首页请用硬件描述语言vhdl设计一个原码二位乘法器,其中两个操作数位宽为8。

请用硬件描述语言vhdl设计一个原码二位乘法器,其中两个操作数位宽为8。

时间: 2024-05-16 17:13:49 浏览: 141

以下是一个简单的vhdl代码实现原码二位乘法器,其中乘法器的输入和输出都是8位。

```

library ieee;

use ieee.std_logic_1164.all;

entity multiplier is

port (a, b : in std_logic_vector(7 downto 0);

p : out std_logic_vector(15 downto 0));

end entity multiplier;

architecture arch of multiplier is

begin

p <= std_logic_vector(unsigned(a) * unsigned(b));

end architecture arch;

```

解释一下代码:

- 首先声明了一个实体entity,它有3个端口,其中a和b是输入,p是输出。

- 在体内,使用了一个简单的乘法实现,将a和b转换为unsigned类型进行乘法运算,然后再将结果转换为std_logic_vector类型输出到p端口。

需要注意的是,这个实现中没有考虑溢出情况。如果需要考虑溢出,可以在体内添加一些逻辑判断。

阅读全文

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

大家在看

yolo开发人工智能小程序经验和总结.zip

yolo开发人工智能小程序经验和总结.zipyolo开发人工智能小程序经验和总结.zipyolo开发人工智能小程序经验和总结.zipyolo开发人工智能小程序经验和总结.zip

USB_HUB硬件电路引脚原理解析.docx

USB_HUB硬件电路引脚原理解析,与个人博文一致,这是word版本。

USB_HUB硬件电路引脚原理解析,与个人博文一致,这是word版本。

Keysight N6705C直流电源分析仪.pdf

Keysight N6705C直流电源分析仪

AS400 自学笔记集锦

AS400 自学笔记集锦

AS400学习笔记(V1.2)

自学使用的400操作命令集锦

LQR与PD控制在柔性机械臂中的对比研究

LQR与PD控制在柔性机械臂中的对比研究,路恩,杨雪锋,针对单杆柔性机械臂末端位置控制的问题,本文对柔性机械臂振动主动控制中较为常见的LQR和PD方法进行了控制效果的对比研究。首先,�

最新推荐

4位乘法器vhdl程序

4位乘法器是数字电路设计中的一个基本组件,它能将两个4位二进制数相乘,生成一个7位的结果。在VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)中,我们可以编写程序来描述这个逻辑功能...

8*8乘法器的VHDL源代码(二种方法)

标题中的“8*8乘法器的VHDL源代码(二种方法)”指的是使用VHDL编程语言实现的8位乘8位无符号乘法器的两种不同设计方案。这两种方法分别是基于LPM_MULT(逻辑乘法宏)模块的自定义乘法器和采用横向进位、迭代求和的...

原码一位乘法器——组成原理课程设计

原码一位乘法器是计算机组成原理课程设计的重要组成部分,它们之间的相乘结果的符号为相乘两数符号的异或值,而数值则为两数绝对值之积。本文将讲解原码一位乘法器的设计原理和实现方法。 原码一位乘法器的设计原理...

课程设计报告——用硬件描述语言设计浮点乘法器(原码一位乘法)

本课程设计报告详细阐述了如何利用硬件描述语言来设计一个浮点乘法器,特别关注原码一位乘法的实现方法。 一、浮点乘法器概述 浮点数表示法是计算机科学中处理大范围数值的一种方式,它由三部分组成:符号位、指数...

超前进位4位加法器74LS283的VHDL程序实现

为了解决这个问题,超前进位加法器的设计允许每位的和直接由加数和被加数计算得出,无需等待低位的进位,因此大大提升了运算速度。 在本文中,我们将探讨一种具体的超前进位加法器——4位加法器74LS283的VHDL程序...

HTML挑战:30天技术学习之旅

资源摘要信息: "desafio-30dias"

标题 "desafio-30dias" 暗示这可能是一个与挑战或训练相关的项目,这在编程和学习新技能的上下文中相当常见。标题中的数字“30”很可能表明这个挑战涉及为期30天的时间框架。此外,由于标题是西班牙语,我们可以推测这个项目可能起源于或至少是针对西班牙语使用者的社区。标题本身没有透露技术上的具体内容,但挑战通常涉及一系列任务,旨在提升个人的某项技能或知识水平。

描述 "desafio-30dias" 并没有提供进一步的信息,它重复了标题的内容。因此,我们不能从中获得关于项目具体细节的额外信息。描述通常用于详细说明项目的性质、目标和期望成果,但由于这里没有具体描述,我们只能依靠标题和相关标签进行推测。

标签 "HTML" 表明这个挑战很可能与HTML(超文本标记语言)有关。HTML是构成网页和网页应用基础的标记语言,用于创建和定义内容的结构、格式和语义。由于标签指定了HTML,我们可以合理假设这个30天挑战的目的是学习或提升HTML技能。它可能包含创建网页、实现网页设计、理解HTML5的新特性等方面的任务。

压缩包子文件的文件名称列表 "desafio-30dias-master" 指向了一个可能包含挑战相关材料的压缩文件。文件名中的“master”表明这可能是一个主文件或包含最终版本材料的文件夹。通常,在版本控制系统如Git中,“master”分支代表项目的主分支,用于存放项目的稳定版本。考虑到这个文件名称的格式,它可能是一个包含所有相关文件和资源的ZIP或RAR压缩文件。

结合这些信息,我们可以推测,这个30天挑战可能涉及了一系列的编程任务和练习,旨在通过实践项目来提高对HTML的理解和应用能力。这些任务可能包括设计和开发静态和动态网页,学习如何使用HTML5增强网页的功能和用户体验,以及如何将HTML与CSS(层叠样式表)和JavaScript等其他技术结合,制作出丰富的交互式网站。

综上所述,这个项目可能是一个为期30天的HTML学习计划,设计给希望提升前端开发能力的开发者,尤其是那些对HTML基础和最新标准感兴趣的人。挑战可能包含了理论学习和实践练习,鼓励参与者通过构建实际项目来学习和巩固知识点。通过这样的学习过程,参与者可以提高在现代网页开发环境中的竞争力,为创建更加复杂和引人入胜的网页打下坚实的基础。

【CodeBlocks精通指南】:一步到位安装wxWidgets库(新手必备)

# 摘要

本文旨在为使用CodeBlocks和wxWidgets库的开发者提供详细的安装、配置、实践操作指南和性能优化建议。文章首先介绍了CodeBlocks和wxWidgets库的基本概念和安装流程,然后深入探讨了CodeBlocks的高级功能定制和wxWidgets的架构特性。随后,通过实践操作章节,指导读者如何创建和运行一个wxWidgets项目,包括界面设计、事件

andorid studio 配置ERROR: Cause: unable to find valid certification path to requested target

### 解决 Android Studio SSL 证书验证问题

当遇到 `unable to find valid certification path` 错误时,这通常意味着 Java 运行环境无法识别服务器提供的 SSL 证书。解决方案涉及更新本地的信任库或调整项目中的网络请求设置。

#### 方法一:安装自定义 CA 证书到 JDK 中

对于企业内部使用的私有 CA 颁发的证书,可以将其导入至 JRE 的信任库中:

1. 获取 `.crt` 或者 `.cer` 文件形式的企业根证书;

2. 使用命令行工具 keytool 将其加入 cacerts 文件内:

```

VC++实现文件顺序读写操作的技巧与实践

资源摘要信息:"vc++文件的顺序读写操作"

在计算机编程中,文件的顺序读写操作是最基础的操作之一,尤其在使用C++语言进行开发时,了解和掌握文件的顺序读写操作是十分重要的。在Microsoft的Visual C++(简称VC++)开发环境中,可以通过标准库中的文件操作函数来实现顺序读写功能。

### 文件顺序读写基础

顺序读写指的是从文件的开始处逐个读取或写入数据,直到文件结束。这与随机读写不同,后者可以任意位置读取或写入数据。顺序读写操作通常用于处理日志文件、文本文件等不需要频繁随机访问的文件。

### VC++中的文件流类

在VC++中,顺序读写操作主要使用的是C++标准库中的fstream类,包括ifstream(用于从文件中读取数据)和ofstream(用于向文件写入数据)两个类。这两个类都是从fstream类继承而来,提供了基本的文件操作功能。

### 实现文件顺序读写操作的步骤

1. **包含必要的头文件**:要进行文件操作,首先需要包含fstream头文件。

```cpp

#include <fstream>

```

2. **创建文件流对象**:创建ifstream或ofstream对象,用于打开文件。

```cpp

ifstream inFile("example.txt"); // 用于读操作

ofstream outFile("example.txt"); // 用于写操作

```

3. **打开文件**:使用文件流对象的成员函数open()来打开文件。如果不需要在创建对象时指定文件路径,也可以在对象创建后调用open()。

```cpp

inFile.open("example.txt", std::ios::in); // 以读模式打开

outFile.open("example.txt", std::ios::out); // 以写模式打开

```

4. **读写数据**:使用文件流对象的成员函数进行数据的读取或写入。对于读操作,可以使用 >> 运算符、get()、read()等方法;对于写操作,可以使用 << 运算符、write()等方法。

```cpp

// 读取操作示例

char c;

while (inFile >> c) {

// 处理读取的数据c

}

// 写入操作示例

const char *text = "Hello, World!";

outFile << text;

```

5. **关闭文件**:操作完成后,应关闭文件,释放资源。

```cpp

inFile.close();

outFile.close();

```

### 文件顺序读写的注意事项

- 在进行文件读写之前,需要确保文件确实存在,且程序有足够的权限对文件进行读写操作。

- 使用文件流进行读写时,应注意文件流的错误状态。例如,在读取完文件后,应检查文件流是否到达文件末尾(failbit)。

- 在写入文件时,如果目标文件不存在,某些open()操作会自动创建文件。如果文件已存在,open()操作则会清空原文件内容,除非使用了追加模式(std::ios::app)。

- 对于大文件的读写,应考虑内存使用情况,避免一次性读取过多数据导致内存溢出。

- 在程序结束前,应该关闭所有打开的文件流。虽然文件流对象的析构函数会自动关闭文件,但显式调用close()是一个好习惯。

### 常用的文件操作函数

- `open()`:打开文件。

- `close()`:关闭文件。

- `read()`:从文件读取数据到缓冲区。

- `write()`:向文件写入数据。

- `tellg()` 和 `tellp()`:分别返回当前读取位置和写入位置。

- `seekg()` 和 `seekp()`:设置文件流的位置。

### 总结

在VC++中实现顺序读写操作,是进行文件处理和数据持久化的基础。通过使用C++的标准库中的fstream类,我们可以方便地进行文件读写操作。掌握文件顺序读写不仅可以帮助我们在实际开发中处理数据文件,还可以加深我们对C++语言和文件I/O操作的理解。需要注意的是,在进行文件操作时,合理管理和异常处理是非常重要的,这有助于确保程序的健壮性和数据的安全。

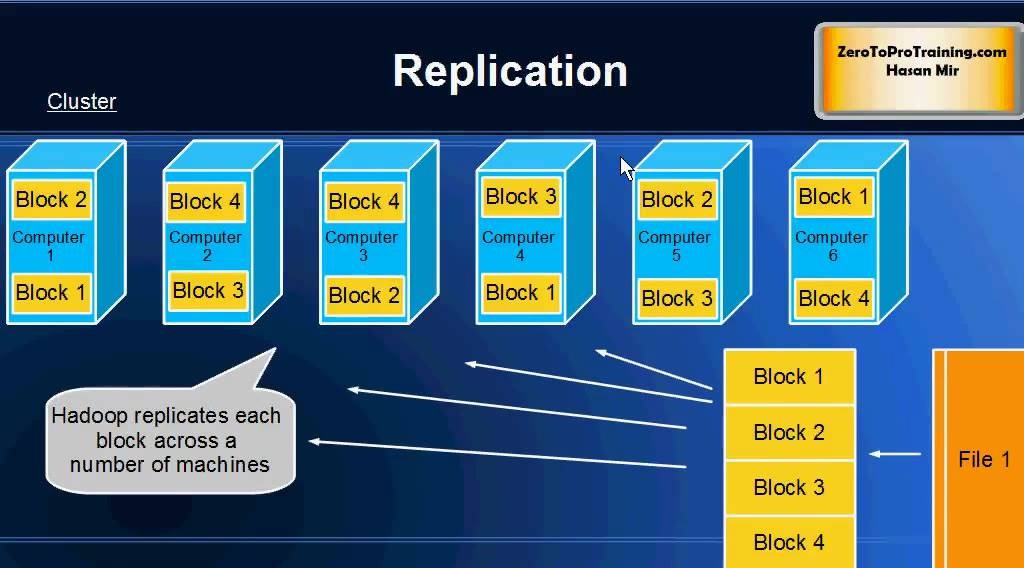

【大数据时代必备:Hadoop框架深度解析】:掌握核心组件,开启数据科学之旅

# 摘要

Hadoop作为一个开源的分布式存储和计算框架,在大数据处理领域发挥着举足轻重的作用。本文首先对Hadoop进行了概述,并介绍了其生态系统中的核心组件。深入分