首页

verdi 逻辑运算

verdi 逻辑运算

时间: 2023-08-08 10:09:04

浏览: 157

Verilog 是一种硬件描述语言(HDL),用于在数字电路和系统级设计中描述逻辑运算。Verilog 中的逻辑运算主要包括与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等。这些逻辑运算可以通过 Verilog 的逻辑门表示,也可以通过逻辑运算符进行表示。在 Verilog 中,逻辑运算可以用于设计各种数字电路,例如加法器、乘法器、比较器等。

阅读全文

相关推荐

逻辑运算符

逻辑运算符

Verdi and Siloti Command Reference

Verdi和Siloti命令参考指南 Verdi是一款强大的IC验证工具,主要针对fsdb模型进行操作,这是Synopsys公司的Verification ContinuumTM平台的一部分。fsdb文件是VCD(Value Change Dump)文件的一种压缩和优化版本,...

verdi用法小结转载自芯片验证日记

- 创建新信号:通过逻辑运算创建新的观察信号。 - 添加 marker:标记特定时间点,便于后续分析。 - 总线操作:处理并行数据总线,查看和分析多个信号作为一个整体。 四、高级功能 除了基础用法外,Verdi 还提供...

verilog语言实现浮点数运算,正确程序代码+仿真

1. **源代码**:Verilog代码文件,可能包括了浮点数运算单元(如加法器、乘法器等)、流水线控制逻辑以及输入/输出接口。代码可能使用模块化结构,每个模块负责特定的计算或控制功能。 2. **仿真设置**:这部分可能...

巴塞隆纳超级运算中心建置全球首款ARM架构CPU/GPU混合型超级计算机.pdf

VERDI通过自动化处理复杂SoC的工作原理,减少了半以上的侦错时间,并通过其独特的分析引擎和专利技术,提高了设计可视化和因果关系分析的能力,有助于实现更高水平的验证效能。 总的来说,这篇文章揭示了ARM架构在...

数字集成电路仿真验证:Makefile与VCS/Verdi实战教程

4. **加法器模块**:设计者展示了8位加法器(adder8.v)的Verilog代码,该模块接受两个8位输入(a_i和b_i),通过always块实现了在时钟上升沿更新的加法运算,输出一个9位的和(c_o)。这个模块是测试的目标,也是实际...

【Verdi系统新手必读】:5个步骤快速入门与精通

# 摘要 MVC标准化是肌电信号处理中确保数据质量的重要步骤,它对于提高测量结果的准确性和可重复性至关重要。本文首先介绍肌电信号的生理学原理和MVC标准化理论,阐述了数据质量的重要性及影响因素。随后,文章深入探讨了肌电信号预处理的各个环节,包括噪声识别与消除、信号放大与滤波技术、以及基线漂移的校正方法。在提升数据质量的关键步骤部分,本文详细描述了信号特征提取、MVC标准化的实施与评估,并讨论了数据质量评估与优化工具。最后,本文通过实验设计和案例分析,展示了MVC标准化在实践应用中的具

能否提供一个在R语言中执行Framingham数据集判别分析的详细和完整的代码示例?

当然可以。在R语言中,Framingham数据集是一个用于心血管疾病研究的经典数据集。以下是使用`ggfortify`包结合` factoextra`包进行判别分析的一个基本步骤: 首先,你需要安装所需的库,如果尚未安装,可以使用以下命令: ```r install.packages(c("ggfortify", "factoextra")) ``` 然后加载所需的数据集并做预处理。Framingham数据集通常存储在`MASS`包中,你可以通过下面的代码加载: ```r library(MASS) data(Framingham) ``` 接下来,我们假设你已经对数据进行了适当的清洗和转换

Blaseball Plus插件开发与构建教程

资源摘要信息:"Blaseball Plus" Blaseball Plus是一个与游戏Blaseball相关的扩展项目,该项目提供了一系列扩展和改进功能,以增强Blaseball游戏体验。在这个项目中,JavaScript被用作主要开发语言,通过在package.json文件中定义的脚本来完成构建任务。项目说明中提到了开发环境的要求,即在20.09版本上进行开发,并且提供了一个flake.nix文件来复制确切的构建环境。虽然Nix薄片是一项处于工作状态(WIP)的功能且尚未完全记录,但可能需要用户自行安装系统依赖项,其中列出了Node.js和纱(Yarn)的特定版本。 ### 知识点详细说明: #### 1. Blaseball游戏: Blaseball是一个虚构的棒球游戏,它在互联网社区中流行,其特点是独特的规则、随机事件和社区参与的元素。 #### 2. 扩展开发: Blaseball Plus是一个扩展,它可能是为在浏览器中运行的Blaseball游戏提供额外功能和改进的软件。扩展开发通常涉及编写额外的代码来增强现有软件的功能。 #### 3. JavaScript编程语言: JavaScript是一种高级的、解释执行的编程语言,被广泛用于网页和Web应用的客户端脚本编写,是开发Web扩展的关键技术之一。 #### 4. package.json文件: 这是Node.js项目的核心配置文件,用于声明项目的各种配置选项,包括项目名称、版本、依赖关系以及脚本命令等。 #### 5.构建脚本: 描述中提到的脚本,如`build:dev`、`build:prod:unsigned`和`build:prod:signed`,这些脚本用于自动化构建过程,可能包括编译、打包、签名等步骤。`yarn run`命令用于执行这些脚本。 #### 6. yarn包管理器: Yarn是一个快速、可靠和安全的依赖项管理工具,类似于npm(Node.js的包管理器)。它允许开发者和项目管理依赖项,通过简单的命令行界面可以轻松地安装和更新包。 #### 7. Node.js版本管理: 项目要求Node.js的具体版本,这里是14.9.0版本。管理特定的Node.js版本是重要的,因为在不同版本间可能会存在API变化或其他不兼容问题,这可能会影响扩展的构建和运行。 #### 8. 系统依赖项的安装: 文档提到可能需要用户手动安装系统依赖项,这在使用Nix薄片时尤其常见。Nix薄片(Nix flakes)是一个实验性的Nix特性,用于提供可复现的开发环境和构建设置。 #### 9. Web扩展的工件放置: 构建后的工件放置在`addon/web-ext-artifacts/`目录中,表明这可能是一个基于WebExtension的扩展项目。WebExtension是一种跨浏览器的扩展API,用于创建浏览器扩展。 #### 10. 扩展部署: 描述中提到了两种不同类型的构建版本:开发版(dev)和生产版(prod),其中生产版又分为未签名(unsigned)和已签名(signed)版本。这些不同的构建版本用于不同阶段的开发和发布。 通过这份文档,我们能够了解到Blaseball Plus项目的开发环境配置、构建脚本的使用、依赖管理工具的运用以及Web扩展的基本概念和部署流程。这些知识点对于理解JavaScript项目开发和扩展构建具有重要意义。

"互动学习:行动中的多样性与论文攻读经历"

多样性她- 事实上SCI NCES你的时间表ECOLEDO C Tora SC和NCESPOUR l’Ingén学习互动,互动学习以行动为中心的强化学习学会互动,互动学习,以行动为中心的强化学习计算机科学博士论文于2021年9月28日在Villeneuve d'Asq公开支持马修·瑟林评审团主席法布里斯·勒菲弗尔阿维尼翁大学教授论文指导奥利维尔·皮耶昆谷歌研究教授:智囊团论文联合主任菲利普·普雷教授,大学。里尔/CRISTAL/因里亚报告员奥利维耶·西格德索邦大学报告员卢多维奇·德诺耶教授,Facebook /索邦大学审查员越南圣迈IMT Atlantic高级讲师邀请弗洛里安·斯特鲁布博士,Deepmind对于那些及时看到自己错误的人...3谢谢你首先,我要感谢我的两位博士生导师Olivier和Philippe。奥利维尔,"站在巨人的肩膀上"这句话对你来说完全有意义了。从科学上讲,你知道在这篇论文的(许多)错误中,你是我可以依

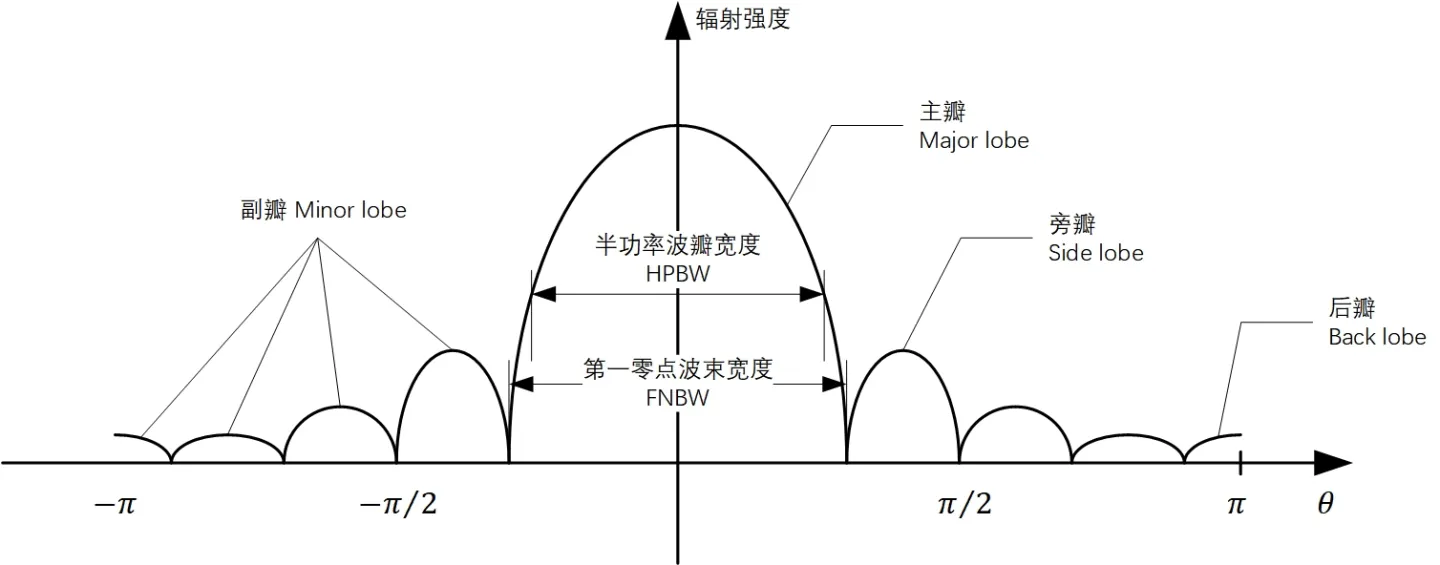

【天线性能提升密籍】:深入探究均匀线阵方向图设计原则及案例分析

# 摘要 本文深入探讨了均匀线阵天线的基础理论及其方向图设计,旨在提升天线系统的性能和应用效能。文章首先介绍了均匀线阵及方向图的基本概念,并阐述了方向图设计的理论基础,包括波束形成与主瓣及副瓣特性的控制。随后,论文通过设计软件工具的应用和实际天线系统调试方法,展示了方向图设计的实践技巧。文中还包含了一系列案例分析,以实证研究验证理论,并探讨了均匀线阵性能

C#怎么把图片存入名为当前日期的文件夹里

在C#中,你可以通过`System.IO`命名空间下的`Directory`和`File`类来创建并存储图片到包含当前日期的文件夹里。以下是一个简单的示例: ```csharp using System; using System.IO; public void SaveImageToTodayFolder(string imagePath, string imageName) { // 获取当前日期 DateTime currentDate = DateTime.Now; string folderPath = Path.Combine(Environment.C

Deno Express:模仿Node.js Express的Deno Web服务器解决方案

资源摘要信息:"deno-express:该项目的灵感来自https" 知识点: 1. Deno 介绍:Deno 是一个简单、现代且安全的JavaScript和TypeScript运行时,由Node.js的原作者Ryan Dahl开发。它内置了诸如TypeScript支持、依赖模块的自动加载等功能。Deno的出现是为了解决Node.js存在的一些问题,比如全局状态污染和包管理等。 2. Express.js 概念:Express.js 是一个基于Node.js平台的极简、灵活的web应用开发框架。它提供了一系列强大的功能,用于开发单页、多页和混合web应用。Express.js的亮点在于其路由系统,对中间件的使用,以及对视图引擎的支持。 3. deno-express 项目:该项目以Node.js的Express框架为灵感,为Deno提供了一套类似于Express的Web服务器搭建方式。使用deno-express可以让开发者用熟悉的Express API在Deno环境中快速构建Web应用。 4. TypeScript 使用:TypeScript 是 JavaScript 的一个超集,添加了类型系统和对ES6+的新特性的支持。它最终会被编译成纯JavaScript代码,以便在浏览器和Node.js等JavaScript环境中运行。在deno-express项目中,通过TypeScript编写代码,不仅可以享受到静态类型检查的好处,还可以利用TypeScript的强类型系统来构建更稳定、易于维护的代码。 5. 代码示例解析:在描述中提供了一个简短的代码示例,示范了如何使用deno-express构建一个简单的web server。 - `import * as expressive from "https://raw.githubusercontent.com/NMathar/deno-express/master/mod.ts";` 这行代码通过网络导入了deno-express库的核心模块。 - `const port = 3000;` 定义了一个端口号,即web服务器将监听的端口。 - `const app = new expressive.App();` 创建了一个Express-like的App实例。 - `app.use(expressive.simpleLog());` 使用了一个简单的日志中间件,这可能会记录请求和响应的信息。 - `app.use(expressive.static_("./public"));` 使用了静态文件服务中间件,指定 "./public" 作为静态文件目录,使得该目录下的文件可以被Web服务访问。 - `app.use(expressive.bodyParser.json());` 使用了body-parser中间件,它能解析请求体中的JSON格式数据,使得在后续的请求处理中可以方便地获取这些数据。 6. Deno 与 Node.js 的对比:Deno与Node.js在设计哲学和实现上有明显差异。Deno不使用npm作为包管理器,而是通过URL导入模块。它也具备内置的TLS和网络测试工具,以及自动的依赖项管理,这都是Node.js需要外部模块来实现的功能。 7. 代码示例中的未显示部分:描述中仅展示了server.ts文件的部分内容,根据标准的Express应用结构,可能还会包括定义路由、设置视图引擎、错误处理中间件等。 8. 模块和库的使用:在deno-express项目中,开发者会接触到如何在Deno环境下使用外部模块。在JavaScript和TypeScript社区中,通过URL直接导入模块是一个新颖的方法,它使得依赖关系变得清晰,并且有助于构建安全、无包管理器污染的应用。 9. 对于TypeScript的依赖:由于deno-express项目的代码示例是用TypeScript编写的,所以它展示了TypeScript在Deno项目中如何使用。Deno对TypeScript的支持是原生的,无需额外编译器,直接运行即可。 10. Web服务器搭建实践:通过这个项目,开发者可以学习如何在Deno中搭建和管理Web服务器,包括如何处理路由、如何对请求和响应进行中间件处理等Web开发基础知识点。 通过对以上知识点的了解,可以对deno-express项目有一个全面的认识。该项目不仅为Deno提供了类似Express.js的Web开发体验,还展示了如何利用TypeScript来构建现代化、高性能的Web应用。