首页assign button_flag_en = (~flag_reg2) & flag_reg1; assign uart_flag = (~recv_done_d1) & recv_done_d0; assign motor_en = (digit == digit_set);

assign button_flag_en = (~flag_reg2) & flag_reg1; assign uart_flag = (~recv_done_d1) & recv_done_d0; assign motor_en = (digit == digit_set);

时间: 2023-09-01 08:13:42 浏览: 74

这是一些Verilog的代码片段,它们是用来实现硬件电路的。我可以为你解释这些代码的含义。

第一行代码 `assign button_flag_en = (~flag_reg2) & flag_reg1;` 中,`~`表示取反,`&`表示按位与运算。这行代码的含义是,如果`flag_reg1`的值为1,且`flag_reg2`的值为0,则`button_flag_en`的值为1,否则为0。

第二行代码 `assign uart_flag = (~recv_done_d1) & recv_done_d0;` 中,`~`表示取反,`&`表示按位与运算。这行代码的含义是,如果`recv_done_d0`的值为1,且`recv_done_d1`的值为0,则`uart_flag`的值为1,否则为0。

第三行代码 `assign motor_en = (digit == digit_set);` 中,`==`表示相等运算。这行代码的含义是,如果`digit`的值等于`digit_set`的值,则`motor_en`的值为1,否则为0。

这些代码片段看起来都是用来控制电路中的开关或者状态变量的。

阅读全文

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

最新推荐

pandas-1.3.5-cp37-cp37m-macosx_10_9_x86_64.zip

pandas whl安装包,对应各个python版本和系统(具体看资源名字),找准自己对应的下载即可!

下载后解压出来是已.whl为后缀的安装包,进入终端,直接pip install pandas-xxx.whl即可,非常方便。

再也不用担心pip联网下载网络超时,各种安装不成功的问题。

基于java的大学生兼职信息系统答辩PPT.pptx

基于java的大学生兼职信息系统答辩PPT.pptx

基于java的乐校园二手书交易管理系统答辩PPT.pptx

基于java的乐校园二手书交易管理系统答辩PPT.pptx

tornado-6.4-cp38-abi3-musllinux_1_1_i686.whl

tornado-6.4-cp38-abi3-musllinux_1_1_i686.whl

Android Studio Ladybug(android-studio-2024.2.1.10-mac.zip.002)

Android Studio Ladybug 2024.2.1(android-studio-2024.2.1.10-mac.dmg)适用于macOS Intel系统,文件使用360压缩软件分割成两个压缩包,必须一起下载使用:

part1: https://download.csdn.net/download/weixin_43800734/89954174

part2: https://download.csdn.net/download/weixin_43800734/89954175

Aspose资源包:转PDF无水印学习工具

资源摘要信息:"Aspose.Cells和Aspose.Words是两个非常强大的库,它们属于Aspose.Total产品家族的一部分,主要面向.NET和Java开发者。Aspose.Cells库允许用户轻松地操作Excel电子表格,包括创建、修改、渲染以及转换为不同的文件格式。该库支持从Excel 97-2003的.xls格式到最新***016的.xlsx格式,还可以将Excel文件转换为PDF、HTML、MHTML、TXT、CSV、ODS和多种图像格式。Aspose.Words则是一个用于处理Word文档的类库,能够创建、修改、渲染以及转换Word文档到不同的格式。它支持从较旧的.doc格式到最新.docx格式的转换,还包括将Word文档转换为PDF、HTML、XAML、TIFF等格式。

Aspose.Cells和Aspose.Words都有一个重要的特性,那就是它们提供的输出资源包中没有水印。这意味着,当开发者使用这些资源包进行文档的处理和转换时,最终生成的文档不会有任何水印,这为需要清洁输出文件的用户提供了极大的便利。这一点尤其重要,在处理敏感文档或者需要高质量输出的企业环境中,无水印的输出可以帮助保持品牌形象和文档内容的纯净性。

此外,这些资源包通常会标明仅供学习使用,切勿用作商业用途。这是为了避免违反Aspose的使用协议,因为Aspose的产品虽然是商业性的,但也提供了免费的试用版本,其中可能包含了特定的限制,如在最终输出的文档中添加水印等。因此,开发者在使用这些资源包时应确保遵守相关条款和条件,以免产生法律责任问题。

在实际开发中,开发者可以通过NuGet包管理器安装Aspose.Cells和Aspose.Words,也可以通过Maven在Java项目中进行安装。安装后,开发者可以利用这些库提供的API,根据自己的需求编写代码来实现各种文档处理功能。

对于Aspose.Cells,开发者可以使用它来完成诸如创建电子表格、计算公式、处理图表、设置样式、插入图片、合并单元格以及保护工作表等操作。它也支持读取和写入XML文件,这为处理Excel文件提供了更大的灵活性和兼容性。

而对于Aspose.Words,开发者可以利用它来执行文档格式转换、读写文档元数据、处理文档中的文本、格式化文本样式、操作节、页眉、页脚、页码、表格以及嵌入字体等操作。Aspose.Words还能够灵活地处理文档中的目录和书签,这让它在生成复杂文档结构时显得特别有用。

在使用这些库时,一个常见的场景是在企业应用中,需要将报告或者数据导出为PDF格式,以便于打印或者分发。这时,使用Aspose.Cells和Aspose.Words就可以实现从Excel或Word格式到PDF格式的转换,并且确保输出的文件中不包含水印,这提高了文档的专业性和可信度。

需要注意的是,虽然Aspose的产品提供了很多便利的功能,但它们通常是付费的。用户需要根据自己的需求购买相应的许可证。对于个人用户和开源项目,Aspose有时会提供免费的许可证。而对于商业用途,用户则需要购买商业许可证才能合法使用这些库的所有功能。"

管理建模和仿真的文件

管理Boualem Benatallah引用此版本:布阿利姆·贝纳塔拉。管理建模和仿真。约瑟夫-傅立叶大学-格勒诺布尔第一大学,1996年。法语。NNT:电话:00345357HAL ID:电话:00345357https://theses.hal.science/tel-003453572008年12月9日提交HAL是一个多学科的开放存取档案馆,用于存放和传播科学研究论文,无论它们是否被公开。论文可以来自法国或国外的教学和研究机构,也可以来自公共或私人研究中心。L’archive ouverte pluridisciplinaire

【R语言高性能计算秘诀】:代码优化,提升分析效率的专家级方法

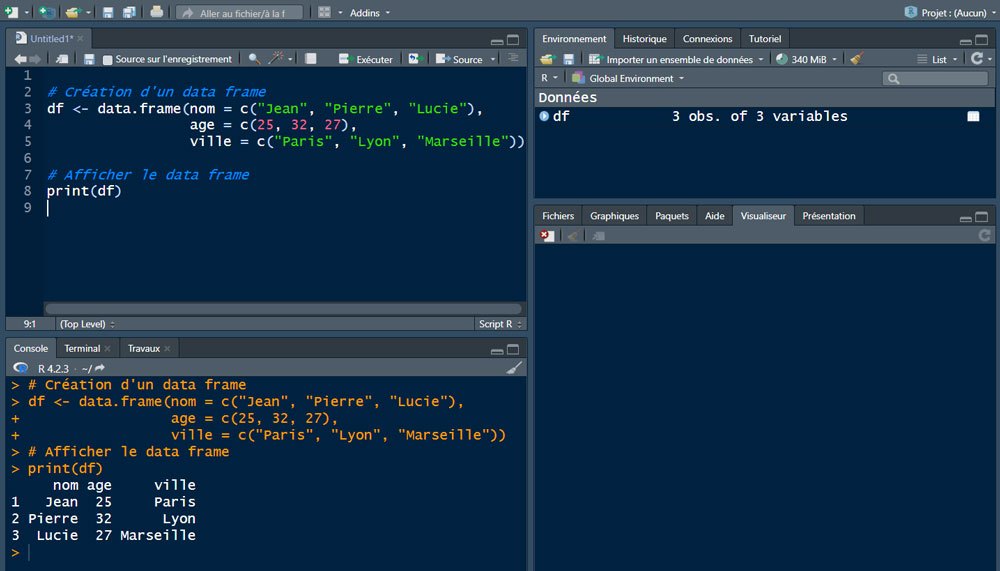

# 1. R语言简介与计算性能概述

R语言作为一种统计编程语言,因其强大的数据处理能力、丰富的统计分析功能以及灵活的图形表示法而受到广泛欢迎。它的设计初衷是为统计分析提供一套完整的工具集,同时其开源的特性让全球的程序员和数据科学家贡献了大量实用的扩展包。由于R语言的向量化操作以及对数据框(data frames)的高效处理,使其在处理大规模数据集时表现出色。

计算性能方面,R语言在单线程环境中表现良好,但与其他语言相比,它的性能在多

在构建视频会议系统时,如何通过H.323协议实现音视频流的高效传输,并确保通信的稳定性?

要通过H.323协议实现音视频流的高效传输并确保通信稳定,首先需要深入了解H.323协议的系统结构及其组成部分。H.323协议包括音视频编码标准、信令控制协议H.225和会话控制协议H.245,以及数据传输协议RTP等。其中,H.245协议负责控制通道的建立和管理,而RTP用于音视频数据的传输。

参考资源链接:[H.323协议详解:从系统结构到通信流程](https://wenku.csdn.net/doc/2jtq7zt3i3?spm=1055.2569.3001.10343)

在构建视频会议系统时,需要合理配置网守(Gatekeeper)来提供地址解析和准入控制,保证通信安全和地址管理

Go语言控制台输入输出操作教程

资源摘要信息:"在Go语言(又称Golang)中,控制台的输入输出是进行基础交互的重要组成部分。Go语言提供了一组丰富的库函数,特别是`fmt`包,来处理控制台的输入输出操作。`fmt`包中的函数能够实现格式化的输入和输出,使得程序员可以轻松地在控制台显示文本信息或者读取用户的输入。"

1. fmt包的使用

Go语言标准库中的`fmt`包提供了许多打印和解析数据的函数。这些函数可以让我们在控制台上输出信息,或者从控制台读取用户的输入。

- 输出信息到控制台

- Print、Println和Printf是基本的输出函数。Print和Println函数可以输出任意类型的数据,而Printf可以进行格式化输出。

- Sprintf函数可以将格式化的字符串保存到变量中,而不是直接输出。

- Fprint系列函数可以将输出写入到`io.Writer`接口类型的变量中,例如文件。

- 从控制台读取信息

- Scan、Scanln和Scanf函数可以读取用户输入的数据。

- Sscan、Sscanln和Sscanf函数则可以从字符串中读取数据。

- Fscan系列函数与上面相对应,但它们是将输入读取到实现了`io.Reader`接口的变量中。

2. 输入输出的格式化

Go语言的格式化输入输出功能非常强大,它提供了类似于C语言的`printf`和`scanf`的格式化字符串。

- Print函数使用格式化占位符

- `%v`表示使用默认格式输出值。

- `%+v`会包含结构体的字段名。

- `%#v`会输出Go语法表示的值。

- `%T`会输出值的数据类型。

- `%t`用于布尔类型。

- `%d`用于十进制整数。

- `%b`用于二进制整数。

- `%c`用于字符(rune)。

- `%x`用于十六进制整数。

- `%f`用于浮点数。

- `%s`用于字符串。

- `%q`用于带双引号的字符串。

- `%%`用于百分号本身。

3. 示例代码分析

在文件main.go中,可能会包含如下代码段,用于演示如何在Go语言中使用fmt包进行基本的输入输出操作。

```go

package main

import "fmt"

func main() {

var name string

fmt.Print("请输入您的名字: ")

fmt.Scanln(&name) // 读取一行输入并存储到name变量中

fmt.Printf("你好, %s!\n", name) // 使用格式化字符串输出信息

}

```

以上代码首先通过`fmt.Print`函数提示用户输入名字,并等待用户从控制台输入信息。然后`fmt.Scanln`函数读取用户输入的一行信息(包括空格),并将其存储在变量`name`中。最后,`fmt.Printf`函数使用格式化字符串输出用户的名字。

4. 代码注释和文档编写

在README.txt文件中,开发者可能会提供关于如何使用main.go代码的说明,这可能包括代码的功能描述、运行方法、依赖关系以及如何处理常见的输入输出场景。这有助于其他开发者理解代码的用途和操作方式。

总之,Go语言为控制台输入输出提供了强大的标准库支持,使得开发者能够方便地处理各种输入输出需求。通过灵活运用fmt包中的各种函数,可以轻松实现程序与用户的交互功能。