首页

linux makefile编写

linux makefile编写

时间: 2023-06-05 13:48:00

浏览: 114

Makefile是一种用于自动化编译程序的工具,它可以根据源代码文件的依赖关系自动编译程序。在Linux系统中,Makefile是非常常见的编译工具,它可以帮助程序员快速、方便地编译程序。Makefile的编写需要掌握一定的语法和规则,包括目标、依赖、命令等。在编写Makefile时,需要考虑到程序的结构、依赖关系和编译选项等因素,以确保程序能够正确编译和运行。

阅读全文

立即开通

100%中奖

相关推荐

Linux Makefile编写:自动化编译与管理的关键

Linux Makefile编写是Linux环境中的关键组件,它在大型项目管理和自动化构建过程中起着至关重要的作用。Makefile是一种特殊的脚本文件,由GNU Make工具解释和执行,用于自动化管理应用程序的编译、链接和安装过程。...

Linux Makefile编写指南:规则、变量与实战

本文档深入探讨了Linux环境下Makefile的编写和使用,这是构建和管理源代码...本篇文档提供了全面的Linux Makefile编写指南,适合开发人员掌握如何创建高效、易维护的构建系统,以便更好地管理和自动化其软件开发流程。

掌握Linux Makefile编写的全面指南

本资源是一份关于Linux GNUMakefile编写的详细指南,适用于对Makefile有一定了解但希望深入学习的人群。GNUMake是一个强大的自动化构建工具,由Richard Stallman、Roland McGrath和Paul Smith等人于1988年开发,版本...

linux Makefile编写

### Linux Makefile 编写详解 #### 实验背景与意义 在Linux环境下,特别是进行大型项目的开发时,Makefile的应用显得尤为重要。对于简单的程序,我们可以直接通过gcc命令来进行编译;但对于复杂的工程项目,手动...

linux Makefile 编写

《深入理解Linux下的Makefile编写》 在Linux环境中,Makefile是项目构建和管理的核心工具之一,它通过定义一系列规则来描述如何从源代码构建可执行文件或库。本文将根据给定的文件内容,详细解析Makefile的关键概念...

linux makefile 编写 规则 编译多个文件

Makefile是Linux开发中的强大工具,通过编写规则,我们可以高效地管理和编译多文件项目。理解并熟练运用Makefile,不仅能够提高开发效率,还能帮助我们更好地理解和控制项目的构建过程。在实际工作中,我们需要...

掌握Linux Makefile编写与管理

这里有字符串处理函数、文件名操作函数等,这些都是Makefile编写中的重要工具。 "跟我一起写Makefile"不仅涵盖了Makefile的基本知识,还提供了丰富的实战案例和深入的理论指导,对于想要掌握Linux下项目构建管理的...

掌握Linux Makefile编写与C程序构建指南

本文档是一篇关于Linux下Makefile编写的详细指南,由陈皓撰写并经祝冬华整理。Makefile是Linux中一个强大的构建工具,用于自动化管理源代码的编译过程。文章分为多个部分,深入讲解了Makefile的基本概念、语法、工作...

掌握Linux Makefile编写:自动化编译神器

"跟我一起写_Makefile"是一篇教程,旨在指导读者在Linux系统下理解和编写Makefile,这是一种重要的构建工具,尤其在软件开发中发挥着核心作用。Makefile主要负责定义和管理软件项目的编译规则,它通过描述源代码文件...

掌握Linux Makefile编写:提升专业编程能力

在Windows环境下,IDE通常会自动处理这些编译细节,但在Linux或Unix环境中,为了实现真正的自动化和标准化,理解并编写Makefile变得至关重要。Makefile的实质是一种文本文件,它包含了针对特定目标(如可执行文件)...

掌握Linux Makefile编写:自动化编译利器

本文将深入探讨"跟我一起写Makefile"的主题,主要针对Linux环境下的Makefile编写和使用。Makefile在Linux编程中扮演着至关重要的角色,特别是在大型软件项目中,它是一种自动化编译工具,用于管理源代码文件之间的...

掌握Linux Makefile编写:自动化编译的基石

本文是一篇关于Linux Makefile编写的教程,由陈皓(CSDN)撰写,旨在帮助Windows程序员理解并掌握Makefile在Unix/Linux软件开发中的重要性。Makefile是一种在Unix/Linux系统中用于自动化构建过程的关键文件,它定义...

掌握Linux Makefile编写与自动化工具的应用

掌握Makefile的编写和使用对于Linux开发者至关重要,因为它在项目管理和构建流程中扮演了核心角色。无论是大型开源项目如MySQL、Apache,还是Linux内核,Makefile都是不可或缺的工具。随着自动化和持续集成/持续部署...

Linux Makefile编写指南:自动化编译与管理

本文将深入探讨Makefile文件在Linux下的编写原理、用途以及创建规则。 首先,Makefile的主要功能是根据指定的目标(target)自动执行一系列预定义的操作(recipe),以达到特定的构建需求。在Linux项目中,例如一个...

掌握Linux Makefile编写:从入门到高级实践

本文档主要介绍了如何在Linux环境下编写和使用Makefile,这是一种在软件开发中非常重要的配置文件,特别是在构建、管理和自动化编译过程中。Makefile通常用于自动化构建过程,尤其是在没有集成开发环境(IDE)支持的...

掌握Linux Makefile编写:自动化编译入门指南

本文将详细介绍Linux Makefile的编写规则,帮助读者快速理解和掌握这一关键的...Makefile是Unix/Linux世界中不可或缺的一部分,对于想要提升编程技能和工程管理能力的开发者来说,深入研究和实践Makefile编写至关重要。

掌握Linux Makefile编写指南:自动化编译利器

本文档主要介绍了Makefile的基本概念和在Linux下C编程中的重要性,特别是对于希望成为专业程序员的人来说,掌握Makefile编写能力的重要性。Makefile是一种用于自动化构建过程的配置文件,它定义了源代码文件之间的...

Linux Makefile编写指南:从基础到高级应用

在Linux环境下,Makefile...Makefile文件在Linux环境下的编写涉及对不同编译器、平台、依赖关系的处理,以及与IDE的有效集成。理解并熟练掌握Makefile的编写原则和技巧,是提高软件开发效率和项目管理能力的重要一环。

掌握Linux Makefile编写教程:构建大型工程的关键

本文档是一份全面的中文教程,详细介绍Linux下的Makefile编写。Makefile是Unix/Linux环境中用于自动化构建和管理项目的文本文件,尤其在软件开发中扮演着至关重要的角色。作者陈皓从基础入门到深入解析,引导读者...

掌握Linux Makefile编写:自动化编译提升开发效率

本文将详细介绍如何在Linux环境下编写Makefile,特别是在C/C++软件开发中不可或缺的自动化构建工具。Makefile,作为编译规则的基石,对于一个专业程序员而言,理解其工作原理和编写技巧至关重要。它定义了工程中的源...

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

海量

VIP免费资源

千本

正版电子书

商城

会员专享价

千门

课程&专栏

全年可省5,000元

立即开通

全年可省5,000元

立即开通

大家在看

FineBI Windows版本安装手册

非常详细 一定安装成功

surfer教程

surfer基础教程基础教程,难得精品,很好的哦,赶紧下载啊。

FastReport5 for D7

FastReport5 for D7

DeepRLPID-main.zip

DDPG调节PID参数

MOOC工程伦理课后习题答案(主观+判断+选择)期末考试答案.docx

MOOC工程伦理课程,课程讲义以及课后选择题、判断题和主观题习题答案

最新推荐

synopsis_VCS_makefile编写.docx

SYNOPSYS VCS Makefile 文件是用于自动化Verilog或SystemVerilog设计的仿真过程的脚本,由Synopsys公司提供。...在编写自己的脚本时,务必考虑Makefile的这些核心特性,以确保能够实现相同的功能和流程控制。

LINUX2.6内核makefile详解

"LINUX2.6内核makefile详解" Linux 2.6 内核 Makefile 详解是 Linux 内核开发中非常重要的一部分。Makefile 是一个脚本文件,用于描述如何编译和构建 Linux 内核。该文件是 Linux 内核开发的核心组件之一,对开发...

Linux下Makefile自动生成工具详解

总结起来,Linux下的Makefile自动生成工具autotools简化了构建过程,使开发者能够专注于编写代码,而不用过多关心构建系统的细节。对于初学者来说,理解这个工具链的工作原理和使用方法是至关重要的,因为它能帮助...

基于STM32单片机的激光雕刻机控制系统设计-含详细步骤和代码

内容概要:本文详细介绍了基于STM32单片机的激光雕刻机控制系统的设计。系统包括硬件设计、软件设计和机械结构设计,主要功能有可调节激光功率大小、改变雕刻速率、手动定位、精确雕刻及切割。硬件部分包括STM32最小系统、步进电机驱动模块、激光发生器控制电路、人机交互电路和串口通信电路。软件部分涉及STM32CubeMX配置、G代码解析、步进电机控制、激光功率调节和手动定位功能的实现。 适合人群:对嵌入式系统和激光雕刻机感兴趣的工程师和技术人员。 使用场景及目标:① 适用于需要高精度激光雕刻的应用场合;② 为开发类似的激光雕刻控制系统提供设计参考。 阅读建议:本文提供了详细的硬件和软件设计方案,读者应结合实际应用场景进行理解,重点关注电路设计和代码实现。

掌握HTML/CSS/JS和Node.js的Web应用开发实践

资源摘要信息:"本资源摘要信息旨在详细介绍和解释提供的文件中提及的关键知识点,特别是与Web应用程序开发相关的技术和概念。" 知识点一:两层Web应用程序架构 两层Web应用程序架构通常指的是客户端-服务器架构中的一个简化版本,其中用户界面(UI)和应用程序逻辑位于客户端,而数据存储和业务逻辑位于服务器端。在这种架构中,客户端(通常是一个Web浏览器)通过HTTP请求与服务器端进行通信。服务器端处理请求并返回数据或响应,而客户端负责展示这些信息给用户。 知识点二:HTML/CSS/JavaScript技术栈 在Web开发中,HTML、CSS和JavaScript是构建前端用户界面的核心技术。HTML(超文本标记语言)用于定义网页的结构和内容,CSS(层叠样式表)负责网页的样式和布局,而JavaScript用于实现网页的动态功能和交互性。 知识点三:Node.js技术 Node.js是一个基于Chrome V8引擎的JavaScript运行时环境,它允许开发者使用JavaScript来编写服务器端代码。Node.js是非阻塞的、事件驱动的I/O模型,适合构建高性能和高并发的网络应用。它广泛用于Web应用的后端开发,尤其适合于I/O密集型应用,如在线聊天应用、实时推送服务等。 知识点四:原型开发 原型开发是一种设计方法,用于快速构建一个可交互的模型或样本来展示和测试产品的主要功能。在软件开发中,原型通常用于评估概念的可行性、收集用户反馈,并用作后续迭代的基础。原型开发可以帮助团队和客户理解产品将如何运作,并尽早发现问题。 知识点五:设计探索 设计探索是指在产品设计过程中,通过创新思维和技术手段来探索各种可能性。在Web应用程序开发中,这可能意味着考虑用户界面设计、用户体验(UX)和用户交互(UI)的创新方法。设计探索的目的是创造一个既实用又吸引人的应用程序,可以提供独特的价值和良好的用户体验。 知识点六:评估可用性和有效性 评估可用性和有效性是指在开发过程中,对应用程序的可用性(用户能否容易地完成任务)和有效性(应用程序是否达到了预定目标)进行检查和测试。这通常涉及用户测试、反馈收集和性能评估,以确保最终产品能够满足用户的需求,并在技术上实现预期的功能。 知识点七:HTML/CSS/JavaScript和Node.js的特定部分使用 在Web应用程序开发中,开发者需要熟练掌握HTML、CSS和JavaScript的基础知识,并了解如何将它们与Node.js结合使用。例如,了解如何使用JavaScript的AJAX技术与服务器端进行异步通信,或者如何利用Node.js的Express框架来创建RESTful API等。 知识点八:应用领域的广泛性 本文件提到的“基准要求”中提到,通过两层Web应用程序可以实现多种应用领域,如游戏、物联网(IoT)、组织工具、商务、媒体等。这说明了Web技术的普适性和灵活性,它们可以被应用于构建各种各样的应用程序,满足不同的业务需求和用户场景。 知识点九:创造性界限 在开发Web应用程序时,鼓励开发者和他们的合作伙伴探索创造性界限。这意味着在确保项目目标和功能要求得以满足的同时,也要勇于尝试新的设计思路、技术方案和用户体验方法,从而创造出新颖且技术上有效的解决方案。 知识点十:参考资料和文件结构 文件名称列表中的“a2-shortstack-master”暗示了这是一个与作业2相关的项目文件夹或代码库。通常,在这样的文件夹结构中,可以找到HTML文件、样式表(CSS文件)、JavaScript脚本以及可能包含Node.js应用的服务器端代码。开发者可以使用这些文件来了解项目结构、代码逻辑和如何将各种技术整合在一起以创建一个完整的工作应用程序。

管理建模和仿真的文件

管理Boualem Benatallah引用此版本:布阿利姆·贝纳塔拉。管理建模和仿真。约瑟夫-傅立叶大学-格勒诺布尔第一大学,1996年。法语。NNT:电话:00345357HAL ID:电话:00345357https://theses.hal.science/tel-003453572008年12月9日提交HAL是一个多学科的开放存取档案馆,用于存放和传播科学研究论文,无论它们是否被公开。论文可以来自法国或国外的教学和研究机构,也可以来自公共或私人研究中心。L’archive ouverte pluridisciplinaire

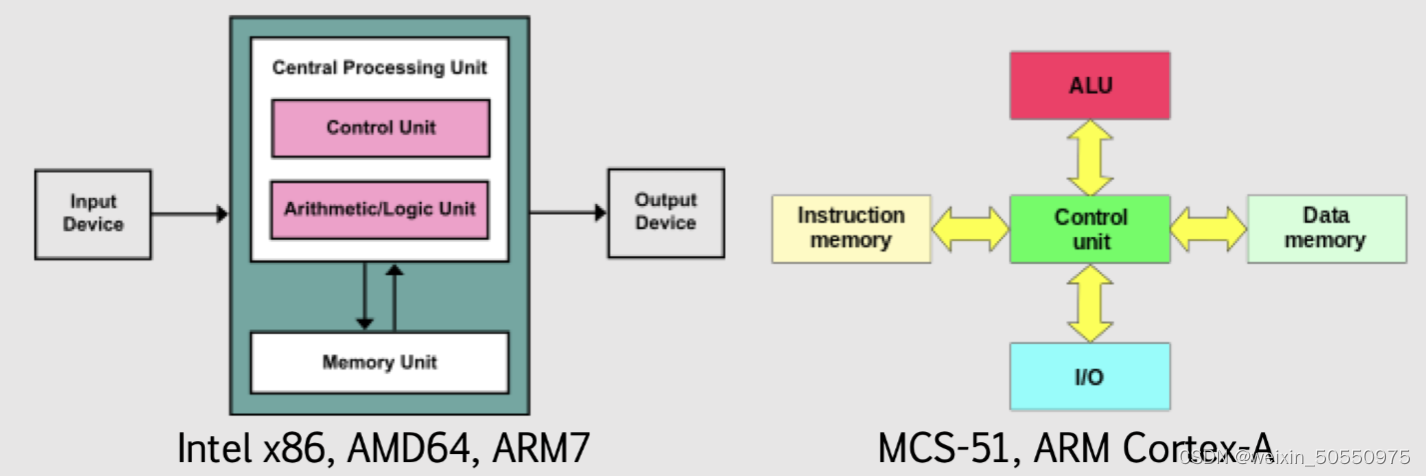

计算机体系结构概述:基础概念与发展趋势

# 摘要 计算机体系结构作为计算机科学的核心领域,经历了从经典模型到现代新发展的演进过程。本文从基本概念出发,详细介绍了冯·诺依曼体系结构、哈佛体系结构以及RISC和CISC体系结构的设计原则和特点。随后,文章探讨了现代计算机体系结构的新发展,包括并行计算体系结构、存储体系结构演进和互连网络的发展。文中还深入分析了前沿技术如量子计算机原理、脑启发式计算以及边缘计算和物联网的结合。最后,文章对计算机体系结构未来的发展趋

int a[][3]={{1,2},{4}}输出这个数组

`int a[][3]={{1,2},{4}}` 定义了一个二维数组,它有两行三列,但是只填充了前两行的数据。第一行是 {1, 2},第二行是 {4}。 当你尝试输出这个数组时,需要注意的是,由于分配的空间是固定的,所以对于只填充了两行的情况,第三列是未初始化的,通常会被默认为0。因此,常规的打印方式会输出类似这样的结果: ``` a[0][0]: 1 a[0][1]: 2 a[1][0]: 4 a[1][1]: (未初始化,可能是0) ``` 如果需要展示所有元素,即使是未初始化的部分,可能会因为语言的不同而有不同的显示方式。例如,在C++或Java中,你可以遍历整个数组来输出: `

勒玛算法研讨会项目:在线商店模拟与Qt界面实现

资源摘要信息: "lerma:算法研讨会项目" 在本节中,我们将深入了解一个名为“lerma:算法研讨会项目”的模拟在线商店项目。该项目涉及多个C++和Qt框架的知识点,包括图形用户界面(GUI)的构建、用户认证、数据存储以及正则表达式的应用。以下是项目中出现的关键知识点和概念。 标题解析: - lerma: 看似是一个项目或产品的名称,作为算法研讨会的一部分,这个名字可能是项目创建者或组织者的名字,用于标识项目本身。 - 算法研讨会项目: 指示本项目是一个在算法研究会议或研讨会上呈现的项目,可能是为了教学、展示或研究目的。 描述解析: - 模拟在线商店项目: 项目旨在创建一个在线商店的模拟环境,这涉及到商品展示、购物车、订单处理等常见在线购物功能的模拟实现。 - Qt安装: 项目使用Qt框架进行开发,Qt是一个跨平台的应用程序和用户界面框架,所以第一步是安装和设置Qt开发环境。 - 阶段1: 描述了项目开发的第一阶段,包括使用Qt创建GUI组件和实现用户登录、注册功能。 - 图形组件简介: 对GUI组件的基本介绍,包括QMainWindow、QStackedWidget等。 - QStackedWidget: 用于在多个页面或视图之间切换的组件,类似于标签页。 - QLineEdit: 提供单行文本输入的控件。 - QPushButton: 按钮控件,用于用户交互。 - 创建主要组件以及登录和注册视图: 涉及如何构建GUI中的主要元素和用户交互界面。 - QVBoxLayout和QHBoxLayout: 分别表示垂直和水平布局,用于组织和排列控件。 - QLabel: 显示静态文本或图片的控件。 - QMessageBox: 显示消息框的控件,用于错误提示、警告或其他提示信息。 - 创建User类并将User类型向量添加到MainWindow: 描述了如何在项目中创建用户类,并在主窗口中实例化用户对象集合。 - 登录和注册功能: 功能实现,包括验证电子邮件、用户名和密码。 - 正则表达式的实现: 使用QRegularExpression类来验证输入字段的格式。 - 第二阶段: 描述了项目开发的第二阶段,涉及数据的读写以及用户数据的唯一性验证。 - 从JSON格式文件读取和写入用户: 描述了如何使用Qt解析和生成JSON数据,JSON是一种轻量级的数据交换格式,易于人阅读和编写,同时也易于机器解析和生成。 - 用户名和电子邮件必须唯一: 在数据库设计时,确保用户名和电子邮件字段的唯一性是常见的数据完整性要求。 - 在允许用户登录或注册之前,用户必须选择代表数据库的文件: 用户在进行登录或注册之前需要指定一个包含用户数据的文件,这可能是项目的一种安全或数据持久化机制。 标签解析: - C++: 标签说明项目使用的编程语言是C++。C++是一种高级编程语言,广泛应用于软件开发领域,特别是在性能要求较高的系统中。 压缩包子文件的文件名称列表: - lerma-main: 这可能是包含项目主要功能或入口点的源代码文件或模块的名称。通常,这样的文件包含应用程序的主要逻辑和界面。 通过这些信息,可以了解到该项目是一个采用Qt框架和C++语言开发的模拟在线商店应用程序,它不仅涉及基础的GUI设计,还包括用户认证、数据存储、数据验证等后端逻辑。这个项目不仅为开发者提供了一个实践Qt和C++的机会,同时也为理解在线商店运行机制提供了一个良好的模拟环境。

"互动学习:行动中的多样性与论文攻读经历"

多样性她- 事实上SCI NCES你的时间表ECOLEDO C Tora SC和NCESPOUR l’Ingén学习互动,互动学习以行动为中心的强化学习学会互动,互动学习,以行动为中心的强化学习计算机科学博士论文于2021年9月28日在Villeneuve d'Asq公开支持马修·瑟林评审团主席法布里斯·勒菲弗尔阿维尼翁大学教授论文指导奥利维尔·皮耶昆谷歌研究教授:智囊团论文联合主任菲利普·普雷教授,大学。里尔/CRISTAL/因里亚报告员奥利维耶·西格德索邦大学报告员卢多维奇·德诺耶教授,Facebook /索邦大学审查员越南圣迈IMT Atlantic高级讲师邀请弗洛里安·斯特鲁布博士,Deepmind对于那些及时看到自己错误的人...3谢谢你首先,我要感谢我的两位博士生导师Olivier和Philippe。奥利维尔,"站在巨人的肩膀上"这句话对你来说完全有意义了。从科学上讲,你知道在这篇论文的(许多)错误中,你是我可以依