首页verilog中循环语句

verilog中循环语句

时间: 2024-06-09 08:11:02 浏览: 120

在Verilog中,有两种常用的循环语句:for循环和forever循环。

for循环的语法如下:

```

for (<initial_condition>; <stop_condition>; <increment>) begin

// 要循环执行的代码

end

```

其中,`<initial_condition>`是循环的初始条件,通常是一个赋值语句用于初始化循环变量;`<stop_condition>`是循环的停止条件,当条件不满足时,循环终止;`<increment>`是每次循环的增量操作,用于更新循环变量的值。

forever循环只能在testbench中使用,它通常用于生成激励时钟信号。forever循环的语法如下:

```

forever begin

// 循环执行的语句

end

```

forever循环会无限循环执行其中的语句,除非遇到了显式的终止条件。

以下是一个示例代码,展示了如何在Verilog中使用for循环和forever循环:

```

for (i = 0; i < 10; i = i + 1) begin

// 循环执行的代码

// 在每次循环中,i的值会递增1

end

forever begin

// 循环执行的语句

// 该循环会无限执行,直到遇到显示的终止条件

end

```

阅读全文

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

大家在看

一种基于STM32的智能交通信号灯设计的研究.rar

一种基于STM32的智能交通信号灯设计的研究.rar

基于Nios II的电子时钟设计

点路设计eda,基于Nios II的电子时钟设计,介绍了设计方法,有代码

福尼斯焊机机器人接口中文说明书

该说明书为福尼斯公司提供的中文版机器人接口说明,主要是配MIG焊机上

Anti-Conent参数算法(700位0aq).zip

zip包内含最新的PDD算法,Anti-Content参数700+位含轨迹算法(之所以含轨迹就是因为稳定)。参数为0aq开头长串,使用与任何700+接口,作者亲测达人端!算法可以直接运行得到Anti-Content参数的值,支持Python及易语言等任意语言调用。购买后有任何问题可以联系作者咨询,作者将随时为你提供必要支持

轮轨接触几何计算程序-Matlab-2024.zip

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。主程序一键自动运行。

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。主程序一键自动运行。

MATLAB实现轮轨接触几何计算(源代码和数据)

数据输入可替换,输出包括等效锥度、接触点对、滚动圆半径差、接触角差等。

运行环境MATLAB2018b。主程序一键自动运行。

最新推荐

租赁合同编写指南及下载资源

资源摘要信息:《租赁合同》是用于明确出租方与承租方之间的权利和义务关系的法律文件。在实际操作中,一份详尽的租赁合同对于保障交易双方的权益至关重要。租赁合同应当包括但不限于以下要点:

1. 双方基本信息:租赁合同中应明确出租方(房东)和承租方(租客)的名称、地址、联系方式等基本信息。这对于日后可能出现的联系、通知或法律诉讼具有重要意义。

2. 房屋信息:合同中需要详细说明所租赁的房屋的具体信息,包括房屋的位置、面积、结构、用途、设备和家具清单等。这些信息有助于双方对租赁物有清晰的认识。

3. 租赁期限:合同应明确租赁开始和结束的日期,以及租期的长短。租赁期限的约定关系到租金的支付和合同的终止条件。

4. 租金和押金:租金条款应包括租金金额、支付周期、支付方式及押金的数额。同时,应明确规定逾期支付租金的处理方式,以及押金的退还条件和时间。

5. 维修与保养:在租赁期间,房屋的维护和保养责任应明确划分。通常情况下,房东负责房屋的结构和主要设施维修,而租客需负责日常维护及保持房屋的清洁。

6. 使用与限制:合同应规定承租方可以如何使用房屋以及可能的限制。例如,禁止非法用途、允许或禁止宠物、是否可以转租等。

7. 终止与续租:租赁合同应包括租赁关系的解除条件,如提前通知时间、违约责任等。同时,双方可以在合同中约定是否可以续租,以及续租的条件。

8. 解决争议的条款:合同中应明确解决可能出现的争议的途径,包括适用法律、管辖法院等,有助于日后纠纷的快速解决。

9. 其他可能需要的条款:根据具体情况,合同中可能还需要包括关于房屋保险、税费承担、合同变更等内容。

下载资源链接:【下载自www.glzy8.com管理资源吧】Rental contract.DOC

该资源为一份租赁合同模板,对需要进行房屋租赁的个人或机构提供了参考价值。通过对合同条款的详细列举和解释,该文档有助于用户了解和制定自己的租赁合同,从而在房屋租赁交易中更好地保护自己的权益。感兴趣的用户可以通过提供的链接下载文档以获得更深入的了解和实际操作指导。

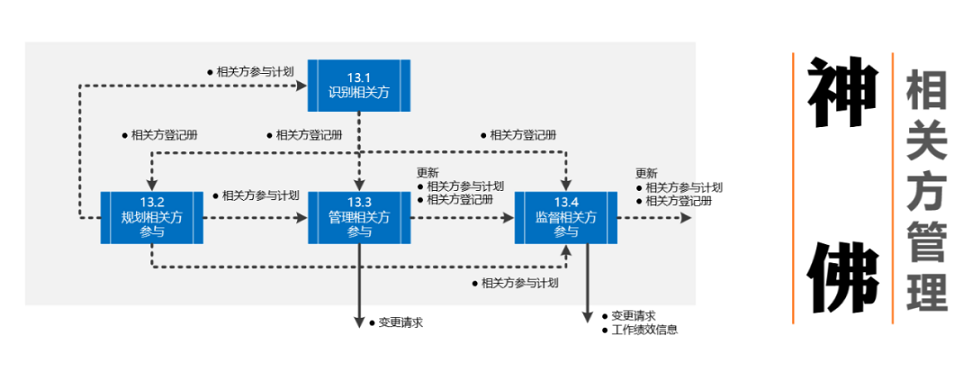

【项目管理精英必备】:信息系统项目管理师教程习题深度解析(第四版官方教材全面攻略)

# 摘要

信息系统项目管理是确保项目成功交付的关键活动,涉及一系列管理过程和知识领域。本文深入探讨了信息系统项目管理的各个方面,包括项目管理过程组、知识领域、实践案例、管理工具与技术,以及沟通和团队协作。通过分析不同的项目管理方法论(如瀑布、迭代、敏捷和混合模型),并结合具体案例,文章阐述了项目管理的最佳实践和策略。此外,本文还涵盖了项目管理中的沟通管理、团队协作的重要性,

最具代表性的改进过的UNet有哪些?

UNet是一种广泛用于图像分割任务的卷积神经网络结构,它的特点是结合了下采样(编码器部分)和上采样(解码器部分),能够保留细节并生成精确的边界。为了提高性能和适应特定领域的需求,研究者们对原始UNet做了许多改进,以下是几个最具代表性的变种:

1. **DeepLab**系列:由Google开发,通过引入空洞卷积(Atrous Convolution)、全局平均池化(Global Average Pooling)等技术,显著提升了分辨率并保持了特征的多样性。

2. **SegNet**:采用反向传播的方式生成全尺寸的预测图,通过上下采样过程实现了高效的像素级定位。

3. **U-Net+

惠普P1020Plus驱动下载:办公打印新选择

资源摘要信息: "最新惠普P1020Plus官方驱动"

1. 惠普 LaserJet P1020 Plus 激光打印机概述:

惠普 LaserJet P1020 Plus 是惠普公司针对家庭、个人办公以及小型办公室(SOHO)市场推出的一款激光打印机。这款打印机的设计注重小巧体积和便携操作,适合空间有限的工作环境。其紧凑的设计和高效率的打印性能使其成为小型企业或个人用户的理想选择。

2. 技术特点与性能:

- 预热技术:惠普 LaserJet P1020 Plus 使用了0秒预热技术,能够极大减少打印第一张页面所需的等待时间,首页输出时间不到10秒。

- 打印速度:该打印机的打印速度为每分钟14页,适合处理中等规模的打印任务。

- 月打印负荷:月打印负荷高达5000页,保证了在高打印需求下依然能稳定工作。

- 标配硒鼓:标配的2000页打印硒鼓能够为用户提供较长的使用周期,减少了更换耗材的频率,节约了长期使用成本。

3. 系统兼容性:

驱动程序支持的操作系统包括 Windows Vista 64位版本。用户在使用前需要确保自己的操作系统版本与驱动程序兼容,以保证打印机的正常工作。

4. 市场表现:

惠普 LaserJet P1020 Plus 在上市之初便获得了市场的广泛认可,创下了百万销量的辉煌成绩,这在一定程度上证明了其可靠性和用户对其性能的满意。

5. 驱动程序文件信息:

压缩包内包含了适用于该打印机的官方驱动程序文件 "lj1018_1020_1022-HB-pnp-win64-sc.exe"。该文件是安装打印机驱动的执行程序,用户需要下载并运行该程序来安装驱动。

另一个文件 "jb51.net.txt" 从命名上来看可能是一个文本文件,通常这类文件包含了关于驱动程序的安装说明、版本信息或是版权信息等。由于具体内容未提供,无法确定确切的信息。

6. 使用场景:

由于惠普 LaserJet P1020 Plus 的打印速度和负荷能力,它适合那些需要快速、频繁打印文档的用户,例如行政助理、会计或小型法律事务所。它的紧凑设计也使得这款打印机非常适合在桌面上使用,从而不占用过多的办公空间。

7. 后续支持与维护:

用户在购买后可以通过惠普官方网站获取最新的打印机驱动更新以及技术支持。在安装新驱动之前,建议用户先卸载旧的驱动程序,以避免版本冲突或不必要的错误。

8. 其它注意事项:

- 用户在使用打印机时应注意按照官方提供的维护说明定期进行清洁和保养,以确保打印质量和打印机的使用寿命。

- 如果在打印过程中遇到任何问题,应先检查打印机设置、驱动程序是否正确安装以及是否有足够的打印纸张和墨粉。

综上所述,惠普 LaserJet P1020 Plus 是一款性能可靠、易于使用的激光打印机,特别适合小型企业或个人用户。正确的安装和维护可以确保其稳定和高效的打印能力,满足日常办公需求。

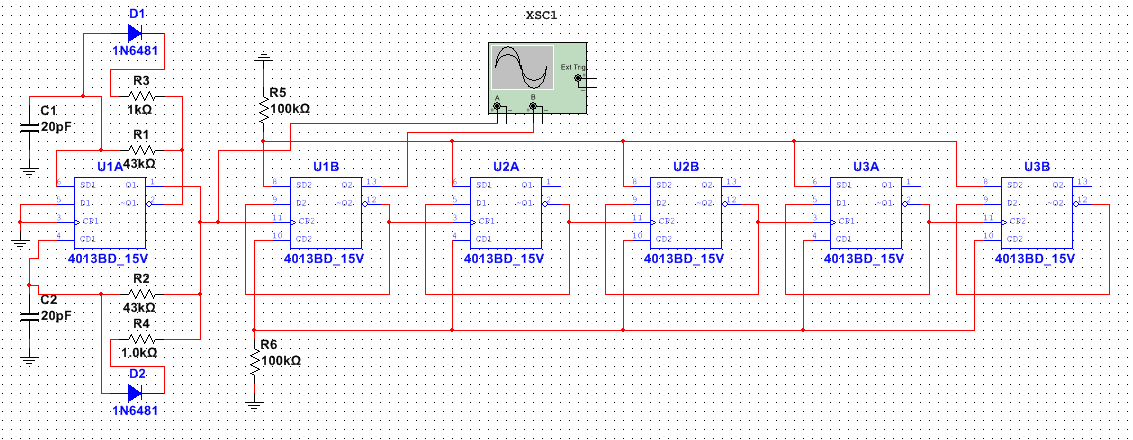

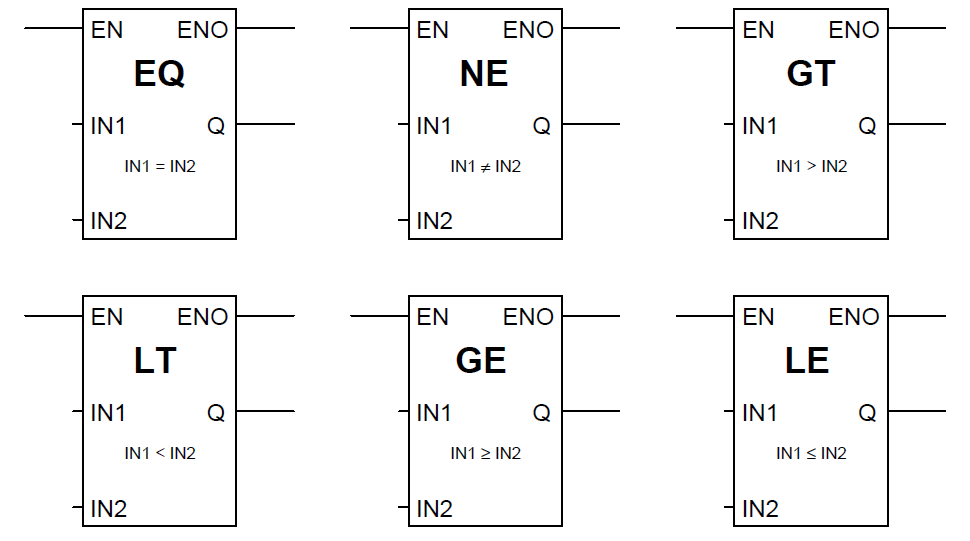

数字电路实验技巧:10大策略,让你的实验效率倍增!

# 摘要

本论文详细介绍了数字电路实验的基础理论、设备使用、设计原则、实践操作、调试与故障排除以及报告撰写与成果展示。首先探讨了数字电路实验所需的基本理论和实验设备的种类与使用技巧,包括测量和故障诊断方法。接着,深入分析了电路设计的原则,涵盖设计流程、逻辑简化、优化策略及实验方案的制定。在实践操作章节中,具体

altium designer布线

### Altium Designer 布线教程和技巧

#### 一、环境设置与准备

为了更高效地完成布线工作,前期的准备工作至关重要。确保原理图已经完全无误并编译成功[^2]。

#### 二、同步查看原理图与PCB布局

通过在原理图标题栏处右键点击并选择 "Split Vertical" 可实现原理图和PCB视图的同时展示,这有助于理解电路连接关系以及提高布线效率。

#### 三、自动布线器配置

Altium Designer内置有强大的自动布线功能。进入“Tools -> PCB Rules and Constraints Editor”,可以自定义诸如最小间距、过孔尺寸等参数来满足

Rust与OpenGL共同打造的迷宫游戏

资源摘要信息:"迷宫游戏开发指南"

在Rust和OpenGL环境下开发迷宫游戏涉及多个方面的知识点,包括编程语言Rust的基本语法和高级特性,OpenGL的图形编程原理以及游戏循环和资源管理等。以下详细说明了这些知识点:

1. Rust编程语言基础

Rust是一种系统编程语言,它提供了内存安全而无需垃圾回收器。Rust的目标是防止空指针解引用、缓冲区溢出等内存安全问题。迷宫游戏开发中,使用Rust可以高效利用系统资源并保证运行时的稳定性和性能。基础知识点包括但不限于:

- 变量和可变性

- 数据类型:整型、浮点型、字符、布尔类型、元组、数组、切片等

- 控制流:if、循环(for, while)、模式匹配

- 函数和闭包

- 所有权、借用和生命周期

- 结构体、枚举和特征

- 模块和使用语句

- 错误处理:Result和Option枚举

- 异步编程:async和await

2. OpenGL图形编程基础

OpenGL(Open Graphics Library)是一个跨语言、跨平台的API,用于渲染2D和3D矢量图形。在Rust中,可以使用gl-rs或其他类似的库来创建OpenGL上下文,并进行渲染操作。迷宫游戏开发中,开发者需要掌握的知识点包括:

- OpenGL上下文的创建和管理

- 着色器语言GLSL的基本语法

- 纹理映射、光源和材质处理

- 几何体的创建和管理(如顶点缓冲、索引缓冲等)

- 渲染管线的各个阶段(顶点处理、裁剪、光栅化等)

- 深度缓冲和模板缓冲的使用

- OpenGL状态机的理解和管理

3. 游戏开发循环

游戏开发循环是指游戏运行时不断循环进行的一系列步骤,通常包括输入处理、游戏状态更新和渲染。迷宫游戏开发中,游戏循环的设计与实现是至关重要的部分。涉及到的知识点包括:

- 游戏状态机的设计

- 输入事件的监听和处理(如键盘、鼠标事件)

- 游戏逻辑的更新(如玩家移动、碰撞检测、迷宫生成逻辑等)

- 场景的渲染和重绘

- 游戏帧率的控制和时间管理

4. 资源管理

资源管理是指游戏中各类资源(如图像、音频、模型等)的加载、使用和释放。在Rust中,这通常涉及到文件读取、内存管理和生命周期控制。迷宫游戏开发中需要的知识点包括:

- 文件系统的操作(如读取迷宫数据文件)

- 内存管理策略(如资源的动态加载和卸载)

- 图像和纹理的加载和使用

- 音频播放控制

- 资源释放时机的确定以避免内存泄漏

5. 迷宫游戏逻辑实现

迷宫游戏的逻辑实现是指游戏中迷宫的生成、玩家的引导和游戏的胜负判定等核心游戏机制。迷宫游戏逻辑实现中的关键知识点包括:

- 迷宫生成算法(如深度优先搜索算法、Prim算法或Kruskal算法等)

- 玩家和游戏对象的移动逻辑

- 路径寻找和导引逻辑(如A*算法)

- 胜负判定和游戏重置逻辑

6. 使用Rust和OpenGL库

实际开发中,开发者会使用一些Rust库来简化OpenGL的调用和管理。相关的知识点包括:

- cargo工具和Rust包管理

- 使用Rust的OpenGL绑定库(如gl-rs、glium等)

- 管理依赖和构建项目的配置文件(Cargo.toml)

- 使用第三方库来处理窗口创建和事件循环(如 glutin)

7. 调试和性能优化

在开发迷宫游戏的过程中,调试和性能优化是重要的环节,以确保游戏运行的流畅性和稳定性。相关的知识点包括:

- 使用调试工具(如gdb、rr、Valgrind等)进行错误追踪和性能分析

- 代码的性能优化策略(如循环展开、内存对齐、缓存优化等)

- 图形渲染的性能优化(如批处理渲染、优化状态切换、减少绘制调用等)

- 使用诊断工具(如Rust的cargo-expand等)来查看代码展开和宏展开

综上所述,Rust和OpenGL迷宫游戏的开发涉及众多知识点,需要开发者具备扎实的编程基础、图形编程经验、游戏开发知识和系统性能优化能力。通过使用Rust的现代编程特性和OpenGL的强大图形处理能力,可以开发出运行高效且稳定的迷宫游戏。

数字电路设计基础:9大技巧带你从理论飞跃到实践

# 摘要

数字电路设计是电子工程领域中的核心部分,它涵盖了从基本概念到高级技巧的广泛知识。本文首先介绍了数字电路设计的基本概念和原理,接着深入探讨了理论基础,包括逻辑门、组合逻辑电路以及时序逻辑电路的设计。随后,文章转向实践应用,讨论了设计工具、仿真测试方法和数字电路在不同领域的应用实例。最后,本

ubuntu 安装opencv2

### Ubuntu 上安装 OpenCV2 版本的库

对于希望在Ubuntu操作系统上安装特定版本如OpenCV2的情况,可以遵循一系列定制化的指令来达成目标。由于当前主流教程多集中于最新版OpenCV及其附加模块(opencv_contrib)的安装指导[^1],针对旧版本(例如OpenCV2)的操作则需特别注意兼容性和依赖关系。

#### 准备工作环境

为了确保顺利安装OpenCV2,在开始前应先更新系统的包列表并升级已有的软件包至最新状态:

```bash

sudo apt update && sudo apt upgrade -y

```

接着,移除任何可能存在的新版本Op

店面租赁合同范本下载指南

资源摘要信息:"店面租赁合同范本是用于规范店面出租和承租双方权益与义务的法律文件。它详细规定了租赁双方的权利和责任,帮助避免在租赁过程中可能出现的纠纷。本文档通常包含以下内容:

1. 合同当事人信息:包括出租方(房东)和承租方(租客)的基本信息,如姓名、地址、联系方式等。

2. 租赁物信息:详细描述所租赁店面的地址、面积、结构、设施、用途等,以及店面的具体位置和周边环境。

3. 租赁期限:明确约定租赁关系开始和结束的具体时间,以及续租的相关条件和程序。

4. 租金及其支付方式:列出租金的金额、支付周期、支付方式以及租金调整的条件和方式。

5. 维修和保养:规定承租方在租赁期间对店面进行日常维护的责任以及出租方对店面大修的责任。

6. 装修和装饰:明确承租方是否有权对店面进行装修,以及装修的相关规定和限制。

7. 转租和转租权:约定是否允许承租方将店面转租给第三方,以及相关的条件和程序。

8. 解除合同的条件:列出合同双方可以解除合同的条件和违约责任。

9. 违约责任:明确规定违约方应承担的经济责任,以及解决纠纷的方式。

10. 其他事项:包括合同附件、变更和补充协议的条款、争议解决方式等其他重要信息。

本合同范本通常作为参考,根据具体租赁情况需要双方协商调整。使用该合同范本前应充分理解合同条款,并根据实际情况进行必要的修改和补充,以确保合同的合法性和适用性。"

由于提供的文件信息中没有具体的【标签】和【压缩包子文件的文件名称列表】,无法针对这两部分提供具体内容的知识点。