首页

verilog数字时钟DE2

verilog数字时钟DE2

时间: 2023-11-17 09:07:56

浏览: 122

Verilog数字时钟DE2是一种基于FPGA的数字时钟,使用Verilog HDL编写。它可以通过输入时钟信号和按键信号来实现时间的修改和计数,并且可以显示当前的时间。根据引用内容,数字时钟DE2包含了时钟修改模块和计数模块,其中计数模块可以实现不同进制的计数,如24进制和60进制。数字时钟DE2可以用于实验室或家庭中,作为一种实用的计时工具。

阅读全文

相关推荐

数字时钟 verilog

使用verilog写的数字时钟程序,可调时间设置,闹钟。

verilog数字钟

verilog 数字钟设计,功能齐全 (1)设计一个数码管实时显示时、分、秒的数字时钟(24小时显示模式); (2)可以调节小时,分钟。 (3)能够进行24小时和12小时的显示切换。 (4)可以设置任意时刻闹钟,并且有开关闹钟功能。 (5)有整点报时功能,几点钟LED灯闪亮几下。 (6)有复位按键,复位后时间从零开始计时,但闹钟设置时间不变。

verilog 数字钟

verilong 数字钟代码 24小时制,可现实星期,仿真通过

clock2.rar_verilog 数字钟_verilog数字钟_数字钟 DE2_数字钟 verilog_数字钟verilog

在本文中,我们将深入探讨如何使用Verilog HDL(硬件描述语言)在DE2开发板上设计一个数字钟。Verilog是一种广泛应用于数字系统设计的编程语言,它允许工程师用代码来描述电子系统的功能和行为。DE2开发板是学习和...

FPGA基础时钟DE2

**FPGA基础时钟DE2设计详解** 在数字系统中,时钟是至关重要的组成部分,它协调着系统中各个部分的操作。FPGA(Field-Programmable Gate Array)作为可编程逻辑器件,允许用户根据需求自定义硬件逻辑,其中时钟生成...

hex_7seg.rar_DE2 verilog_de2_de2 hex 16b

标题中的“hex_7seg.rar_DE2 verilog_de2_de2 hex 16b”指的是一个使用Verilog语言编写的项目,目标是在Altera DE2开发板上实现一个16位十六进制到七段数码管的译码器。DE2开发板是Altera公司推出的基于 Cyclone II ...

verilog语言时钟代码

在这个“verilog语言时钟代码”项目中,我们主要关注如何使用Verilog来创建一个功能丰富的时钟模块,这个模块能够在DE2开发板上实现多种功能,如置数、清零、倒计时、正计时以及蜂鸣报警。 首先,理解Verilog的基本...

DE2_SD_Card_Audio.rar_DE2 verilog_DE2_SD_Card_Audio_de2_de2 audi

Verilog代码中会包含SPI时钟的产生、命令和数据的发送接收、错误检测等功能。对于音频播放,可能还需要包含一个音频解码器,例如支持MP3或WAV格式的解码。 DE2开发板上的音频处理模块可能包含了DA转换器(Digital-...

de2_net verilog de2开发板

DE2开发板是一款基于 Altera 公司Cyclone II系列FPGA的实验平台,常用于数字电子设计的教学和研究。Verilog是一种硬件描述语言(HDL),它被用来设计、建模和验证数字系统,包括FPGA和ASIC。本项目“de2_net verilog...

tut_DE2_sdram_verilog_DE2verilog_sdram_memory_

通过阅读这份文档,你将能够掌握如何在DE2开发板上使用Verilog语言设计并实现一个有效的SDRAM控制器,这对于理解数字系统设计和FPGA应用至关重要。 在学习过程中,你可能还需要了解一些基本的数字逻辑和计算机体系...

基于verilog的时钟设计

Verilog是一种硬件描述语言(HDL),广泛用于设计和验证数字集成电路,包括时钟管理系统。本篇文章将深入探讨如何使用Verilog来设计时钟以及在DE2开发板上的实现。 一、Verilog简介 Verilog是IEEE 1364标准定义的一...

uart.rar_DE2 串口_DE2-70串口_UART HDL_de2 UART verilog_de2-70 串口

本项目是基于DE2-70 FPGA开发板使用Verilog HDL语言实现的UART模块,可用于实现数据的串行发送和接收。 DE2-70开发板是一款基于ALTERA Cyclone IV系列FPGA的硬件平台,具有丰富的外围接口,包括GPIO、SPI、I2C、...

DE2_i2sound.rar_DE2 verilog_DE2_i2sound download_I2S_download DE

在DE2_i2sound项目中,Verilog代码将用于实现I2S接口,可能包括时钟管理、数据收发、控制信号处理等模块。对于初学者来说,这些代码提供了很好的学习资源,可以了解如何在FPGA上实现音频接口。 2. i2sound.sof文件...

SDRAM.rar_VERILOG SDRAM_sdram de2_sdram verilog

在本项目中,我们关注的是如何使用Verilog HDL(硬件描述语言)来设计一个SDRAM控制器,该控制器能够在DE2-70开发板上运行。 Verilog HDL是一种强大的工具,它允许工程师以类似于编程语言的方式描述数字系统的逻辑...

DE2下日历时钟设计

本文将深入探讨如何在DE2平台上设计一个24小时制的日历时钟系统,该系统能够同时在数码管和LCD显示屏上显示时间,并且支持通过按键进行模式切换,从而提供用户友好的交互体验。 首先,设计的核心在于FPGA编程,利用...

基于FPGA的数字时钟的设计

基于FPGA的数字时钟设计涉及了多个关键知识点,包括FPGA的基本概念、Quartus II开发环境的应用、Verilog HDL硬件描述语言的使用以及数字时钟的电路原理。 首先,FPGA(Field-Programmable Gate Array)是可编程逻辑...

karaoke machine de2 verilog

总的来说,"karaoke machine de2 verilog"是一个集成了数字信号处理、硬件接口设计、用户交互和存储管理等多个方面的综合性项目。通过这个项目,可以深入理解和掌握Verilog语言以及FPGA开发流程,同时对音频处理技术...

基于DE2开发板的Verilog时钟功能开发教程

资源摘要信息: "Verilog开发时钟功能基于DE2开发板" 知识点概述: 本资源涉及到使用Verilog语言设计与实现时钟功能,并通过DE2开发板进行硬件实现和测试。DE2开发板是Altera公司(现为英特尔旗下公司)推出的一款...

Verilog HDL实现的FPGA数字时钟设计

"这篇学术论文主要探讨了基于FPGA(现场可编程门阵列)的数字时钟设计,利用Verilog HDL硬件描述语言在Altera公司的Quartus II开发环境下进行实现。设计的数字时钟具有通用性和可移植性,能够在不同系列的FPGA芯片上...

Verilog实现DE2-70开发板上的SDRAM控制器

资源摘要信息:"SDRAM控制器的Verilog实现与DE2-70开发板应用" 知识点: 1. SDRAM控制器:SDRAM(Synchronous Dynamic Random Access Memory)是动态随机存取存储器的一种,与传统的DRAM相比,其最大的特点是与系统...

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

海量

VIP免费资源

千本

正版电子书

商城

会员专享价

千门

课程&专栏

全年可省5,000元

立即开通

全年可省5,000元

立即开通

大家在看

COBIT操作手册

COBIT操作手册大全,欢迎大家下载使用

2000-2022年 上市公司-股价崩盘风险相关数据(数据共52234个样本,包含do文件、excel数据和参考文献).zip

上市公司股价崩盘风险是指股价突然大幅下跌的可能性。这种风险可能由多种因素引起,包括公司的财务状况、市场环境、政策变化、投资者情绪等。 测算方式:参考《管理世界》许年行老师和《中国工业经济》吴晓晖老师的做法,使用负收益偏态系数(NCSKEW)和股票收益上下波动比率(DUVOL)度量股价崩盘风险。 数据共52234个样本,包含do文件、excel数据和参考文献。 相关数据指标 stkcd、证券代码、year、NCSKEW、DUVOL、Crash、Ret、Sigma、证券代码、交易周份、周个股交易金额、周个股流通市值、周个股总市值、周交易天数、考虑现金红利再投资的周个股回报率、市场类型、周市场交易总股数、周市场交易总金额、考虑现金红利再投资的周市场回报率(等权平均法)、不考虑现金红利再投资的周市场回报率(等权平均法)、考虑现金红利再投资的周市场回报率(流通市值加权平均法)、不考虑现金红利再投资的周市场回报率(流通市值加权平均法)、考虑现金红利再投资的周市场回报率(总市值加权平均法)、不考虑现金红利再投资的周市场回报率(总市值加权平均法)、计算周市场回报率的有效公司数量、周市场流通市值、周

IEEE_Std_1588-2008

IEEE-STD-1588-2008 标准文档(英文版),里面有关PTP profile关于1588-2008的各种定义

SC1235设计应用指南_V1.2.pdf

SC1235设计应用指南_V1.2.pdf

CG2H40010F PDK文件

CREE公司CG2H40010F功率管的PDK文件。用于ADS的功率管仿真。

最新推荐

基于FPGA的数字时钟的设计

基于FPGA的数字时钟设计涉及了多个关键知识点,包括FPGA的基本概念、Quartus II开发环境的应用、Verilog HDL硬件描述语言的使用以及数字时钟的电路原理。 首先,FPGA(Field-Programmable Gate Array)是可编程逻辑...

verilog 编写数码管循环显示器

本文档将介绍如何使用Verilog语言编写一个数码管循环显示程序,该程序将在DE2核心FPGA开发板上实现特定字符的循环显示。 首先,项目的设计目标是在数码管上循环显示“HEUAC407”这八位英文字符和数字。为了实现这一...

Altera Cyclone II系列FPGA开发板 DE2板资料

DE2 板上安装了多种时钟电路,包括 50MHz晶振和 27MHz 晶振等。这些时钟电路可以提供稳定的时钟信号,满足不同应用场景下的时钟需求。 多媒体模块 DE2 板上安装了多媒体模块,包括 24 位 CD 音质音频芯片 WM8731、...

Verilog HDL 七段数码管倒计时效果

Verilog HDL是一种硬件描述语言,常用于数字电子系统的建模和设计,特别是在FPGA(Field Programmable Gate Array)和ASIC(Application-Specific Integrated Circuit)的设计中。在本实验中,我们利用Verilog HDL...

OpenCV部署YOLOv5-pose人体姿态估计(C++和Python双版本).zip

OpenCV部署YOLOv5-pose人体姿态估计(C++和Python双版本).zip [资源说明] 1、该项目是团队成员近期最新开发,代码完整,资料齐全,含设计文档等 2、上传的项目源码经过严格测试,功能完善且能正常运行,请放心下载使用! 3、本项目适合计算机相关专业(人工智能、通信工程、自动化、电子信息、物联网等)的高校学生、教师、科研工作者、行业从业者下载使用,可借鉴学习,也可直接作为毕业设计、课程设计、作业、项目初期立项演示等,也适合小白学习进阶,遇到问题不懂就问,欢迎交流。 4、如果基础还行,可以在此代码基础上进行修改,以实现其他功能,也可直接用于毕设、课设、作业等。 5、不懂配置和运行,可远程教学 欢迎下载,学习使用!

HTML挑战:30天技术学习之旅

资源摘要信息: "desafio-30dias" 标题 "desafio-30dias" 暗示这可能是一个与挑战或训练相关的项目,这在编程和学习新技能的上下文中相当常见。标题中的数字“30”很可能表明这个挑战涉及为期30天的时间框架。此外,由于标题是西班牙语,我们可以推测这个项目可能起源于或至少是针对西班牙语使用者的社区。标题本身没有透露技术上的具体内容,但挑战通常涉及一系列任务,旨在提升个人的某项技能或知识水平。 描述 "desafio-30dias" 并没有提供进一步的信息,它重复了标题的内容。因此,我们不能从中获得关于项目具体细节的额外信息。描述通常用于详细说明项目的性质、目标和期望成果,但由于这里没有具体描述,我们只能依靠标题和相关标签进行推测。 标签 "HTML" 表明这个挑战很可能与HTML(超文本标记语言)有关。HTML是构成网页和网页应用基础的标记语言,用于创建和定义内容的结构、格式和语义。由于标签指定了HTML,我们可以合理假设这个30天挑战的目的是学习或提升HTML技能。它可能包含创建网页、实现网页设计、理解HTML5的新特性等方面的任务。 压缩包子文件的文件名称列表 "desafio-30dias-master" 指向了一个可能包含挑战相关材料的压缩文件。文件名中的“master”表明这可能是一个主文件或包含最终版本材料的文件夹。通常,在版本控制系统如Git中,“master”分支代表项目的主分支,用于存放项目的稳定版本。考虑到这个文件名称的格式,它可能是一个包含所有相关文件和资源的ZIP或RAR压缩文件。 结合这些信息,我们可以推测,这个30天挑战可能涉及了一系列的编程任务和练习,旨在通过实践项目来提高对HTML的理解和应用能力。这些任务可能包括设计和开发静态和动态网页,学习如何使用HTML5增强网页的功能和用户体验,以及如何将HTML与CSS(层叠样式表)和JavaScript等其他技术结合,制作出丰富的交互式网站。 综上所述,这个项目可能是一个为期30天的HTML学习计划,设计给希望提升前端开发能力的开发者,尤其是那些对HTML基础和最新标准感兴趣的人。挑战可能包含了理论学习和实践练习,鼓励参与者通过构建实际项目来学习和巩固知识点。通过这样的学习过程,参与者可以提高在现代网页开发环境中的竞争力,为创建更加复杂和引人入胜的网页打下坚实的基础。

【CodeBlocks精通指南】:一步到位安装wxWidgets库(新手必备)

# 摘要 本文旨在为使用CodeBlocks和wxWidgets库的开发者提供详细的安装、配置、实践操作指南和性能优化建议。文章首先介绍了CodeBlocks和wxWidgets库的基本概念和安装流程,然后深入探讨了CodeBlocks的高级功能定制和wxWidgets的架构特性。随后,通过实践操作章节,指导读者如何创建和运行一个wxWidgets项目,包括界面设计、事件

andorid studio 配置ERROR: Cause: unable to find valid certification path to requested target

### 解决 Android Studio SSL 证书验证问题 当遇到 `unable to find valid certification path` 错误时,这通常意味着 Java 运行环境无法识别服务器提供的 SSL 证书。解决方案涉及更新本地的信任库或调整项目中的网络请求设置。 #### 方法一:安装自定义 CA 证书到 JDK 中 对于企业内部使用的私有 CA 颁发的证书,可以将其导入至 JRE 的信任库中: 1. 获取 `.crt` 或者 `.cer` 文件形式的企业根证书; 2. 使用命令行工具 keytool 将其加入 cacerts 文件内: ```

VC++实现文件顺序读写操作的技巧与实践

资源摘要信息:"vc++文件的顺序读写操作" 在计算机编程中,文件的顺序读写操作是最基础的操作之一,尤其在使用C++语言进行开发时,了解和掌握文件的顺序读写操作是十分重要的。在Microsoft的Visual C++(简称VC++)开发环境中,可以通过标准库中的文件操作函数来实现顺序读写功能。 ### 文件顺序读写基础 顺序读写指的是从文件的开始处逐个读取或写入数据,直到文件结束。这与随机读写不同,后者可以任意位置读取或写入数据。顺序读写操作通常用于处理日志文件、文本文件等不需要频繁随机访问的文件。 ### VC++中的文件流类 在VC++中,顺序读写操作主要使用的是C++标准库中的fstream类,包括ifstream(用于从文件中读取数据)和ofstream(用于向文件写入数据)两个类。这两个类都是从fstream类继承而来,提供了基本的文件操作功能。 ### 实现文件顺序读写操作的步骤 1. **包含必要的头文件**:要进行文件操作,首先需要包含fstream头文件。 ```cpp #include <fstream> ``` 2. **创建文件流对象**:创建ifstream或ofstream对象,用于打开文件。 ```cpp ifstream inFile("example.txt"); // 用于读操作 ofstream outFile("example.txt"); // 用于写操作 ``` 3. **打开文件**:使用文件流对象的成员函数open()来打开文件。如果不需要在创建对象时指定文件路径,也可以在对象创建后调用open()。 ```cpp inFile.open("example.txt", std::ios::in); // 以读模式打开 outFile.open("example.txt", std::ios::out); // 以写模式打开 ``` 4. **读写数据**:使用文件流对象的成员函数进行数据的读取或写入。对于读操作,可以使用 >> 运算符、get()、read()等方法;对于写操作,可以使用 << 运算符、write()等方法。 ```cpp // 读取操作示例 char c; while (inFile >> c) { // 处理读取的数据c } // 写入操作示例 const char *text = "Hello, World!"; outFile << text; ``` 5. **关闭文件**:操作完成后,应关闭文件,释放资源。 ```cpp inFile.close(); outFile.close(); ``` ### 文件顺序读写的注意事项 - 在进行文件读写之前,需要确保文件确实存在,且程序有足够的权限对文件进行读写操作。 - 使用文件流进行读写时,应注意文件流的错误状态。例如,在读取完文件后,应检查文件流是否到达文件末尾(failbit)。 - 在写入文件时,如果目标文件不存在,某些open()操作会自动创建文件。如果文件已存在,open()操作则会清空原文件内容,除非使用了追加模式(std::ios::app)。 - 对于大文件的读写,应考虑内存使用情况,避免一次性读取过多数据导致内存溢出。 - 在程序结束前,应该关闭所有打开的文件流。虽然文件流对象的析构函数会自动关闭文件,但显式调用close()是一个好习惯。 ### 常用的文件操作函数 - `open()`:打开文件。 - `close()`:关闭文件。 - `read()`:从文件读取数据到缓冲区。 - `write()`:向文件写入数据。 - `tellg()` 和 `tellp()`:分别返回当前读取位置和写入位置。 - `seekg()` 和 `seekp()`:设置文件流的位置。 ### 总结 在VC++中实现顺序读写操作,是进行文件处理和数据持久化的基础。通过使用C++的标准库中的fstream类,我们可以方便地进行文件读写操作。掌握文件顺序读写不仅可以帮助我们在实际开发中处理数据文件,还可以加深我们对C++语言和文件I/O操作的理解。需要注意的是,在进行文件操作时,合理管理和异常处理是非常重要的,这有助于确保程序的健壮性和数据的安全。

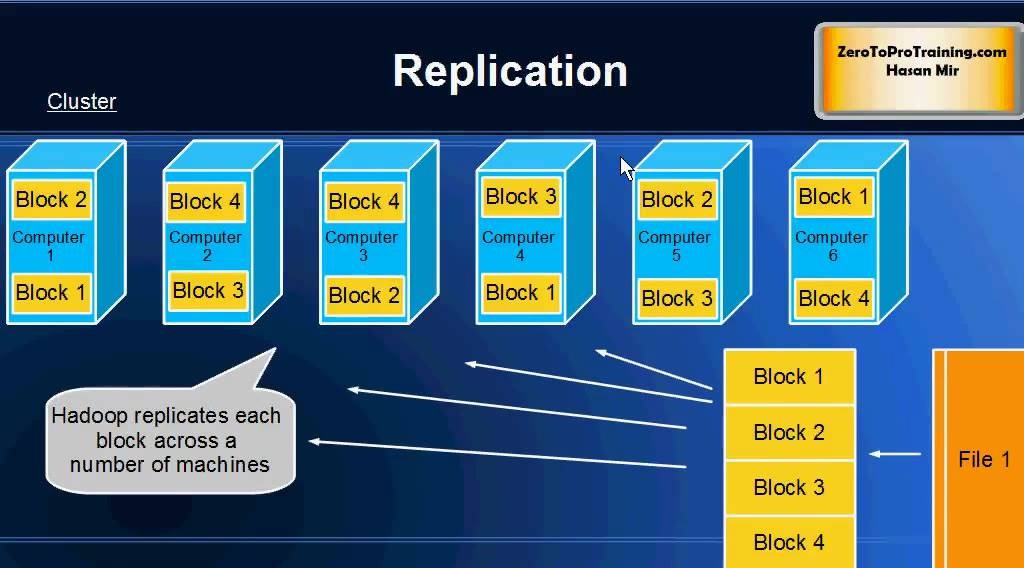

【大数据时代必备:Hadoop框架深度解析】:掌握核心组件,开启数据科学之旅

# 摘要 Hadoop作为一个开源的分布式存储和计算框架,在大数据处理领域发挥着举足轻重的作用。本文首先对Hadoop进行了概述,并介绍了其生态系统中的核心组件。深入分