【嵌入式系统优化】:C语言下的I2C通信性能调优策略(性能优化手册)

发布时间: 2024-12-11 14:52:37 阅读量: 11 订阅数: 11

C语言嵌入式系统编程修炼之软件架构篇和性能优化篇

# 1. 嵌入式系统与I2C通信简介

在现代电子设备中,嵌入式系统扮演着至关重要的角色。这些系统能够执行特定任务,通常搭载着实时操作系统,与我们的日常生活密切相关,比如家用电器、汽车电子、工业控制等。I2C通信协议是这些设备中常见的串行通信协议之一,它因简单、成本低和易于实现的特点而广泛应用于嵌入式系统中。

I2C(Inter-Integrated Circuit)是一种由Philips半导体(现在的NXP)在1980年代早期开发的多主机串行计算机总线。该协议能够在主设备(如微控制器)和多个从设备(如传感器、ADC、LCD驱动器等)之间进行通信。I2C设计之初是为了在芯片与芯片之间进行简单的数据交换,因此,它在硬件上仅需要两条线:串行数据线(SDA)和串行时钟线(SCL)。

为了更好地理解I2C协议,我们需要从它的基础开始探索。在第二章中,我们将深入分析I2C通信协议的工作原理、信号和时序、设备地址以及数据传输规范等关键技术点。接下来,让我们开始对I2C通信协议的基础知识进行详细探讨。

# 2. I2C通信协议深度解析

## 2.1 I2C通信协议基础

### 2.1.1 I2C协议的工作原理

I2C (Inter-Integrated Circuit) 是一种多主机串行总线,广泛应用于微控制器和各种外围设备之间的短距离通信。其设计初衷是简化主板上的芯片间通信,使得系统设计可以更加模块化和轻量化。I2C使用两条线:一条串行数据线(SDA)和一条串行时钟线(SCL)。总线的控制权可以由任何连接到该总线上的设备取得,这些设备既可以是发送数据的主设备,也可以是接收数据的从设备。

I2C通信的物理层中,总线是开放式的集电极或开漏极线,它允许多个主设备通过总线进行通信,但同一时间内只允许一个主设备控制总线。当总线上没有信号时,两条线均为高电平状态。主设备通过拉低SDA线来发起一个起始信号,结束传输时则通过释放SDA线产生一个停止信号。在数据传输期间,SCL线由主设备控制,用于提供时钟信号,确保数据以正确的时序在SDA线上进行传输。

### 2.1.2 I2C协议的数据传输机制

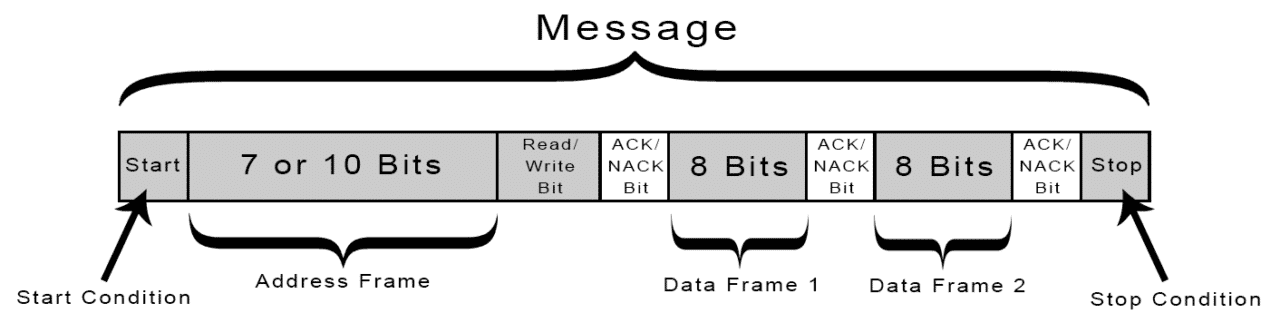

数据在I2C总线上的传输按照字节为单位进行,每个字节由8位组成,并且遵循先传最高位(MSB)的约定。在每个字节传输完毕之后,接收方会发送一个应答位(ACK)表示数据接收成功,或者发送一个非应答位(NACK)表示接收失败或者没有更多数据需要接收。

数据传输的一般过程包括:起始信号、设备地址传输、读/写位、应答位、数据传输、应答位以及停止信号。当主设备需要读取从设备的数据时,它会发送从设备的地址以及读位,随后从设备回应ACK并开始数据传输。若要向从设备写入数据,主设备发送设备地址和写位,然后开始数据传输,每次传输后从设备回应ACK。

## 2.2 I2C通信中的信号和时序

### 2.2.1 I2C的起始和停止信号

起始信号(START)是由主设备发起的,用于通知所有其他设备开始一个新的数据传输序列。它由主设备在SCL为高电平时将SDA从高电平拉低至低电平实现。

停止信号(STOP)则是由主设备发起的,标志着一个数据传输序列的结束。停止信号由主设备在SCL为高电平时将SDA从低电平拉高至高电平实现。

### 2.2.2 I2C时钟同步和延时处理

在I2C总线中,时钟同步是一个重要的概念。由于I2C允许多个主设备在同一总线上运行,因此必须有一个机制来处理时钟的同步问题。当多个主设备同时尝试进行通信时,它们可以协商确定一个共同的时钟频率,称为时钟同步。I2C协议提供了时钟拉伸(Clock Stretching)的机制来实现这一点,从设备可以延长时钟周期,确保数据处理的正确性。

在某些情况下,I2C总线上的设备可能需要额外的时间来处理接收到的数据,或者准备要发送的数据。在这种情况下,设备可以利用时钟延时来减慢总线的时钟频率,从而获得所需的时间。

## 2.3 I2C设备地址和数据传输

### 2.3.1 设备地址的分配与识别

I2C协议规定,每个连接到总线上的从设备必须有一个唯一的设备地址,以便主设备能够识别和选择特定的从设备进行通信。设备地址通常由7位或10位组成,7位地址用于大多数常见的设备,而10位地址则用于地址空间更大的设备。

设备地址通常包括两部分:固定的部分和可编程的部分。固定部分是由设备制造商决定的,用于区分设备类型的ID。可编程的部分则是在设备内部设置的,以确保在同一总线上的地址不发生冲突。设备地址的最后一位是读/写位(R/W bit),当该位为0时,表示主设备将向从设备写入数据;当该位为1时,则表示主设备将从从设备读取数据。

### 2.3.2 数据的读写操作规范

数据传输包括写入操作和读取操作两种类型,具体操作依赖于设备地址后跟的读/写位。

在写操作过程中,主设备首先发送起始信号,然后跟随设备地址以及写位(通常是0)。之后从设备回应ACK,表示准备好接收数据。主设备接着开始发送数据,每发送一个字节后,从设备发送ACK表示已经正确接收。当所有数据发送完毕后,主设备发送停止信号,结束此次通信。

读操作则有些许不同,主设备发送起始信号和设备地址(读位为1)后,如果从设备准备就绪,它会回应ACK并开始发送数据。主设备在接收到每个字节后发送ACK(除了最后一个字节发送NACK),通知从设备数据已经接收完毕,最后主设备发送停止信号,结束通信。

通过以上分析,我们可以看出I2C协议的细节设计具有高度的灵活性和可扩展性,它通过简单的两条线就能实现复杂的数据通信,而且对设备的硬件要求并不高,因此成为嵌入式系统中应用广泛的一种通信协议。然而,I2C通信协议的灵活性也带来了诸如总线冲突、数据速率限制等问题,在下一章节中,我们将深入探讨如何解决这些问题,并介绍如何在C语言环境下进行I2C驱动开发。

# 3. C语言环境下的I2C驱动开发

### 3.1 C语言在嵌入式系统中的应用

C语言在嵌入式系统中的优势在于其接近硬件的特性,允许开发者直接与硬件设备进行交互,同时提供丰富的标准库支持,使得编程更加高效。嵌入式系统通常资源受限,包括处理器性能、内存大小和存储空间等。C语言编译器可以优化代码大小,生成紧凑且高效的机器代码,适合于资源受限的嵌入式环境。

#### 3.1.1 C语言在嵌入式系统中的优势

C语言被广泛应用于嵌入式系统开发的主要原因包括:

- **高效性**:C语言在编译时优化程度较高,能够生成运行高效的代码。

- **硬件操作的便利性**:直接通过指针访问硬件寄存器和进行内存操作,提供底层硬件控制的能力。

- **可移植性**:C语言程序的可移植性较好,可以通过修改少量的硬件依赖代码移植到不同的硬件平台。

- **编译器工具链丰富**:支持多种编译器和调试工具,为开发人员提供了良好的开发和调试体验。

#### 3.1.2 嵌入式系统中C语言编译环境的搭建

搭建C语言编译环境通常涉及以下几个步骤:

- **选择合适的编译器**:常见的嵌入式C编译器包括GCC(GNU Compiler Collection)、ARM Keil、IAR Embedded Workbench等。

- **配置交叉编译工具链**:在非目标硬件平台(例如x86 PC)上编译适用于目标硬件平台(例如ARM Cortex-M处理器)的程序。

- **安装开发和调试工具**:如GDB调试器,以及串口、JTAG或SWD调试器等硬件调试接口。

- **编写和测试代码**:开始编写程序,并使用开发板进行实际测试。

- **配置编译选项**:确保编译器设置正确,例如处理器架构、优化级别、内存设置等。

### 3.2 C语言实现I2C驱动程序

I2C驱动程序通常包含与硬件通信的基础函数,如初始化I

0

0