【PCIE 3.0设备通信】:实现端到端数据传输与同步的策略

发布时间: 2024-12-14 13:50:16 阅读量: 1 订阅数: 2

PCIe_3.0_spec_pcie3.0spec_pciespec_pcie_PCIe_3.0_spec_pcie3spec_

参考资源链接:[PCIe 3.0协议详细解析:速度与规范升级](https://wenku.csdn.net/doc/6trfrxoi77?spm=1055.2635.3001.10343)

# 1. PCIE 3.0标准概述

PCI Express(PCIE)技术是现代计算机系统中至关重要的高速串行计算机扩展总线标准。自2003年首次引入以来,PCIE已经发展了多个版本,其中PCIE 3.0版本在2010年推出,它不仅显著提高了带宽,还在设计上引入了诸多改进,以应对日益增长的数据传输需求。

## 1.1 PCIE标准的演进

从PCIE 1.0到PCIE 3.0,带宽实现了翻倍增长,每通道的传输速率从2.5 GT/s(Giga Transfers per second)增加到8 GT/s。这一进步对于图形卡、SSD存储、网络接口卡等高性能设备的I/O(输入/输出)速度有着直接的积极影响。

## 1.2 PCIE 3.0的关键特性

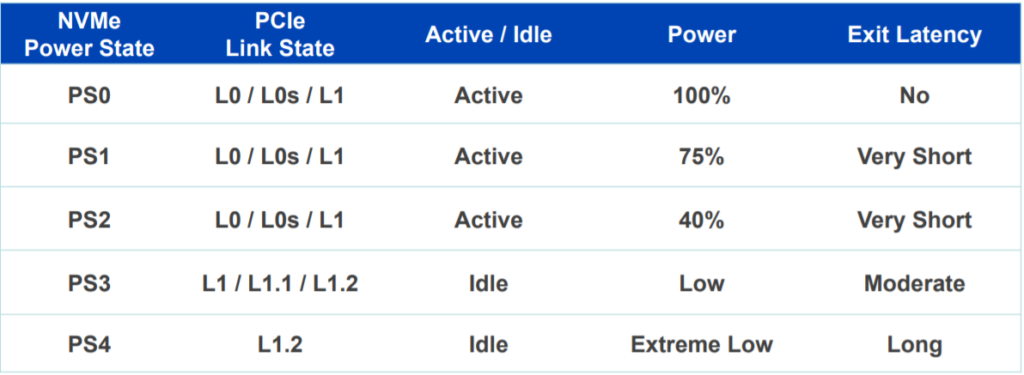

PCIE 3.0的关键特性包括但不限于其高速的数据传输率,以及改进的信号完整性和电源管理。其带宽的提升为高吞吐量的应用场景提供了更强的支持,使得在数据中心、高性能计算和游戏设备等领域中,PCIE 3.0成为不可或缺的技术标准。

## 1.3 PCIE 3.0的应用前景

随着技术的演进,PCIE 3.0不仅在个人电脑和服务器上有着广泛的应用,还扩展到了嵌入式系统、移动设备等更多领域。它的普及极大地促进了硬件设备的标准化,简化了设备间的互操作性,为未来技术的发展奠定了基础。

通过了解PCIE 3.0标准的演进,关键特性和应用前景,我们可以更加深入地探索其在硬件通信、软件策略以及高级应用中的实际应用和优化方法。接下来,我们将进一步深入探讨PCIE 3.0的硬件通信基础。

# 2. PCIE 3.0硬件通信基础

### 2.1 PCIE 3.0硬件架构解析

#### 接口类型和插槽

PCI Express(PCIE)是现代计算机架构中的一项关键连接技术,用于连接主板上的设备和扩展卡。PCIE 3.0作为其中的一个重要版本,其架构设计支持广泛的接口类型和插槽。最常见的接口类型包括x1, x4, x8和x16,其中“x”后面的数字表示PCIE插槽的通道数量。每个通道的传输速率可达8GT/s,对于x16插槽而言,单向数据传输速率可达到16GB/s。

| 接口类型 | 通道数 | 单向理论带宽 |

|----------|--------|--------------|

| x1 | 1 | 1GB/s |

| x4 | 4 | 4GB/s |

| x8 | 8 | 8GB/s |

| x16 | 16 | 16GB/s |

在物理实现上,PCIE插槽通常设计为向下兼容,例如x16插槽可以支持x1, x4等较小的设备。不同的接口类型在实际使用中主要根据所需带宽进行选择,例如,独立显卡通常使用x16插槽以充分利用带宽。

#### 信号传输与电气特性

PCIE 3.0的信号传输依赖于差分信号线对,支持双工传输,即数据同时双向传输。与PCIE 2.0相比,PCIE 3.0在电气特性上做了优化,使得信号在传输过程中受到的干扰更小,从而提供更高质量的信号。为了维持高速数据传输的稳定性,PCIE 3.0使用了特定的编码技术,如8b/10b编码,该技术将8位数据编码为10位传输,增加了额外的位用于错误检测和同步。

电气特性方面,PCIE 3.0规范定义了最大电压1.5V和1.8V两种标准,而最新的PCIE 4.0规范则已经开始采用1.2V。电气特性决定了PCIE设备的功耗和热设计功率(TDP),影响设备的散热设计。

### 2.2 PCIE 3.0数据包传输机制

#### 数据包格式与结构

PCIE 3.0采用了分层的数据包格式,包括事务层包(TLPs)、数据链路层包(DLLPs)和物理层包(PLPs)。事务层包用于主机与端点设备之间的数据传输,包含了地址、命令和数据信息;数据链路层包用于确保事务层包的可靠传输;物理层包则包含在物理层传输中的附加信息。每一层的数据包都包含了一系列的字段,如序列号用于流量控制,头信息用于标识数据包的类型和大小。

```

+-----------------------------------------------+

| Transaction Layer Packet (TLP) Header |

| +-------------------------------------------+ |

| | TLP Header Fields | |

| +-------------------------------------------+ |

| | Data | |

+-----------------------------------------------+

```

事务层包的头信息通常包括请求者ID、请求类型、包长度等关键信息,而数据部分则是实际需要传输的数据内容。这种结构化的数据包设计允许PCIE设备能够有效地处理各种不同类型的传输需求。

#### 流水线技术和流量控制

PCIE 3.0的数据传输通过流水线技术大大提高了效率。流水线技术允许同时进行多个事务的传输,而不需要等待前一个事务的完成。这种并行处理机制显著提高了数据吞吐率,尤其是在高带宽的应用场景下。

此外,PCIE 3.0还采用了先进的流量控制机制。流量控制基于信用系统,发送方在传输数据前需要获得接收方的信用授权。如果接收方的缓冲区已满,发送方会暂停发送,直到接收方重新提供可用的缓冲区。这种机制确保了传输的效率,同时避免了数据丢失。

### 2.3 端到端连接的建立与维护

#### 链路训练与初始化

在PCIE设备启动或上电后,设备必须完成链路训练以建立通信。链路训练是一个协商过程,目的是确定两个连接点之间的最大吞吐能力、链路宽度、时钟频率等参数。初始化过程中,链路双方会进行一系列的交互,以确保数据能够按照正确的速率和格式传输。

```

+----------------+ +----------------+

| 发送端设备 | | 接收端设备 |

| | | |

| 初始化请求 +---->+ |

| | | 同意/拒绝 |

| |<----+ |

+----------------+ +----------------+

```

链路初始化成功后,端点设备将能够交换事务层包和数据链路层包,进行实际的数据传输。这个过程对最终用户的透明性很强,但对系统性能的影响很大,良好的初始化过程可以确保系统稳定高效运行。

#### 错误检测与纠正机制

为了保证数据传输的可靠性,PCIE 3.0实现了多种错误检测与纠正机制。包括奇偶校验、循环冗余校验(CRC)以及更复杂的错误检测和纠正码(ECC)。这些机制能够在不同层次上确保数据在传输过程中没有被破坏或丢失。

一旦检测到错误,PCIE 3.0提供了重试机制。如果检测到数据包损坏,接收方会要求发送方重新发送。对于数据链路层和物理层的错误,PCIE 3.0采用了更复杂的错误检测和纠正算法,能够修复一定数量的比特错误,保障了通信的可靠性。

这些复杂但精细的错误处理机制,确保了在各种环境下,PCIE 3.0能够提供稳定的连接和数据传输,使得PCIE技术成为了当前计算机硬件通信的事实标准。

# 3. PCIE 3.0软件通信策略

## 3.1 操作系统中的PCIE驱动模型

### 3.1.1 驱动架构与加载流程

在操作系统中,PCIE驱动模型是软件通信策略的核心组件。该模型包括硬件抽象层(HAL)、总线驱动、设备驱动以及一些特定于操作系统的接口。HAL负责硬件的通用操作,包括端口、中断和其他硬件资源的抽象。总线驱动负责管理和识别连接到PCIE总线的设备,而设备驱动则负责处理特定硬件设备的通信和控制逻辑。

驱动程序加载流程可以分为几个步骤:

1. **加载驱动程序模块**:操作系统加载驱动程序,将其包含在内核空间中。

2. **初始化驱动程序**:在加载后,操作系统调用驱动程序中的初始化入口点,执行必要的资源申请和硬件探测。

3. **设备发现**:驱动程序通过查询PCIE配置空间来发现连接的设备,并为每个设备创建逻辑表示。

4. **资源分配**:系统为设备分配I/O空间、内存空间和中断请求(IRQ)。

5. **设备绑定**:驱动程序绑定到特定设备,建立起与硬件通信的逻辑联系。

```c

// 示例代码块展示Linux内核模块加载函数

static int __init pcie_driver_init(void) {

// 初始化代码,包括资源分配和设备发现

return 0;

}

static void __exit pcie_driver_exit(void) {

// 清理代码,释放分配的资源

}

module_init(pcie_driver_init);

module_exit(pcie_driv

```

0

0