【FPGA时序约束】:Verilog代码编写与时钟域交叉分析

发布时间: 2024-12-13 22:48:42 阅读量: 3 订阅数: 7

参考资源链接:[VScode与Modelsim集成:Verilog语法检测与编译教程](https://wenku.csdn.net/doc/4qyiawk9aw?spm=1055.2635.3001.10343)

# 1. FPGA时序约束基础

## 1.1 时序约束的必要性

在FPGA设计中,时序约束是确保数字电路按照预期运行的关键步骤。时序约束指导布局和布线工具如何满足设计的时序要求,例如设置频率、定义时钟域、和指定I/O延时等。合理的时序约束能够减少信号在逻辑门和互连之间的延迟,并避免时钟域之间的潜在冲突。

## 1.2 时钟定义和应用

时钟是同步数字电路的心脏,因此正确地定义和应用时钟约束是至关重要的。在FPGA时序约束中,定义时钟域包括指定时钟源、时钟频率、以及在多个时钟域之间交互时如何处理信号。此外,还需要了解时钟的偏斜(Skew)、不确定性(Uncertainty)和多周期路径(Multi-Cycle Paths)的概念。

## 1.3 基本时序约束语法

FPGA设计工具(如Xilinx的Vivado或Intel的Quartus)提供了一套时序约束语言,通常基于Synopsys Design Constraints (SDC)。以下是一些基本时序约束语句的示例:

```tcl

# 设置时钟

create_clock -period 10.0 -name sys_clk [get_ports clk]

# 设置输入延时

set_input_delay -max 4.0 -clock sys_clk [get_ports data_in]

# 设置输出延时

set_output_delay -min -3.5 -max 2.5 -clock sys_clk [get_ports data_out]

```

这些约束有助于综合工具对电路进行优化,确保在给定的时钟周期内满足所有的时序要求。随着章节深入,我们将探索更多高级时序约束技术及其实践。

# 2. Verilog代码编写指南

## 2.1 Verilog语法基础

### 2.1.1 数据类型与信号

在Verilog中,数据类型定义了信号的存储方式和它能表示的数据范围。基本的数据类型包括:

- `wire`:连续赋值语句中使用的信号,代表连续的物理连线。

- `reg`:在`always`块中被赋值的信号,代表寄存器。

- `integer`:整数类型,通常用于计数器或循环。

- `real`和`realtime`:浮点类型,用于模拟真实的时间和数值。

- `supply0`和`supply1`:特殊的供电类型,分别代表逻辑0和逻辑1。

数据类型的选择会影响后续的信号处理和优化。以下是信号声明的例子:

```verilog

wire [3:0] a, b; // 4位宽的线网a和b

reg [7:0] out; // 8位宽的寄存器out

```

### 2.1.2 模块与接口

Verilog采用模块化设计,每个模块都具有特定的接口和功能。模块是基本的设计单位,可以描述为组合逻辑或时序逻辑。模块的结构包括端口列表(port list)、内部信号声明、逻辑行为描述等。

一个简单的Verilog模块例子:

```verilog

module adder (

input wire [3:0] a, b, // 输入信号a和b

input wire cin, // 进位输入

output wire [3:0] sum, // 输出和sum

output wire cout // 进位输出

);

// 在这里实现加法器的逻辑

endmodule

```

在这个模块中,我们定义了两个4位宽的输入线网`a`和`b`,一个输入进位`cin`,以及4位宽的输出和`sum`和一个输出进位`cout`。

## 2.2 Verilog设计实践

### 2.2.1 组合逻辑设计

组合逻辑设计是基于当前输入值计算输出的逻辑电路设计。在Verilog中,组合逻辑的实现依赖于`assign`语句或`always @(*)`块。下面是一个简单的组合逻辑例子:

```verilog

module mux2to1 (

input wire [3:0] a, b, // 输入a和b

input wire sel, // 选择信号

output reg [3:0] out // 输出

);

always @(*) begin

if(sel) out = b; // 当sel为1时,选择b作为输出

else out = a; // 否则选择a作为输出

end

endmodule

```

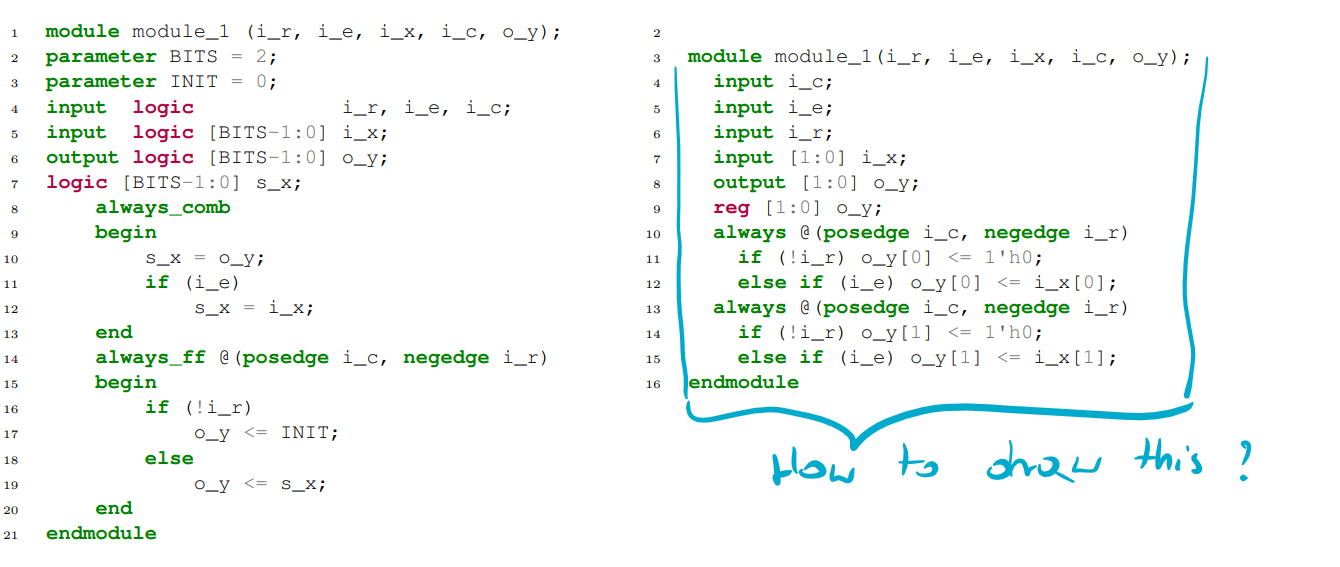

### 2.2.2 时序逻辑设计

时序逻辑设计涉及时钟信号,并且输出不仅依赖于当前的输入值,还依赖于之前的输入值和状态。时序逻辑在Verilog中通常使用`always @(posedge clk)`或`always @(negedge clk)`块来描述。下面是一个触发器的例子:

```verilog

module dff(

input wire clk, // 时钟信号

input wire rst_n, // 复位信号,低电平有效

input wire d, // 数据输入

output reg q // 输出

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

q <= 1'b0;

else

q <= d; // 在时钟上升沿,将d的值赋给q

end

endmodule

```

## 2.3 Verilog代码优化技巧

### 2.3.1 代码可读性提升

提升代码可读性可以帮助维护和调试。一些技巧包括:

- 使用清晰的命名规范。

- 恰当地使用注释。

- 遵循模块化设计原则。

- 使用参数化和生成语句。

例如,使用参数化的代码块,可以增强代码的灵活性和可重用性。

```verilog

module mux4to1 #(

parameter WIDTH = 8

)(

input wire [WIDTH-1:0] a, b, c, d,

input wire [1:0] sel,

output reg [WIDTH-1:0] out

);

//

```

0

0