掌握74LS90:时序电路设计与稳定性分析的关键

发布时间: 2024-11-29 19:23:07 阅读量: 6 订阅数: 10

参考资源链接:[74LS90引脚功能及真值表](https://wenku.csdn.net/doc/64706418d12cbe7ec3fa9083?spm=1055.2635.3001.10343)

# 1. 数字逻辑与74LS90概述

## 1.1 数字逻辑的基本原理

数字逻辑是现代电子电路设计的基石,其涉及使用离散的信号,通常为高电平和低电平(分别表示1和0),来进行逻辑运算。数字电路的这种性质使其非常适合处理二进制数据,这在计算机科学和信息技术领域是至关重要的。数字逻辑电路的典型示例包括逻辑门(AND、OR、NOT等),这些门构成了更复杂的电路和处理器的基础。

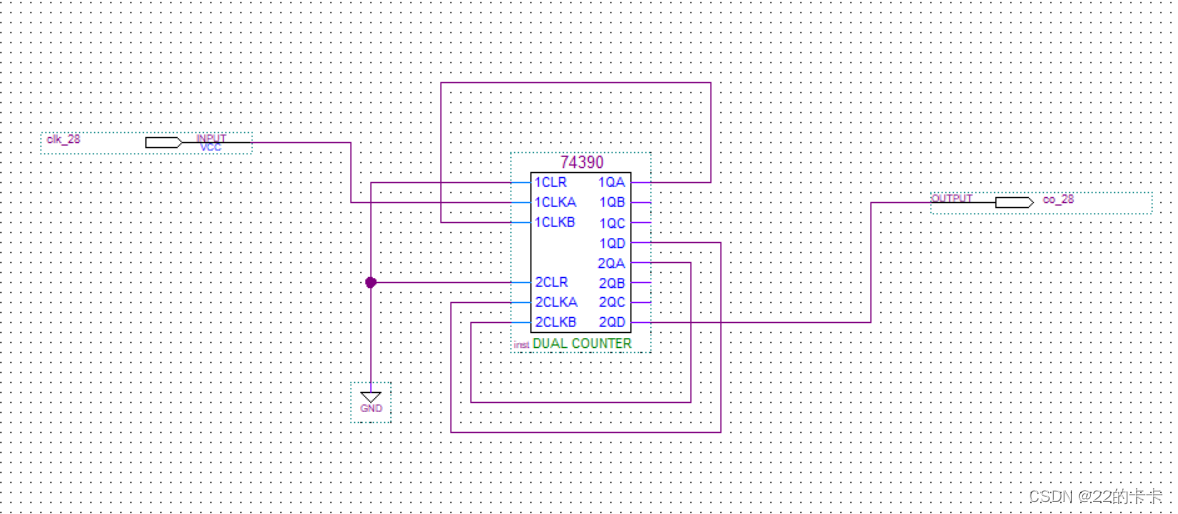

## 1.2 74LS90集成电路简介

74LS90是一款广泛使用的中规模集成(MSI)数字电路芯片,它是由德州仪器(Texas Instruments)等公司生产的双十进制计数器。它属于74系列逻辑芯片的一部分,具有低功耗肖特基(Low Power Schottky)特性,这使得它在速度与功耗之间的平衡非常优异。74LS90可以配置为各种计数模式,是学习数字逻辑和时序电路设计的理想选择。

# 2. 74LS90的基本功能与特性

## 2.1 74LS90的内部结构

### 2.1.1 触发器与计数单元

74LS90是一个包含两个独立的4位二进制计数器的集成电路,具有内部的触发器以及计数单元。每个计数器都可以被配置为二进制计数器或十进制计数器,取决于其引脚的配置方式。触发器是构成数字电路的基本单元,它在数字电路中用于存储一位信息,并且可以通过时钟信号来改变状态。

在二进制计数器中,触发器的每一位代表一个数位,输出则是二进制的序列。例如,当触发器从0000计数到1111时,便完成了从0到15的计数。每个计数器在内部都由多个JK触发器构成,这些触发器通过特定的逻辑门来确保计数的正确性。

在设计时,了解计数器的内部触发器配置对设计有效、高效的数字电路至关重要。了解触发器的特性,如触发方式、存储能力等,能够帮助我们更好地利用74LS90实现复杂的功能。

```mermaid

graph LR

A[输入脉冲] -->|上升沿| B(JK触发器)

B -->|Q输出| C[下一个触发器]

B -->|Q'输出| D[下一个触发器]

C -->|触发器链| E[计数输出]

D -->|触发器链| E[计数输出]

```

### 2.1.2 异步清零与置数功能

74LS90具备重要的控制功能,包括异步清零和置数。这些功能在电路设计中非常关键,尤其是在需要在特定时刻重置计数器或将计数器置入特定状态时。异步清零是指计数器可以在不受时钟信号影响的情况下,通过将特定的引脚(通常是R0_1和R0_2)置为低电平,瞬间将所有的计数位重置为零。

置数功能则允许用户为计数器设置一个初始的值,这通常是通过设置P0_1到P0_4引脚来实现的。这些功能的实现,在设计有特定启动或结束条件的电路时显得尤为重要。

```mermaid

graph LR

A[异步清零信号] -->|低电平| B[清零触发器]

B -->|输出| C[计数器复位]

A1[置数信号] -->|高电平| D[置数触发器]

D -->|输入| E[设置初始值]

E -->|输出| F[计数器初始设置]

```

## 2.2 74LS90的工作模式

### 2.2.1 二进制计数与十进制计数

74LS90具备在二进制和十进制模式下工作的能力,这是通过其内部的逻辑电路和特定的引脚配置实现的。在二进制模式下,每个触发器代表一个二进制位,电路能够计数从0到15的二进制数。在十进制模式下,计数器配置为能够进行十进制的计数(0-9),使用了特殊的解码逻辑来绕过不合法的二进制状态(如1010-1111),避免错误的计数。

了解74LS90的工作模式,可以帮助工程师选择合适的配置,实现诸如计时、频率分频等应用。例如,在需要分频器时,可以选择将计数器配置为10进制模式,每个计数周期结束时产生一个输出脉冲,实现对输入信号的10分频。

### 2.2.2 分频器应用案例

以74LS90设计分频器是一个典型应用,分频器是数字电路中的一种常用组件,用于产生较低频率的输出信号。在设计分频器时,可以通过将74LS90配置为二进制或十进制计数模式,根据需要来选择适当的计数周期。

例如,如果我们需要一个能够将输入信号频率降低4倍的分频器,我们可以配置74LS90工作在二进制模式,并使计数器只计数到1001(二进制表示的9),这样每当计数器达到9并回滚到0时,输出一个脉冲信号,完成4分频。

在设计分频器时,要特别注意计数器的进位输出(carry-out)和时钟输入之间的逻辑关系,确保正确的分频比和同步时序。

```mermaid

graph LR

A[输入信号] -->|分频器| B[74LS90]

B -->|二进制模式| C[计数至9]

C -->|回滚至0| D[输出脉冲]

D -->|4分频| E[输出信号]

```

## 2.3 74LS90的电气参数

### 2.3.1 供电与电源要求

74LS90的供电需求是一个必须考虑的因素,因为它决定了电路的稳定性和可靠性。74LS90通常使用+5伏的直流电源供电,这个电压需要稳定,避免电源噪声干扰。供电电流的需求不高,但是它和环境温度、电路中其他元件的功耗以及74LS90的工作状态都有关系。

在使用74LS90时,要确保电源电压在规定的范围内,否则可能会导致电路性能不稳定或者损害元件。在设计电源电路时,还需要考虑去耦电容的添加,它可以在一定程度上过滤掉电源线上的噪声,确保电源的干净和稳定。

### 2.3.2 输出电流与电压特性

输出电流是另一个关键的电气参数,它定义了74LS90可以提供的最大驱动电流。对于大多数应用,74LS90能够驱动一定数量的LED或TTL负载,但是其输出电流能力是有限的。输出电压特性描述了74LS90在不同负载下的输出电压水平,这对逻辑电平的识别是关键。

在一些特定的应用场景下,比如驱动更大的负载,可能需要外部晶体管或缓冲器来增强驱动能力。了解74LS90的电压和电流限制,可以帮助设计者选择合适的外围电路,从而优化整体电路设计的性能和可靠性。

表格中总结了74LS90的电气参数,为工程师们提供了一个快速参考点,以确保在设计时能正确处理这些关键参数。

| 参数名称 | 符号 | 最小值 | 典型值 | 最大值 |

| --------------- | ---- | ------ | ------ | ------ |

| 供电电压 | Vcc | +4.75V | +5.00V | +5.25V |

| 输出电流(高电平) | Ioh | -0.4mA | - | -20mA |

| 输出电流(低电平) | Iol | 8mA | - | 16mA |

| 输入电流

0

0