VHDL 实现电子闹钟设计与功能解析

"该资源是关于使用VHDL设计电子闹钟的教程,涵盖了开发流程、功能需求、系统结构和设计流程。项目来自福建师范大学数学与计算机科学学院的电子信息科学与技术专业,由学生花和尚完成。设计包括时间调整、24小时制显示、LCD显示、闹钟触发和分频器等多个模块。"

在VHDL中设计电子闹钟是一项综合性的数字系统设计任务,涉及到硬件描述语言的基础知识和实际应用。VHDL是一种广泛用于FPGA(Field-Programmable Gate Array)和ASIC(Application-Specific Integrated Circuit)设计的编程语言。以下是该设计中的关键知识点:

1. **基本功能**:

- **时间调整**:允许用户设置和修改当前时间和闹钟时间。

- **24小时制**:系统遵循24小时制的时间表示,这需要在计时逻辑中进行编程。

- **LCD显示**:通过1602LCD显示器显示时间,需要编写LCD驱动代码来控制显示内容。

- **闹钟触发**:在设定的时间点产生1KHz的脉冲,可以作为音频或其他提醒信号的触发源。

- **闪烁提示**:在调整时间时,相关位置应闪烁,提供用户友好的交互体验。

2. **系统结构**:

- **按键接口**:使用三个按键,分别为复位、选择和调整,用于控制和交互。

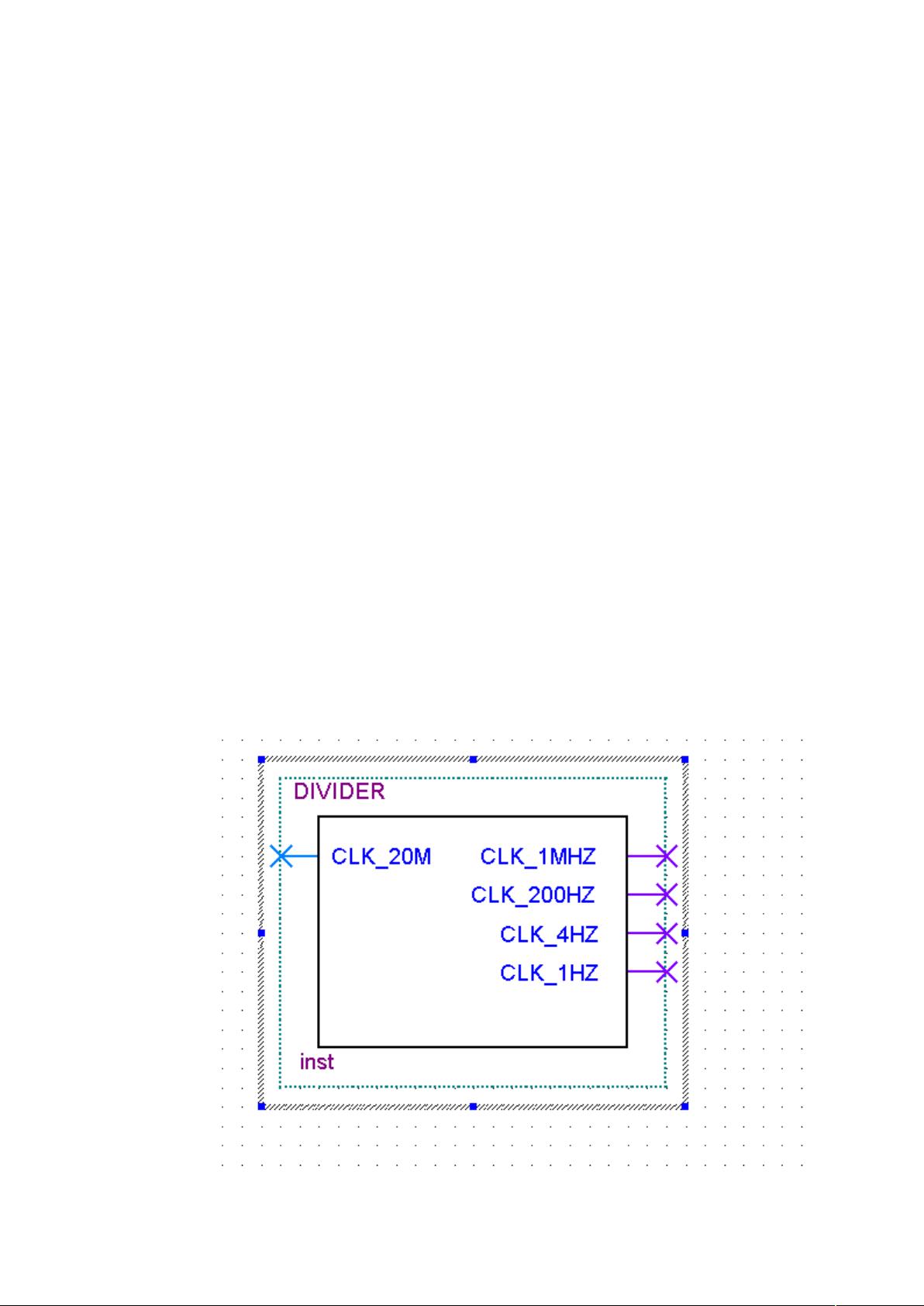

- **模块化设计**:包括抖动消除、分频、时间计时、闹钟时间设定、译码控制和LCD1602驱动等六个模块,每个模块负责特定功能。

- **输入/输出信号**:四个输入(包括按键和时钟)和五个输出(包括闹钟信号和LCD接口),这些信号在顶层文件中定义和连接。

3. **设计流程**:

- 开发流程通常涉及设计规格、逻辑模块化、VHDL编码、仿真验证、硬件实现和测试。

- 分频器是关键组件,输出四种不同频率的信号,例如1MHz、2000Hz、4Hz和1Hz,用于不同功能,如秒计时、闪烁控制等。

4. **VHDL代码**:

- 代码示例展示了顶层实体`ALARMER_TOP`的声明,包括输入和输出端口,以及使用`CLEAR_TOP`组件进行分频。

- `IEEE`库被引用,提供了必要的标准逻辑类型和包,如`STD_LOGIC_1164`和`STD_LOGIC_UNSIGNED`。

5. **操作说明**:

- 加电后,通过按键进行操作,例如按选择键查看作者信息,按复位键启动闹钟。

这样的设计不仅锻炼了学生的VHDL编程技能,还涵盖了数字逻辑、嵌入式系统和人机交互等多方面的知识,是电子工程教育中的典型实践项目。

2008-12-09 上传

2022-09-14 上传

2012-07-07 上传

2022-09-20 上传

2011-01-15 上传

2012-09-24 上传

Monk_kui

- 粉丝: 0

- 资源: 5

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍