探索编码译码与组合逻辑电路:实验与原理解析

需积分: 17 108 浏览量

更新于2024-07-31

收藏 1.02MB PDF 举报

本实验报告主要探讨了编码译码和组合逻辑电路的基本概念与设计,针对的是电子与通信专业学生。实验分为两个部分:编码器和译码器的设计与验证。

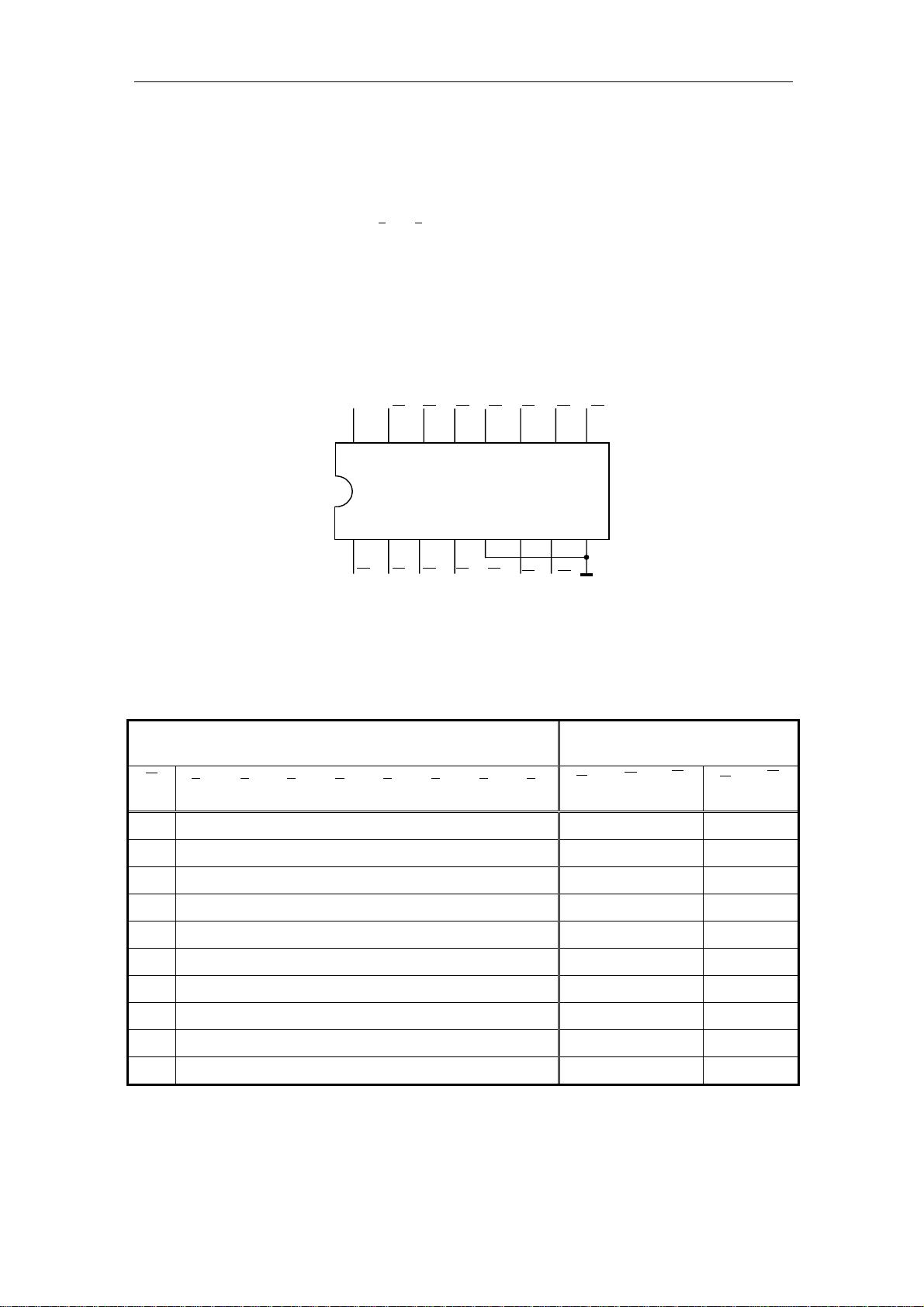

首先,实验目的是让学生深入了解编码器的工作原理和逻辑功能。编码器,特别是优先编码器,如74LS148,是一种将输入的二进制信号转换为指定输出代码的电路。8线-3线优先编码器如图2.2-2所示,它的引脚包括输入端口I0-I7,输出端口Y0-Y2,以及控制信号如EI和控制输入A0-A2。通过这个实验,学生能够学习如何根据输入信号生成不同的编码输出。

接着,实验引入了译码器,以74LS138为例,这是一种3线-8线的译码器。3线输入(A、B、C)对应8路输出(Y0-Y7),如图2.2-3所示。这个电路的主要作用是将输入的二进制代码解码为原始信号。通过实践,学生会掌握译码器如何根据接收到的代码选择性地点亮特定的输出路径。

实验所需的器材包括通用实验板、输入逻辑电平开关、发光二极管逻辑电平指示组件、可调直流稳压电源、万用表以及函数信号发生器等工具,这些都是构建和测试这些逻辑电路的关键设备。

整个实验设计旨在通过实际操作,使学生掌握编码器和译码器的硬件实现,理解它们在数据处理和通信系统中的应用,同时提升他们的逻辑思维能力和电路分析技能。通过这个过程,学生不仅能加深对二进制编码理论的理解,还能提高动手能力,为后续深入学习数字电路和系统设计打下坚实的基础。

660 浏览量

165 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

165 浏览量