Verilog HDL序列检测器与86数码管显示实验详解

需积分: 35 72 浏览量

更新于2024-07-15

2

收藏 1.47MB DOCX 举报

本次实验文档主要涉及两个核心部分:Verilog HDL语言下的序列检测器设计以及数码管控制与显示模块。首先,我们来看序列检测器部分:

1. 实验目的:

通过此实验,学生将深入理解并实践Verilog HDL的使用,包括状态机的设计和Modelsim软件的仿真。目标是实现一个能从数字码流中识别特定序列1001_0101的检测器,输入X为数字码流,输出Z在检测到指定序列后由低电平变为高电平。LED灯被用来实时反馈输出状态变化。

2. 设备与软件:

所需设备包括一台计算机,软件工具包括QuartusII 13.0.1用于硬件描述语言设计,以及Modelsim Altera Starter Edition 10.1d进行行为级仿真。

3. 实验内容:

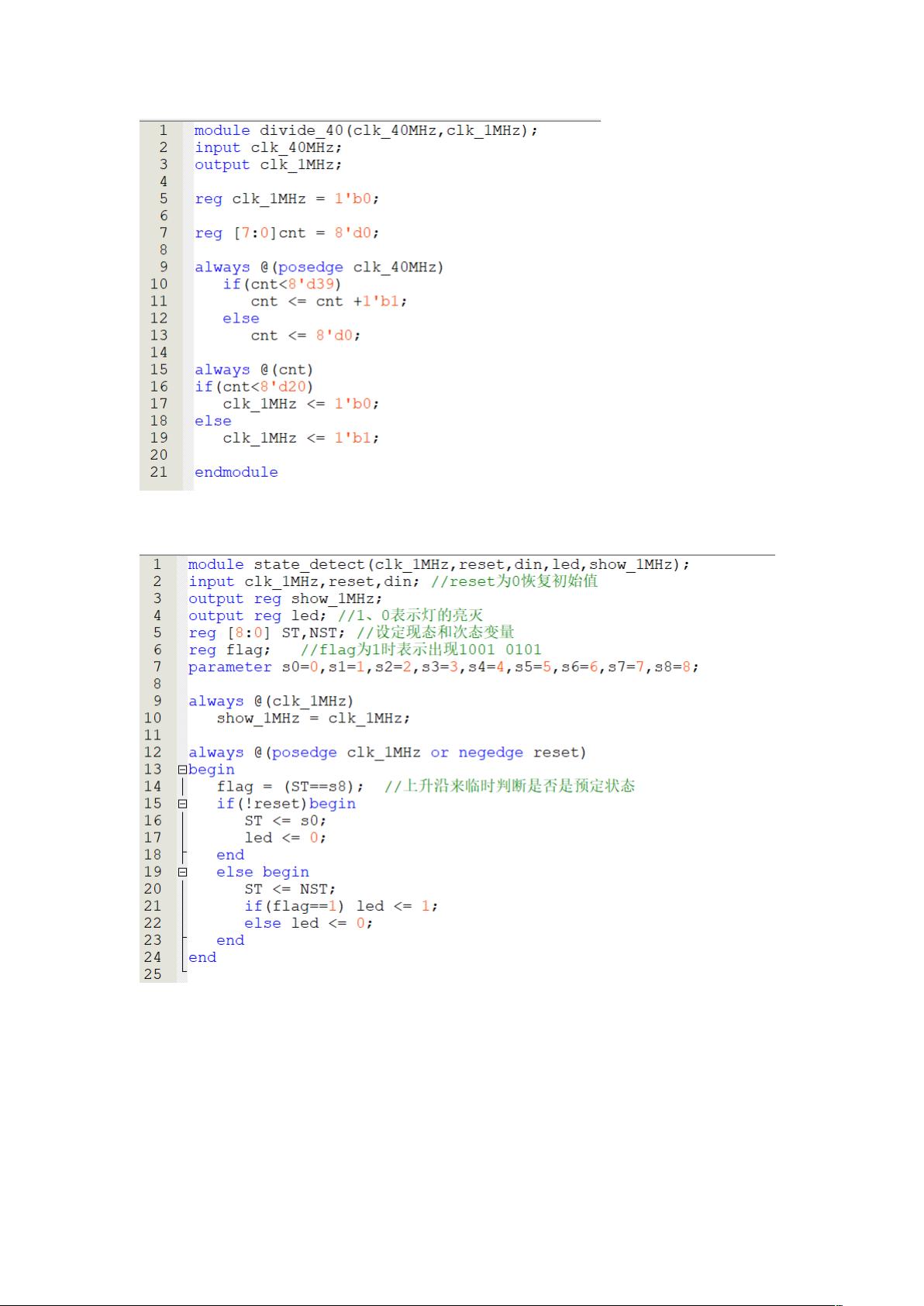

利用状态机设计,具体实现步骤包括编写divide_40.v模块(40分频),state_detect.v模块(序列检测逻辑),以及顶层文件sequence_detect.v中的集成和编译。在这个过程中,需要解决语法错误,调整电路设计以满足1us的码流速率。

4. 实验步骤:

- 编写并测试divide_40.v,实现40MHz输入时钟的40分频。

- 设计state_detect.v,定义状态转移表和触发条件,以实现“1001_0101”序列的检测。

- 在顶层文件中,连接分频模块和序列检测器,确保信号传递正确。

- 仿真阶段分为前后两步,先进行前仿真检查逻辑正确性,后进行后仿真观察实际波形和验证功能。

数码管控制与显示模块部分同样重要:

2.1 实验目标:

学习如何控制两个数码管显示数字86,提升对硬件接口和驱动的理解。

2.2 设备与软件:

相同的硬件和软件配置,可能需要针对数码管控制的额外驱动代码。

2.3 实验内容:

设计并实现数码管的驱动模块,以及与序列检测器结合的显示逻辑。

2.4 实验步骤:

- 创建或修改必要的驱动模块,确保能够准确地控制数码管显示86。

- 将驱动模块与序列检测器的结果结合,实现特定条件下显示功能。

2.5 仿真分析:

数码管控制的仿真分析与序列检测器类似,分为前仿真检查驱动代码是否符合预期,后仿真确认实际显示效果。

总结与收获:

通过这两个部分的实验,学生不仅能够巩固Verilog HDL编程技能,还能提升状态机设计和硬件系统集成的能力。同时,实际的LED和数码管应用也锻炼了学生的硬件调试和系统集成实践经验。通过模型的仿真验证,学生可以更好地理解和优化电路行为,为未来从事嵌入式系统设计打下坚实基础。

2022-06-20 上传

2022-10-21 上传

2022-11-29 上传

2021-04-10 上传

2020-07-09 上传

2022-06-20 上传

2022-07-01 上传

2022-06-30 上传

长安忆往昔如梦

- 粉丝: 3

- 资源: 10

最新资源

- 过滤器返冲洗控制程序.rar

- mod5

- ImgHosting:图片托管

- 云原生架构白皮书.zip

- 行业文档-设计装置-一种可充气变形省空的书架.zip

- TPFinal_IngSoftware2020_UCEL:在Web的Aportes Tecso仓库创建证书,在UCEL的Ingenieria软件工程2020版最终发布

- LP2

- node-sqs-processor:SQS队列处理模块

- 三系列浓相输送监控系统设计与实现

- Accuinsight-1.0.35-py2.py3-none-any.whl.zip

- node-servoblaster:用于 Node.js 的 ServoBlaster 库

- fb41源程序.rar

- git-json-api:通过HTTP从Git存储库中的JSON文件中获取内容(以及POST更改)

- 调试

- assignment

- weixin052用于日语词汇学习的微信小程序+ssm后端毕业源码案例设计