FPGA实现的LS波段宽带步进频率信号源设计与集成

178 浏览量

更新于2024-09-01

6

收藏 277KB PDF 举报

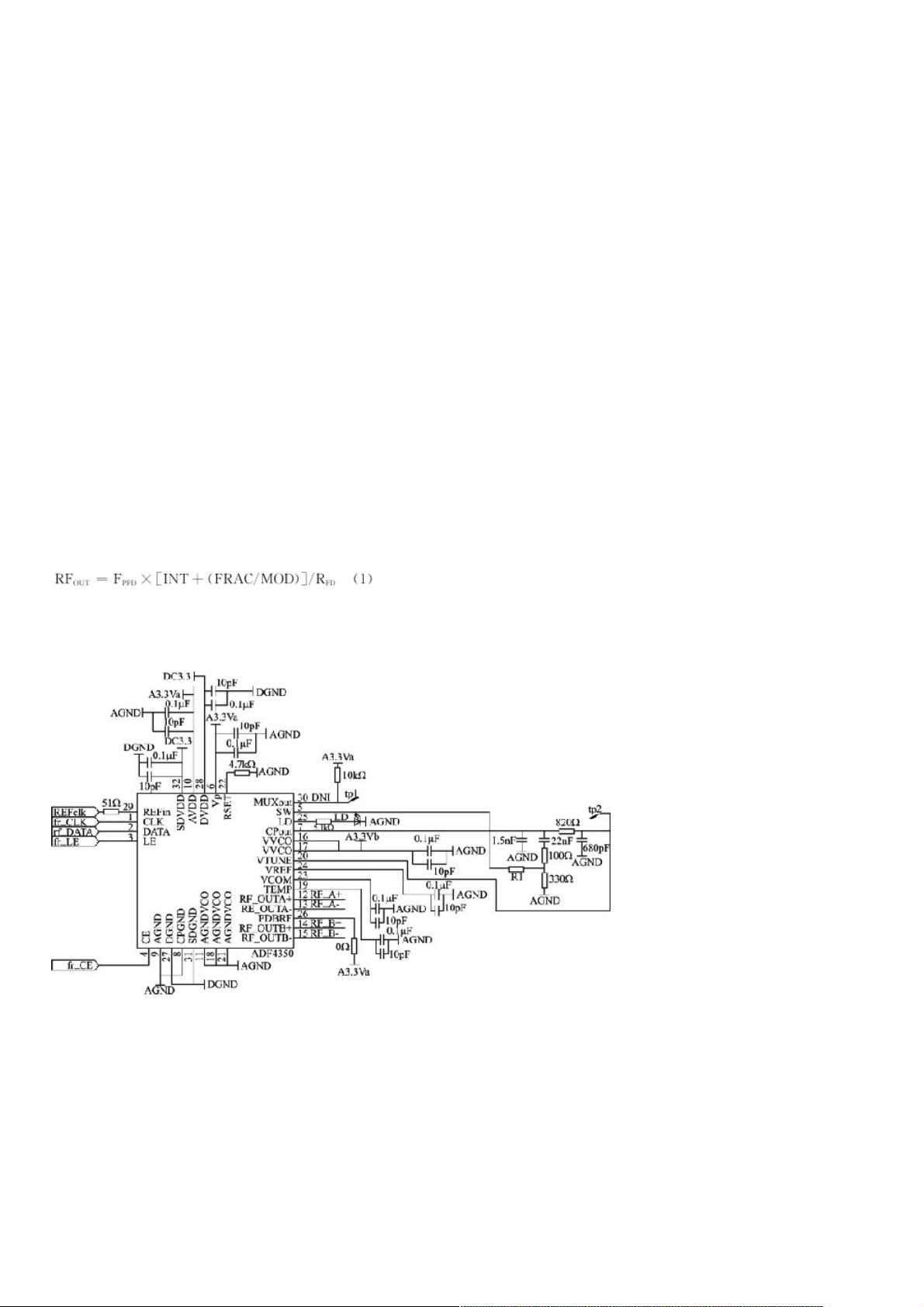

本文主要探讨了基于FPGA的宽带步进频率信号源的设计方法。该设计巧妙地融合了直接数字频率合成器(DDS)和锁相环(PLL)芯片的优点,如ADI公司生产的ADF4350宽带频率合成器,它内置了VCO、鉴相器、电荷泵和分频器等功能,提供了宽广的频率范围,从2200MHz至4400MHz,且支持小数和整数分频。通过Xilinx公司的Spartan3系列FPGA进行系统集成和时序控制,使得设计的信号源能够在LS波段实现高性能和低噪声杂散。

频率合成器的核心是ADF4350芯片,它的工作原理是利用外部提供的参考频率fREF,通过内部R分频器后驱动鉴相器,形成鉴相参考频率FPFD。射频输出RFOUT经过N分频后得到的反馈频率FN与FPFD进行比较,产生与相位差成比例的脉冲,由电荷泵转化为携带误差信息的电流。这个电流经过外部环路处理,最终调整VCO的输出频率,实现频率的精确控制。

设计中,FPGA的灵活性和可编程性使得可以根据需求灵活配置和控制频率源的输出,确保输出频率的准确性,同时克服了DDS在宽频带实现上的挑战,以及PLL可能存在的相位噪声和杂散问题。这样的设计不仅提升了信号源的性能,还提高了整个系统的稳定性,特别适用于通信和雷达系统等领域。

通过本文的详细介绍,读者可以了解到如何利用FPGA技术优化步进频率信号源的设计,包括硬件选择、控制策略和实际应用中的优势,为相关领域的研究和实践提供了有价值的参考。

2021-07-13 上传

159 浏览量

177 浏览量

125 浏览量

125 浏览量

125 浏览量

582 浏览量

404 浏览量

点击了解资源详情

weixin_38659646

- 粉丝: 3

最新资源

- Openaea:Unity下开源fanmad-aea游戏开发

- Eclipse中实用的Maven3插件指南

- 批量查询软件发布:轻松掌握搜索引擎下拉关键词

- 《C#技术内幕》源代码解析与学习指南

- Carmon广义切比雪夫滤波器综合与耦合矩阵分析

- C++在MFC框架下实时采集Kinect深度及彩色图像

- 代码研究员的Markdown阅读笔记解析

- 基于TCP/UDP的数据采集与端口监听系统

- 探索CDirDialog:高效的文件路径选择对话框

- PIC24单片机开发全攻略:原理与编程指南

- 实现文字焦点切换特效与滤镜滚动效果的JavaScript代码

- Flask API入门教程:快速设置与运行

- Matlab实现的说话人识别和确认系统

- 全面操作OpenFlight格式的API安装指南

- 基于C++的书店管理系统课程设计与源码解析

- Apache Tomcat 7.0.42版本压缩包发布