Quartus与Modelsim SE 10联合仿真全面指南

需积分: 38 191 浏览量

更新于2024-07-15

1

收藏 1.35MB DOCX 举报

"这篇文档是关于如何使用quartus ii与Modelsim SE 10进行联合仿真的详细教程,涵盖了从设置Modelsim路径到优化仿真速度,再到ROM仿真设置和下载流程的全部步骤。"

在FPGA设计中,联合仿真是一项重要的任务,它允许开发者在硬件实现之前验证设计的正确性。Quartus II是一款由Altera(现Intel FPGA)提供的综合、适配、编程和调试工具,而Modelsim是一款强大的硬件描述语言(HDL)仿真器,支持VHDL和Verilog。本文档详述了如何有效地将这两者结合使用,以提高仿真效率。

首先,要设置Modelsim SE 10.0c的路径。在Quartus II的Tools菜单中选择Options,然后在选项窗口中设置Modelsim的路径,通常是在安装目录下的win32子目录。确保正确配置后点击OK以保存设置。

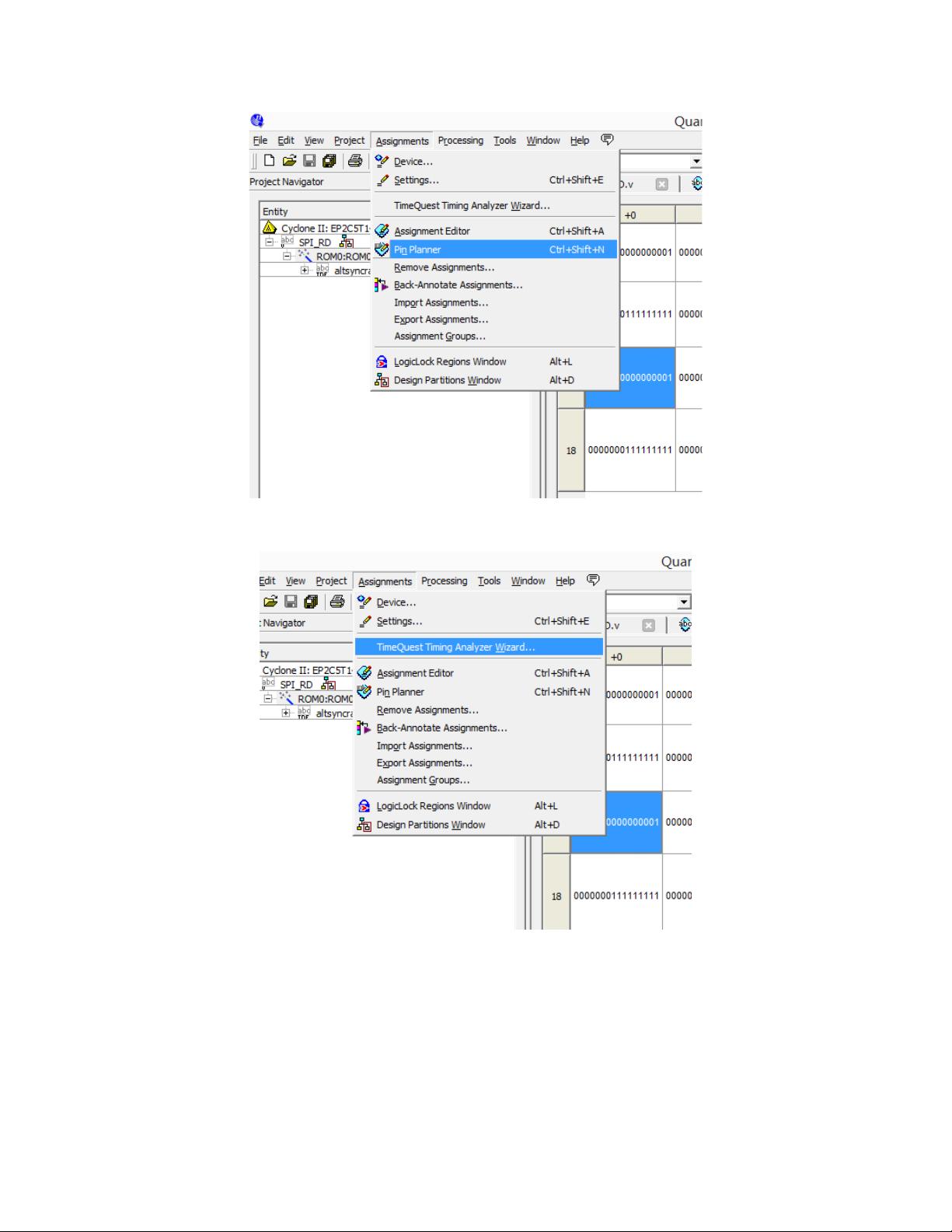

接着,新建Quartus II工程并进行设计。设计完成后,需要进行仿真设置,包括分配引脚、设定简单的时序约束,以及综合布局布线。引脚分配是确保设计与实际FPGA硬件接口匹配的关键步骤。时序约束则用于确保设计满足性能要求。

为了进行联合仿真,需要自动生成并编辑testbench文件。Quartus II会自动在工程文件夹下创建一个Modelsim子文件夹,其中包含仿真所需的文件。打开.textbeach.vt文件,根据提示设置仿真参数,包括测试文件名、顶层文件名以及仿真设置。

减少库的编译是提高仿真速度的有效手段。通过选择仅编译必要的库组件,可以显著缩短编译时间。在Quartus II中,将器件系列添加到编译列表,并选择相应的语言(如VHDL或Verilog),指定库的保存位置,然后开始编译。

ROM仿真也是FPGA设计中的常见需求。在本教程中,会指导用户如何设置ROM仿真,包括指定保存路径、创建.mf文件,并修改相应值以生成符合设计要求的ROM。

最后,文档还涉及了下载过程,包括添加驱动、设置未使用的引脚为输入暂态,以及选择合适的下载方式,如AS方式或JTAG方式。对于JTAG下载,如果希望设计在断电后仍能保持,可以生成.jic文件。

总结来说,这个文档为FPGA开发者提供了一套完整的Quartus II与Modelsim SE 10联合仿真实践指南,涵盖了从环境配置到设计验证,再到最终下载的全过程,对于初学者和有经验的开发者来说都是非常有价值的参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-11-13 上传

2022-11-29 上传

2022-11-13 上传

2020-12-28 上传

2022-11-03 上传

2023-04-04 上传

Laminaria

- 粉丝: 27

- 资源: 14

最新资源

- MongoDB-test-project

- Accuinsight-1.0.22-py2.py3-none-any.whl.zip

- AppBots:IIT2019053,IIT2019039,IIT2019059,IIT2019060

- 电动机星三角启动程序.rar

- PGA 排行榜抓取器:从 PGA 官方网站上的当前排行榜中抓取玩家分数-matlab开发

- 曼达

- Ignite-Trilha-ReactJS:培训期间开发的讲义和项目,重点是Rocketseat的ReactJS

- goormExploration:goormIDE的探索可用性,带宽,速度,可用工具或发行版等

- Mergely:在线合并和差异文档

- clase1_NT2

- 笔记本销售网站的ASP毕业设计(源代码+论文).zip

- 反向传播教程 - 神经网络的训练算法:关于反向传播算法的西班牙语教程。 仅用于学术和教育用途。-matlab开发

- React初始项目

- CanturkFramework:开发了完整的.Net框架结构,其中使用了许多用于OOP的技术

- 基于网络环境的库存管理系统的asp毕业设计(源代码+论文).zip

- zb-php:ZB API像官方文档界面一样,支持任意扩展