Verilog HDL基础与应用

版权申诉

DOC格式 | 258KB |

更新于2024-06-25

| 188 浏览量 | 举报

"Verilog HDL相关知识问答"

在Verilog HDL中,设计者可以利用其丰富的特性和语法来实现数字系统的设计、仿真和验证。以下是对标题和描述中涉及知识点的详细解释:

1. Verilog HDL的标准化:Verilog HDL于1995年被IEEE正式标准化,成为IEEE 1364标准,为数字系统设计提供了统一的描述语言。

2. 描述方式:Verilog HDL支持行为描述、数据流描述和结构化描述三种方式。行为描述通过过程化结构(如always块)建模;数据流描述使用连续赋值语句来描述信号的连续变化;结构化描述则通过门和模块实例来构建硬件结构。

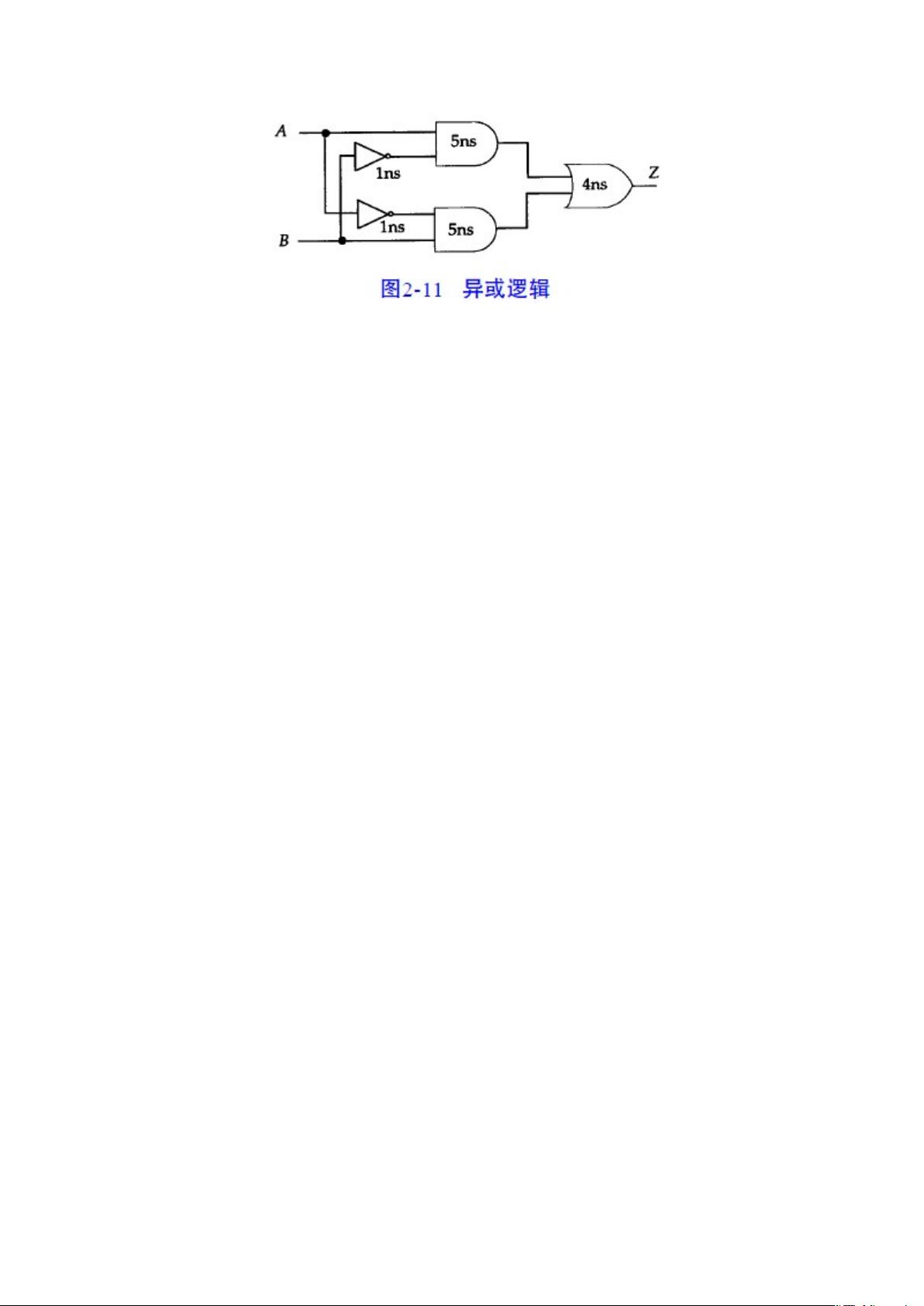

3. 时序描述:Verilog HDL可以清晰地描述设计的时序特性,包括时钟、触发器和延迟等,这对于设计时序电路至关重要。

4. 参数化设计:Verilog HDL允许在模块声明中定义参数,使得设计能够根据参数进行实例化,实现参数化设计,增强了代码的复用性和灵活性。

5. 测试验证:Verilog HDL支持编写测试激励(testbench),通过模拟输入和预期输出来验证设计的功能正确性。

6. Verilog HDL起源:该语言最初由Gateway Design Automation公司开发,后来被其他公司如Cadence Design Systems收购,并逐步发展成为行业标准。

7. 数据类型:Verilog HDL中的主要数据类型分为线网(wire)和寄存器(reg)。线网类型用于表示硬件连接,而寄存器类型用于表示存储数据的元件。

8. UDP:用户定义原语(User Defined Primitives)允许用户自定义逻辑操作,扩展了Verilog的基本功能。

9. 基本门电路:在开关级描述中,基本门通常包括PMOS(P沟道金属氧化物半导体场效应晶体管)和NMOS(N沟道金属氧化物半导体场效应晶体管)。在逻辑门层面,常见的有AND门和OR门。

10. `timescale指令:`timescale用于设置时间和延迟的单位和精度,确保仿真时的时间精度和一致性。例如`timescale 1ns/100ps表示时间单位是1ns,时间精度是100ps。

11. 过程赋值语句中的时延:在Verilog HDL中,过程赋值语句可以指定两种时延。一是语句间时延,例如在两条连续的赋值语句之间设定延迟;二是语句内时延,即表达式计算到赋值之间的延迟。

这些基础知识构成了Verilog HDL设计的基础,对于理解和编写Verilog代码至关重要。通过学习和掌握这些概念,设计者可以有效地创建、验证和实现复杂的数字系统。

相关推荐

文档优选

- 粉丝: 98

- 资源: 1万+