VHDL Testbench入门:功能验证与激励波形生成

需积分: 0 151 浏览量

更新于2024-09-11

收藏 125KB PDF 举报

本资源是一份详细的testbench入门教程,旨在帮助学习者理解和掌握如何在VHDL语言环境下使用testbench进行电路仿真。Testbench是硬件描述语言(HDL)设计中至关重要的工具,用于验证和测试电路的功能和性能。它主要通过以下几个步骤进行操作:

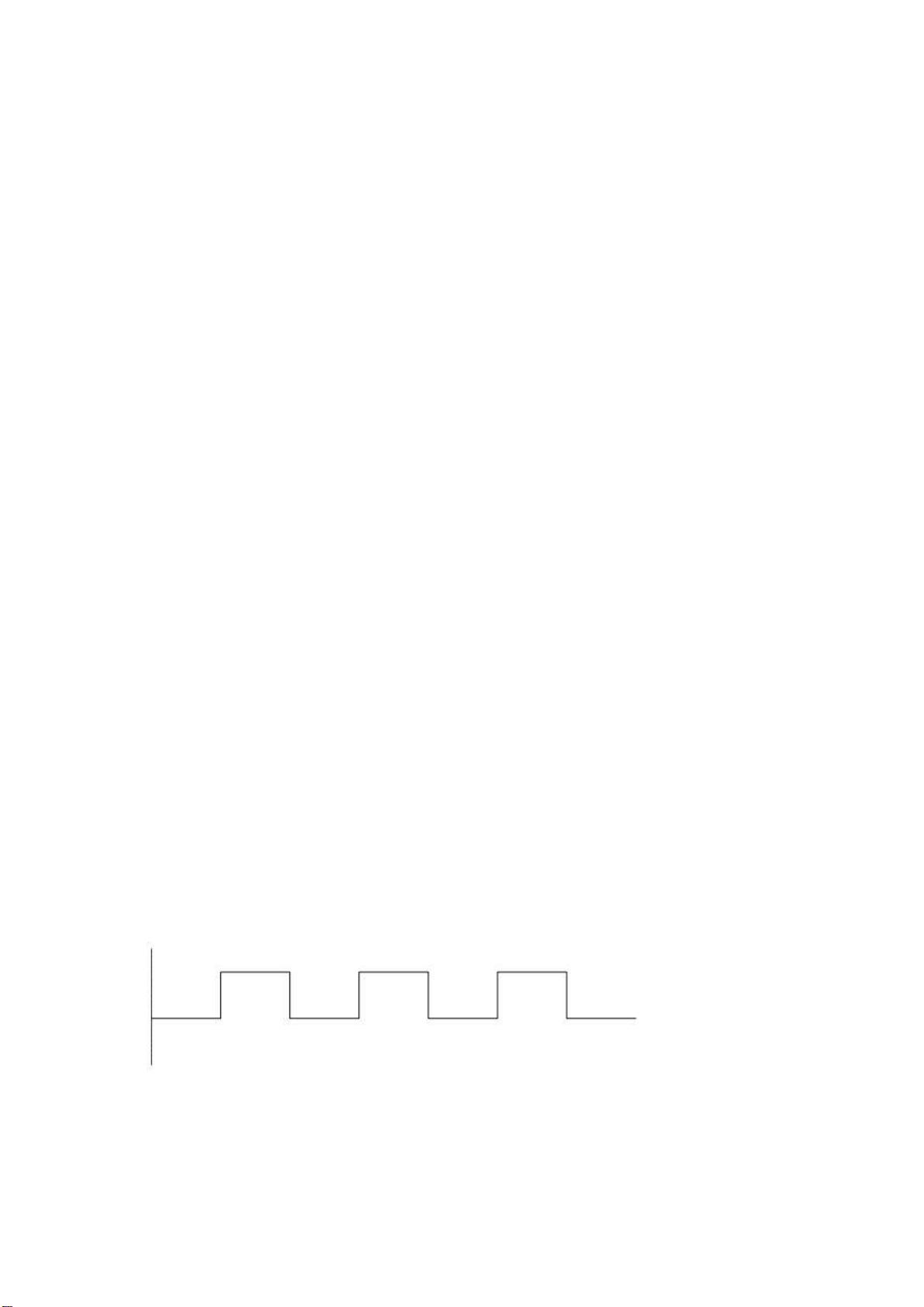

1. 编写目的:testbench的主要目标是创建模拟环境,通过模拟激励信号(如时钟和复位信号)来驱动设计的电路,并观察其响应,以检查设计是否符合预期。这个过程涉及生成特定波形,如周期性时钟和可变占空比的时钟,以及复位信号。

2. 基本结构:一个基本的testbench结构通常包含以下组件:

- `module test_bench`:顶层文件,无输入和输出端口,主要用于组织和管理测试。

- 信号或变量定义:声明用于模拟输入和监测输出的信号。

- 激励产生:使用`initial`或`always`语句来生成模拟激励,如定时的时钟和复位信号。

- 模块实例化:将待测试模块(设计模块)和激励产生模块作为实例引入到顶层文件。

- 端口连接:按照名称或位置将激励信号连接到被测模块的相应端口,通常采用名称关联方式。

3. 激励信号的产生:

- 时钟信号:可以通过不同的方法产生,如:

- 使用`initial`产生占空比50%的时钟,确保赋予初始值以避免信号处于高阻状态。

- `always`语句实现周期性的时钟翻转。

- `repeat`循环产生固定数量的时钟周期。

- 复位信号:可以设定为一次性或周期性地产生,以便控制电路的初始化状态。

本教程深入浅出地介绍了testbench的基本概念、结构以及如何使用VHDL编写实际的testbench代码。对于初学者来说,理解并掌握这些基本技巧是进行HDL设计验证的关键,能够确保电路功能的准确性和性能的优化。通过实践和不断学习,读者将能熟练运用testbench进行高效和精确的电路测试。

2024-12-26 上传

2024-12-26 上传

soooophia

- 粉丝: 0

- 资源: 1