"Verilog HDL基础与设计实例:半加器、三输入与非门和基本门原语"

版权申诉

188 浏览量

更新于2024-03-09

收藏 228KB PDF 举报

本文主要介绍了HDL语言与ASIC原理中的Verilog设计实例系列(一),其中涵盖了半加器的实现原理图和Verilog描述、三输入与非门以及五输入与非门的功能相互连接的基本门原语声明等内容。通过具体的Verilog代码示例和逻辑设计介绍,读者可以深入了解Verilog HDL的应用和实践方法。

首先,文章介绍了半加器的实现原理图和Verilog描述。半加器是一种基本的数字电路,用于对两个二进制数进行相加操作。Verilog代码中定义了一个module,输入为a和b两个信号,输出为sum和c_out分别表示加法结果和进位。通过xor门和and门的组合实现了半加器的功能。这一设计实例展示了Verilog语言编写数字电路的基本方法和技巧。

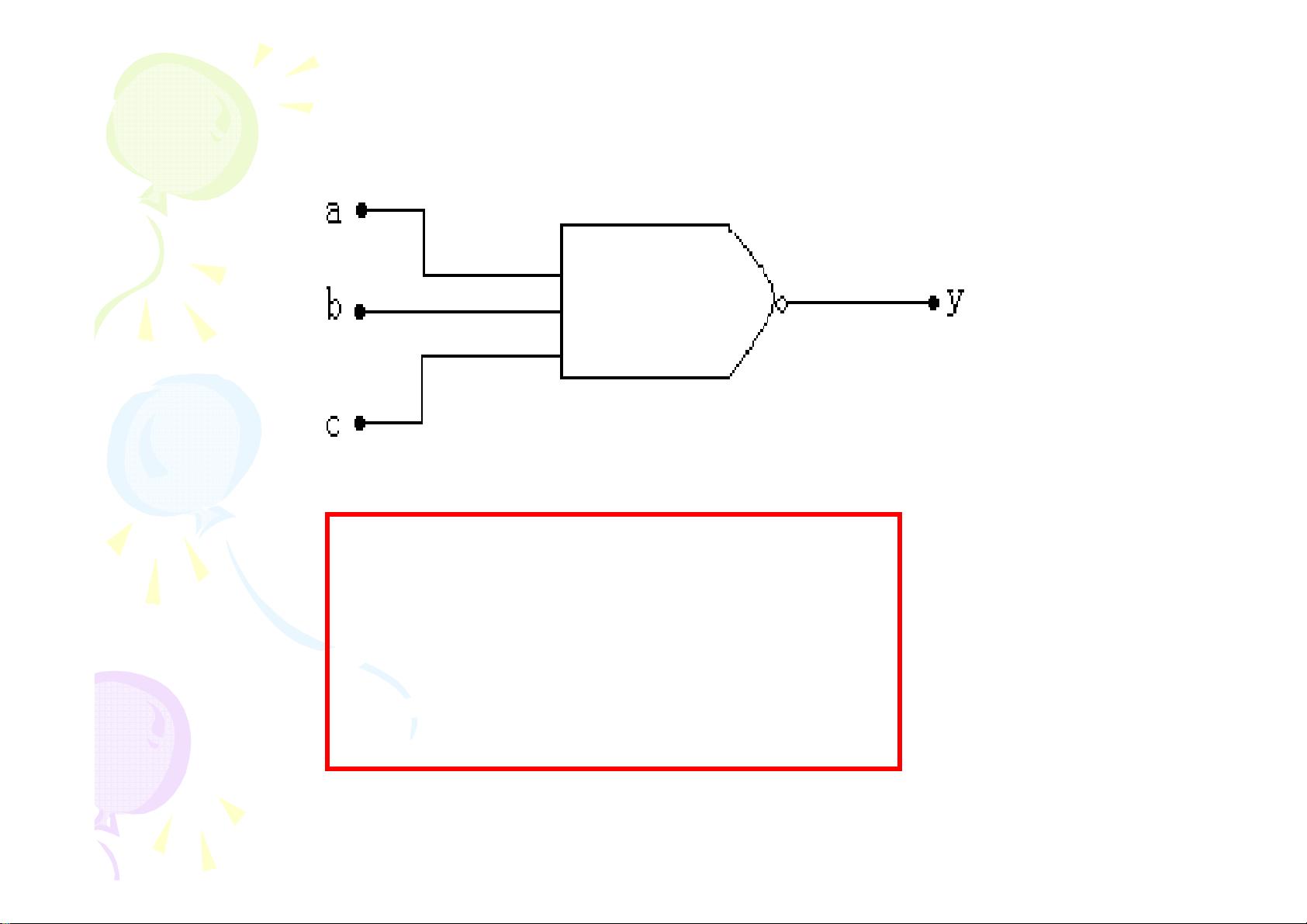

其次,文章介绍了三输入与非门的原语化举例。三输入与非门是逻辑门中的一种,常用于数字电路的设计和实现。Verilog代码中展示了nand门的实现方式,通过多个输入信号的逻辑运算实现了与非门的功能。这一实例展示了Verilog语言中使用原语化表示逻辑门的方法,有助于读者理解数字电路的逻辑设计原理。

最后,文章介绍了五输入与非门的功能相互连接的基本门原语声明。将多个五输入与非门连接在一起,可以实现复杂的逻辑功能。Verilog代码中声明了AOI门的组合连接方式,展示了多个逻辑门如何通过连接方式实现复杂的逻辑功能。这一设计实例展示了Verilog语言中如何声明和使用多个逻辑门进行逻辑功能设计,有助于读者理解数字电路中逻辑门的连接和组合方式。

总的来说,本文通过多个设计实例展示了Verilog HDL在数字电路设计中的应用方法和实践技巧。读者可以通过学习这些实例,掌握Verilog语言的基本语法和逻辑设计原理,为进一步深入学习HDL语言和ASIC原理打下坚实的基础。Verilog设计实例系列(一)是数字电路设计领域中的重要内容,通过实际的练习和实践,读者可以提高自己的数字电路设计能力,为未来的ASIC设计工作做好准备。

2021-09-21 上传

2021-09-21 上传

2022-06-18 上传

2023-05-12 上传

2023-07-16 上传

2023-07-13 上传

2023-06-26 上传

2023-07-04 上传

2024-11-01 上传

matlab大师

- 粉丝: 2734

- 资源: 8万+

最新资源

- Bubble-Up-GitHub-Accounts:观看整个 GitHub 存储库,但仅将来自特定 GitHub 用户的通知发送到您的 Gmail 收件箱

- sinatra-angularjs:带有Sinatra REST API的Angularjs的基本示例

- matlab开发-SVD刷新矩阵完成orrecommenders系统设计.zip

- 毕设项目-基于springboot开发实现的网络小说系统源码+项目说明.7z

- xyz-reader:Android Nanodegree中的XYZ Reader项目

- Block Fortress:开源突破克隆-开源

- 基于HTML实现的房地产公司手机网站手机网站模板HTML5网站(css+html+js+图样+毕业设计).zip

- BreakCalculator:英国议会辩论格式的中断计算器

- weixin060微信小程序考试系统+ssm(源码+部署说明+演示视频+源码介绍+lw).rar

- 创业计划书-2007年中国零售业趋势展望

- 多线程注册例程-易语言.zip

- AeroBenchVVPython:F-16机动验证基准的Python版本

- 华中科技大学887考研真题(2011-2019年).zip

- weixin011医院核酸检测服务系统开发+Springboot(源码+部署说明+演示视频+源码介绍+lw).rar

- Roomba Monitor-开源

- boomerang-client