FPGA加速的数字卷积加减速算法设计与高性能实现

PDF格式 | 499KB |

更新于2024-08-30

| 177 浏览量 | 举报

本文主要探讨了基于FPGA的数字卷积加减速算法的设计与实现,其核心目标是提高计算效率、稳定性和运算速度,以满足现代数控系统和工业机器人对高速和高精度控制的需求。传统软件编程的加减速算法可能存在计算量大、难以实现硬件化的缺点。

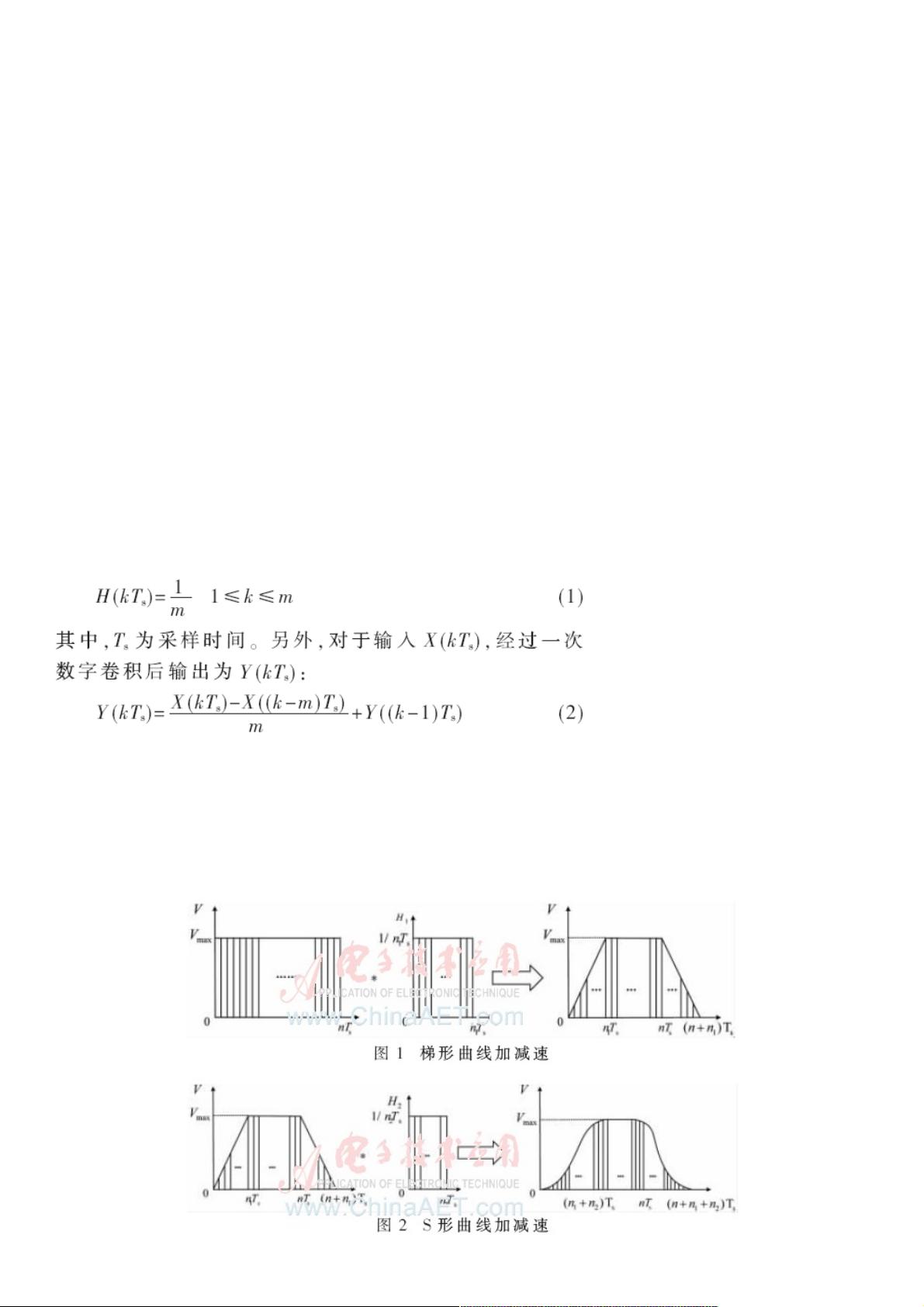

首先,作者引入数字卷积这一概念,利用其迭代表达式的特性(仅包含加法和除法运算),这使得在FPGA硬件平台上实现时,能够显著减少计算负担。数字卷积通过一次运算就能生成梯形加减速曲线,其总运行时间nTs由曲线长度与固定速度Vmax决定。通过调整卷积核H1的值,如取1/n1Ts,可以确保速度位移的一致性。

进一步地,通过两次数字卷积操作,可以得到光滑的S形加减速曲线,相比于梯形曲线,这种曲线具有更好的灵活性和动态性能。这种方式不仅简化了计算过程,还降低了速度突变带来的振动,有助于提高加工精度和整体运动控制的平滑性。

文章的关键创新在于将FIR滤波器的速度规划算法与数字卷积相结合,既实现了加减速的连续变化,又降低了计算复杂度。相较于先前的算法,这种方法在保持高性能的同时,降低了实现的难度,这对于在硬件资源受限的环境中,如FPGA,具有重要的实际应用价值。

基于FPGA的数字卷积加减速算法设计不仅优化了运动控制的性能,还降低了硬件实现的复杂性,为数控系统和工业机器人的高效、精确控制提供了新的解决方案。这种技术的发展预示着未来硬件加速的运动控制算法将更加普遍,对提升工业自动化水平有着深远影响。

相关推荐

765 浏览量

weixin_38581308

- 粉丝: 2

最新资源

- 企业人事管理系统代码:Oracle与Eclipse的完美结合

- WebDev:构建高效教育服务网站的完整指南

- 使用JSP实现的同学录管理系统功能详解

- 中英文个人简历模板集锦

- 基于51单片机的交通灯控制系统设计

- Ola-Mundo:首秀GitHub存储库,HTML课程的实践

- Office安装错误解决:缺失文件导致更新失败

- 完整贪吃蛇游戏源码分析及MFC编程实战

- 探索uC-GUI-V3-98完整源码及其文件结构

- GeoSOS地理元胞自动机:多种模拟技术实现

- Windows CE 5.0纤程编程实战与同步控制示例

- VC实现大漠插件调用编程实例解析

- 探索JavaScript中的节点概念

- 历届电子竞赛电源电路图集锦与程序汇总

- VB字符串解析方法教程与实例分析

- 掌握IIS5.0:网页开发超级管理手册精要