5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

ALINX Confidential

www.alinx.com

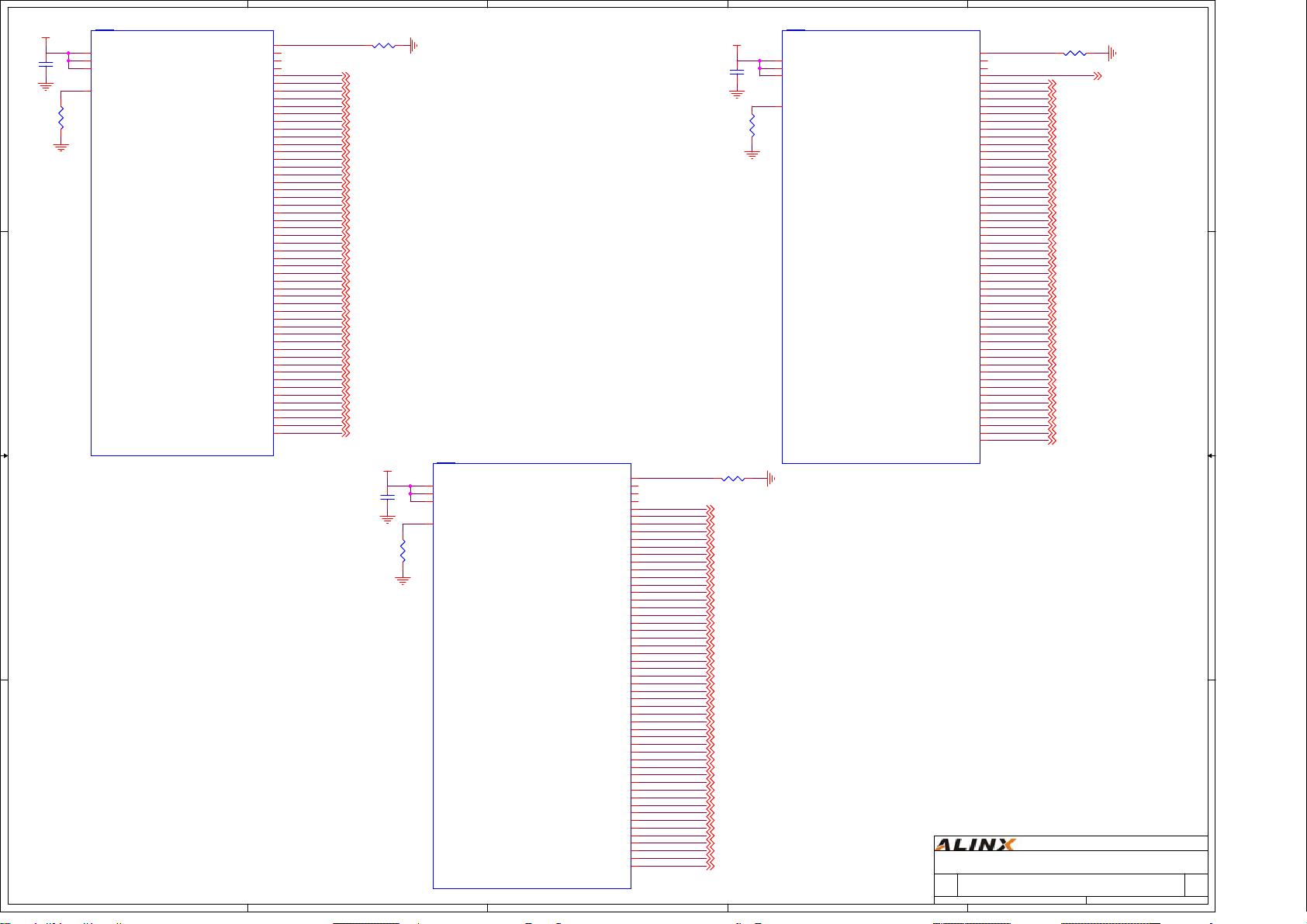

+1.8V OR +1.2V +1.8V OR +1.2V

+1.8V OR +1.2V

VRP_64

VRP_65

VRP_66

PCIE_PERSTNB64_L1_N

B64_L1_P

B64_L2_N

B64_L2_P

B64_L3_N

B64_L3_P

B64_L4_N

B64_L4_P

B64_L5_N

B64_L5_P

B64_L6_N

B64_L6_P

B64_L7_N

B64_L7_P

B64_L8_N

B64_L8_P

B64_L9_N

B64_L9_P

B64_L10_N

B64_L10_P

B64_L11_N

B64_L11_P

B64_L12_N

B64_L12_P

B64_L13_N

B64_L13_P

B64_L14_N

B64_L14_P

B64_L15_N

B64_L15_P

B64_L16_N

B64_L16_P

B64_L17_N

B64_L17_P

B64_L18_N

B64_L18_P

B64_L19_N

B64_L19_P

B64_L20_N

B64_L20_P

B64_L21_N

B64_L21_P

B64_L22_N

B64_L22_P

B64_L23_N

B64_L23_P

B64_L24_N

B64_L24_P

B65_L1_N

B65_L1_P

B65_L2_N

B65_L2_P

B65_L3_N

B65_L3_P

B65_L4_N

B65_L4_P

B65_L5_N

B65_L5_P

B65_L6_N

B65_L6_P

B65_L7_N

B65_L7_P

B65_L8_N

B65_L8_P

B65_L9_N

B65_L9_P

B65_L10_N

B65_L10_P

B65_L11_N

B65_L11_P

B65_L12_N

B65_L12_P

B65_L13_N

B65_L13_P

B65_L14_N

B65_L14_P

B65_L15_N

B65_L15_P

B65_L16_N

B65_L16_P

B65_L17_N

B65_L17_P

B65_L18_N

B65_L18_P

B65_L19_N

B65_L19_P

B65_L20_N

B65_L20_P

B65_L21_N

B65_L21_P

B65_L22_N

B65_L22_P

B65_L23_N

B65_L23_P

B65_L24_N

B65_L24_P

B66_L1_N

B66_L1_P

B66_L2_N

B66_L2_P

B66_L3_N

B66_L3_P

B66_L4_N

B66_L4_P

B66_L5_N

B66_L5_P

B66_L6_N

B66_L6_P

B66_L7_N

B66_L7_P

B66_L8_N

B66_L8_P

B66_L9_N

B66_L9_P

B66_L10_N

B66_L10_P

B66_L11_N

B66_L11_P

B66_L12_N

B66_L12_P

B66_L13_N

B66_L13_P

B66_L14_N

B66_L14_P

B66_L15_N

B66_L15_P

B66_L16_N

B66_L16_P

B66_L17_N

B66_L17_P

B66_L18_N

B66_L18_P

B66_L19_N

B66_L19_P

B66_L20_N

B66_L20_P

B66_L21_N

B66_L21_P

B66_L22_N

B66_L22_P

B66_L23_N

B66_L23_P

B66_L24_N

B66_L24_P

VCCO_64

VCCO_65

VCCO_66

PCIE_PERSTN 24B64_L1_N 25

B64_L1_P 25

B64_L2_N 25

B64_L2_P 25

B64_L3_N 25

B64_L3_P 25

B64_L4_N 25

B64_L4_P 25

B64_L5_N 25

B64_L5_P 25

B64_L6_N 25

B64_L6_P 25

B64_L7_N 25

B64_L7_P 25

B64_L8_N 25

B64_L8_P 25

B64_L9_N 25

B64_L9_P 25

B64_L10_N 25

B64_L10_P 25

B64_L11_N 25

B64_L11_P 25

B64_L12_N 25

B64_L12_P 25

B64_L13_N 25

B64_L13_P 25

B64_L14_N 25

B64_L14_P 25

B64_L15_N 25

B64_L15_P 25

B64_L16_N 25

B64_L16_P 25

B64_L17_N 25

B64_L17_P 25

B64_L18_N 25

B64_L18_P 25

B64_L19_N 25

B64_L19_P 25

B64_L20_N 25

B64_L20_P 25

B64_L21_N 25

B64_L21_P 25

B64_L22_N 25

B64_L22_P 25

B64_L23_N 25

B64_L23_P 25

B64_L24_N 25

B64_L24_P 25

B65_L1_N 25

B65_L1_P 25

B65_L2_N 25

B65_L2_P 25

B65_L3_N 25

B65_L3_P 25

B65_L4_N 25

B65_L4_P 25

B65_L5_N 25

B65_L5_P 25

B65_L6_N 25

B65_L6_P 25

B65_L7_N 25

B65_L7_P 25

B65_L8_N 25

B65_L8_P 25

B65_L9_N 25

B65_L9_P 25

B65_L10_N 25

B65_L10_P 25

B65_L11_N 25

B65_L11_P 25

B65_L12_N 25

B65_L12_P 25

B65_L13_N 25

B65_L13_P 25

B65_L14_N 25

B65_L14_P 25

B65_L15_N 25

B65_L15_P 25

B65_L16_N 25

B65_L16_P 25

B65_L17_N 25

B65_L17_P 25

B65_L18_N 25

B65_L18_P 25

B65_L19_N 25

B65_L19_P 25

B65_L20_N 25

B65_L20_P 25

B65_L21_N 25

B65_L21_P 25

B65_L22_N 25

B65_L22_P 25

B65_L23_N 25

B65_L23_P 25

B65_L24_N 25

B65_L24_P 25

B66_L1_N 25

B66_L1_P 25

B66_L2_N 25

B66_L2_P 25

B66_L3_N 25

B66_L3_P 25

B66_L4_N 25

B66_L4_P 25

B66_L5_N 25

B66_L5_P 25

B66_L6_N 25

B66_L6_P 25

B66_L7_N 25

B66_L7_P 25

B66_L8_N 25

B66_L8_P 25

B66_L9_N 25

B66_L9_P 25

B66_L10_N 25

B66_L10_P 25

B66_L11_N 25

B66_L11_P 25

B66_L12_N 25

B66_L12_P 25

B66_L13_N 25

B66_L13_P 25

B66_L14_N 25

B66_L14_P 25

B66_L15_N 25

B66_L15_P 25

B66_L16_N 25

B66_L16_P 25

B66_L17_N 25

B66_L17_P 25

B66_L18_N 25

B66_L18_P 25

B66_L19_N 25

B66_L19_P 25

B66_L20_N 25

B66_L20_P 25

B66_L21_N 25

B66_L21_P 25

B66_L22_N 25

B66_L22_P 25

B66_L23_N 25

B66_L23_P 25

B66_L24_N 25

B66_L24_P 25

Title

Size

Document Number Rev

Date: Sheet

of

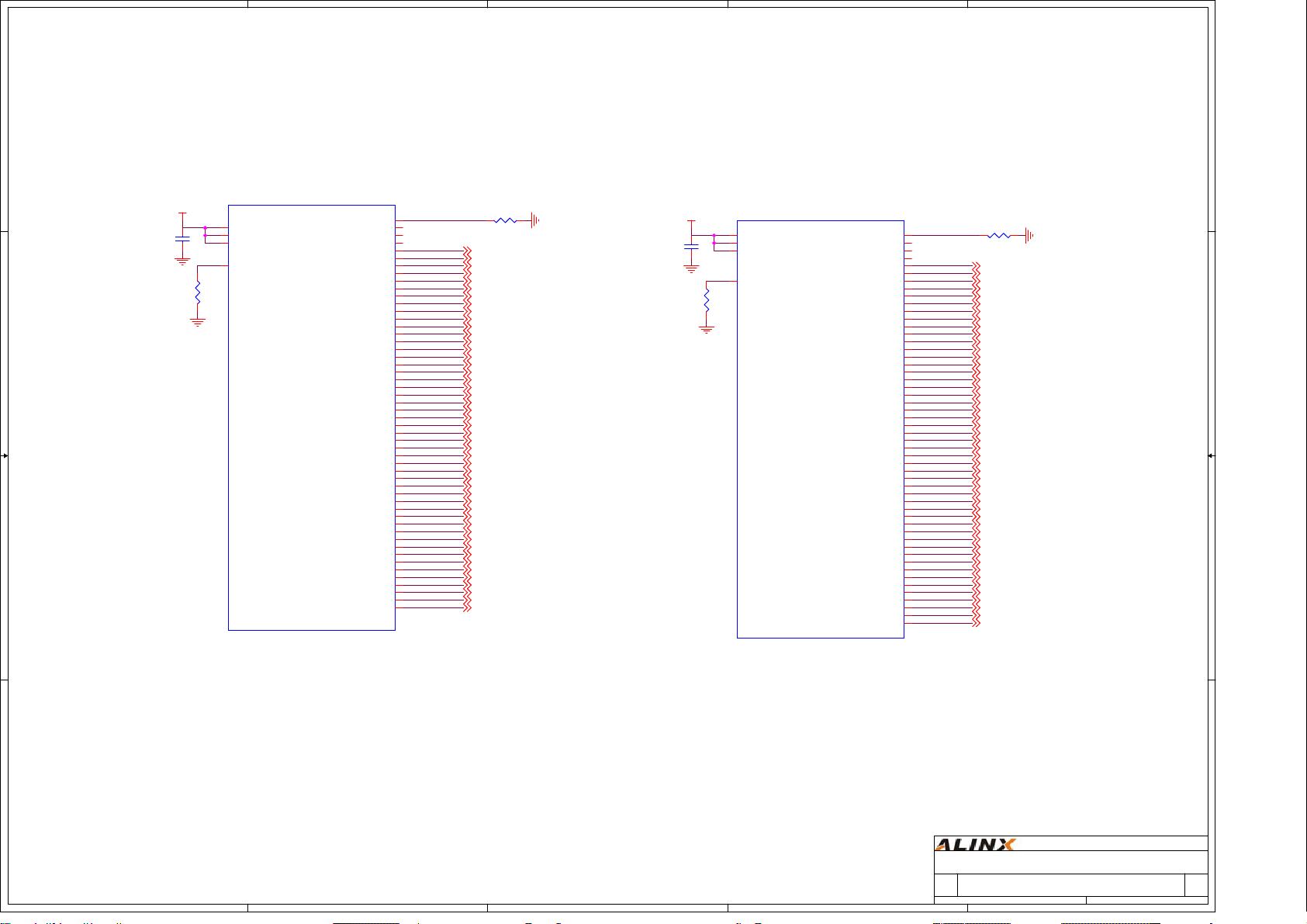

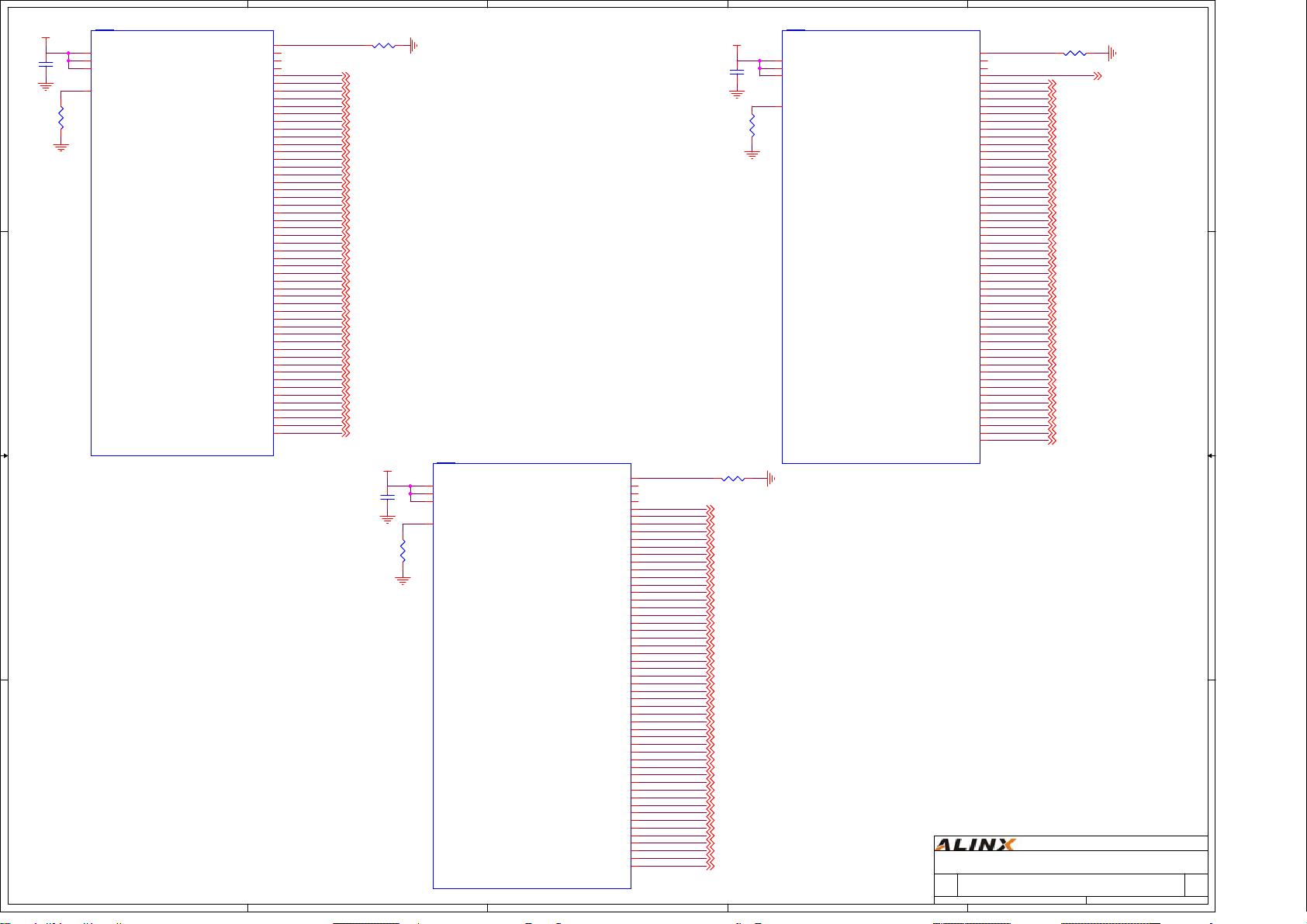

ACU19EG核心板 Schematics

1.0

PAGE06 Z7 Bank64_65_66

631Wednesday, October 26, 2022

Title

Size

Document Number Rev

Date: Sheet

of

ACU19EG核心板 Schematics

1.0

PAGE06 Z7 Bank64_65_66

631Wednesday, October 26, 2022

Title

Size

Document Number Rev

Date: Sheet

of

ACU19EG核心板 Schematics

1.0

PAGE06 Z7 Bank64_65_66

631Wednesday, October 26, 2022

xczu19eg-ffvc1760-2-i

U76-4

VREF_66

AJ16

VCCO_66

AP18

VCCO_66

AV15

VCCO_66

BA14

IO_T0U_N12_VRP_66

AY13

IO_T1U_N12_66

BB14

IO_T2U_N12_66

AP17

IO_T3U_N12_66

AL17

IO_L1N_T0L_N1_DBC_66

BA17

IO_L1P_T0L_N0_DBC_66

AY17

IO_L2N_T0L_N3_66

BB16

IO_L2P_T0L_N2_66

BA16

IO_L3N_T0L_N5_AD15N_66

AW16

IO_L3P_T0L_N4_AD15P_66

AW17

IO_L4N_T0U_N7_DBC_AD7N_66

BB15

IO_L4P_T0U_N6_DBC_AD7P_66

BA15

IO_L5N_T0U_N9_AD14N_66

AY14

IO_L5P_T0U_N8_AD14P_66

AY15

IO_L6N_T0U_N11_AD6N_66

BB13

IO_L6P_T0U_N10_AD6P_66

BA13

IO_L7N_T1L_N1_QBC_AD13N_66

BA12

IO_L7P_T1L_N0_QBC_AD13P_66

AY12

IO_L8N_T1L_N3_AD5N_66

BB11

IO_L8P_T1L_N2_AD5P_66

BA11

IO_L9N_T1L_N5_AD12N_66

BB10

IO_L9P_T1L_N4_AD12P_66

BA10

IO_L10N_T1U_N7_QBC_AD4N_66

AV13

IO_L10P_T1U_N6_QBC_AD4P_66

AU13

IO_L11N_T1U_N9_GC_66

AW14

IO_L11P_T1U_N8_GC_66

AW15

IO_L12N_T1U_N11_GC_66

AV14

IO_L12P_T1U_N10_GC_66

AU14

IO_L13N_T2L_N1_GC_QBC_66

AV16

IO_L13P_T2L_N0_GC_QBC_66

AV17

IO_L14N_T2L_N3_GC_66

AU15

IO_L14P_T2L_N2_GC_66

AT15

IO_L15N_T2L_N5_AD11N_66

AV18

IO_L15P_T2L_N4_AD11P_66

AU18

IO_L16N_T2U_N7_QBC_AD3N_66

AT18

IO_L16P_T2U_N6_QBC_AD3P_66

AR18

IO_L17N_T2U_N9_AD10N_66

AT17

IO_L17P_T2U_N8_AD10P_66

AR17

IO_L18N_T2U_N11_AD2N_66

AU16

IO_L18P_T2U_N10_AD2P_66

AT16

IO_L19N_T3L_N1_DBC_AD9N_66

AK18

IO_L19P_T3L_N0_DBC_AD9P_66

AJ18

IO_L20N_T3L_N3_AD1N_66

AM18

IO_L20P_T3L_N2_AD1P_66

AL18

IO_L21N_T3L_N5_AD8N_66

AN17

IO_L21P_T3L_N4_AD8P_66

AN18

IO_L22N_T3U_N7_DBC_AD0N_66

AK17

IO_L22P_T3U_N6_DBC_AD0P_66

AJ17

IO_L23N_T3U_N9_66

AM16

IO_L23P_T3U_N8_66

AL16

IO_L24N_T3U_N11_66

AP16

IO_L24P_T3U_N10_66

AN16

R233

1K/1%

R722240R/1%

xczu19eg-ffvc1760-2-i

U76-3

VREF_65

AJ23

VCCO_65

AR26

VCCO_65

AV25

VCCO_65

BA24

IO_T0U_N12_VRP_65

BA27

IO_T1U_N12_SMBALERT_65

AW25

IO_T2U_N12_65

AP26

IO_T3U_N12_PERSTN0_65

AM25

IO_L1N_T0L_N1_DBC_65

AY24

IO_L1P_T0L_N0_DBC_65

AW24

IO_L2N_T0L_N3_65

BB25

IO_L2P_T0L_N2_65

BB24

IO_L3N_T0L_N5_AD15N_65

BA25

IO_L3P_T0L_N4_AD15P_65

AY25

IO_L4N_T0U_N7_DBC_AD7N_65

BB26

IO_L4P_T0U_N6_DBC_AD7P_65

BA26

IO_L5N_T0U_N9_AD14N_65

AY28

IO_L5P_T0U_N8_AD14P_65

AY27

IO_L6N_T0U_N11_AD6N_65

BB28

IO_L6P_T0U_N10_AD6P_65

BA28

IO_L7N_T1L_N1_QBC_AD13N_65

AV24

IO_L7P_T1L_N0_QBC_AD13P_65

AU24

IO_L8N_T1L_N3_AD5N_65

AW26

IO_L8P_T1L_N2_AD5P_65

AV26

IO_L9N_T1L_N5_AD12N_65

AW27

IO_L9P_T1L_N4_AD12P_65

AV27

IO_L10N_T1U_N7_QBC_AD4N_65

AV28

IO_L10P_T1U_N6_QBC_AD4P_65

AU28

IO_L11N_T1U_N9_GC_65

AU26

IO_L11P_T1U_N8_GC_65

AU25

IO_L12N_T1U_N11_GC_65

AT26

IO_L12P_T1U_N10_GC_65

AT25

IO_L13N_T2L_N1_GC_QBC_65

AT27

IO_L13P_T2L_N0_GC_QBC_65

AR27

IO_L14N_T2L_N3_GC_65

AR25

IO_L14P_T2L_N2_GC_65

AR24

IO_L15N_T2L_N5_AD11N_65

AN26

IO_L15P_T2L_N4_AD11P_65

AM26

IO_L16N_T2U_N7_QBC_AD3N_65

AP27

IO_L16P_T2U_N6_QBC_AD3P_65

AN27

IO_L17N_T2U_N9_AD10N_65

AN28

IO_L17P_T2U_N8_AD10P_65

AM28

IO_L18N_T2U_N11_AD2N_65

AT28

IO_L18P_T2U_N10_AD2P_65

AR28

IO_L19N_T3L_N1_DBC_AD9N_65

AT23

IO_L19P_T3L_N0_DBC_AD9P_65

AR23

IO_L20N_T3L_N3_AD1N_65

AP25

IO_L20P_T3L_N2_AD1P_65

AP24

IO_L21N_T3L_N5_AD8N_65

AN24

IO_L21P_T3L_N4_AD8P_65

AM24

IO_L22N_T3U_N7_DBC_AD0N_65

AN23

IO_L22P_T3U_N6_DBC_AD0P_65

AM23

IO_L23N_T3U_N9_PERSTN1_I2C_SDA_65

AL23

IO_L23P_T3U_N8_I2C_SCLK_65

AK23

IO_L24N_T3U_N11_65

AK24

IO_L24P_T3U_N10_65

AJ24

R170

1K/1%

C884

47uF/6.3V

C1653

47uF/6.3V

R234240R/1%

R721240R/1%

xczu19eg-ffvc1760-2-i

U76-2

VREF_64

AJ19

VCCO_64

AR21

VCCO_64

AV20

VCCO_64

BA19

IO_T0U_N12_VRP_64

BB21

IO_T1U_N12_64

AW21

IO_T2U_N12_64

AR22

IO_T3U_N12_64

AL20

IO_L1N_T0L_N1_DBC_64

BB23

IO_L1P_T0L_N0_DBC_64

BA23

IO_L2N_T0L_N3_64

AY22

IO_L2P_T0L_N2_64

AY23

IO_L3N_T0L_N5_AD15N_64

BA21

IO_L3P_T0L_N4_AD15P_64

BA22

IO_L4N_T0U_N7_DBC_AD7N_64

BA20

IO_L4P_T0U_N6_DBC_AD7P_64

AY20

IO_L5N_T0U_N9_AD14N_64

BB19

IO_L5P_T0U_N8_AD14P_64

BB20

IO_L6N_T0U_N11_AD6N_64

BB18

IO_L6P_T0U_N10_AD6P_64

BA18

IO_L7N_T1L_N1_QBC_AD13N_64

AV23

IO_L7P_T1L_N0_QBC_AD13P_64

AU23

IO_L8N_T1L_N3_AD5N_64

AW22

IO_L8P_T1L_N2_AD5P_64

AV22

IO_L9N_T1L_N5_AD12N_64

AW19

IO_L9P_T1L_N4_AD12P_64

AW20

IO_L10N_T1U_N7_QBC_AD4N_64

AY18

IO_L10P_T1U_N6_QBC_AD4P_64

AY19

IO_L11N_T1U_N9_GC_64

AV21

IO_L11P_T1U_N8_GC_64

AU21

IO_L12N_T1U_N11_GC_64

AV19

IO_L12P_T1U_N10_GC_64

AU20

IO_L13N_T2L_N1_GC_QBC_64

AT21

IO_L13P_T2L_N0_GC_QBC_64

AT22

IO_L14N_T2L_N3_GC_64

AU19

IO_L14P_T2L_N2_GC_64

AT20

IO_L15N_T2L_N5_AD11N_64

AP22

IO_L15P_T2L_N4_AD11P_64

AN22

IO_L16N_T2U_N7_QBC_AD3N_64

AP21

IO_L16P_T2U_N6_QBC_AD3P_64

AN21

IO_L17N_T2U_N9_AD10N_64

AR20

IO_L17P_T2U_N8_AD10P_64

AP20

IO_L18N_T2U_N11_AD2N_64

AR19

IO_L18P_T2U_N10_AD2P_64

AP19

IO_L19N_T3L_N1_DBC_AD9N_64

AN19

IO_L19P_T3L_N0_DBC_AD9P_64

AM19

IO_L20N_T3L_N3_AD1N_64

AM20

IO_L20P_T3L_N2_AD1P_64

AM21

IO_L21N_T3L_N5_AD8N_64

AL21

IO_L21P_T3L_N4_AD8P_64

AL22

IO_L22N_T3U_N7_DBC_AD0N_64

AK19

IO_L22P_T3U_N6_DBC_AD0P_64

AK20

IO_L23N_T3U_N9_64

AJ20

IO_L23P_T3U_N8_64

AJ21

IO_L24N_T3U_N11_64

AK22

IO_L24P_T3U_N10_64

AJ22

C1654

47uF/6.3V

R723

1K/1%