Nelson et al. VOL. 4, NO. 11/NOVEMBER 2012/J. OPT. COMMUN. NETW. B133

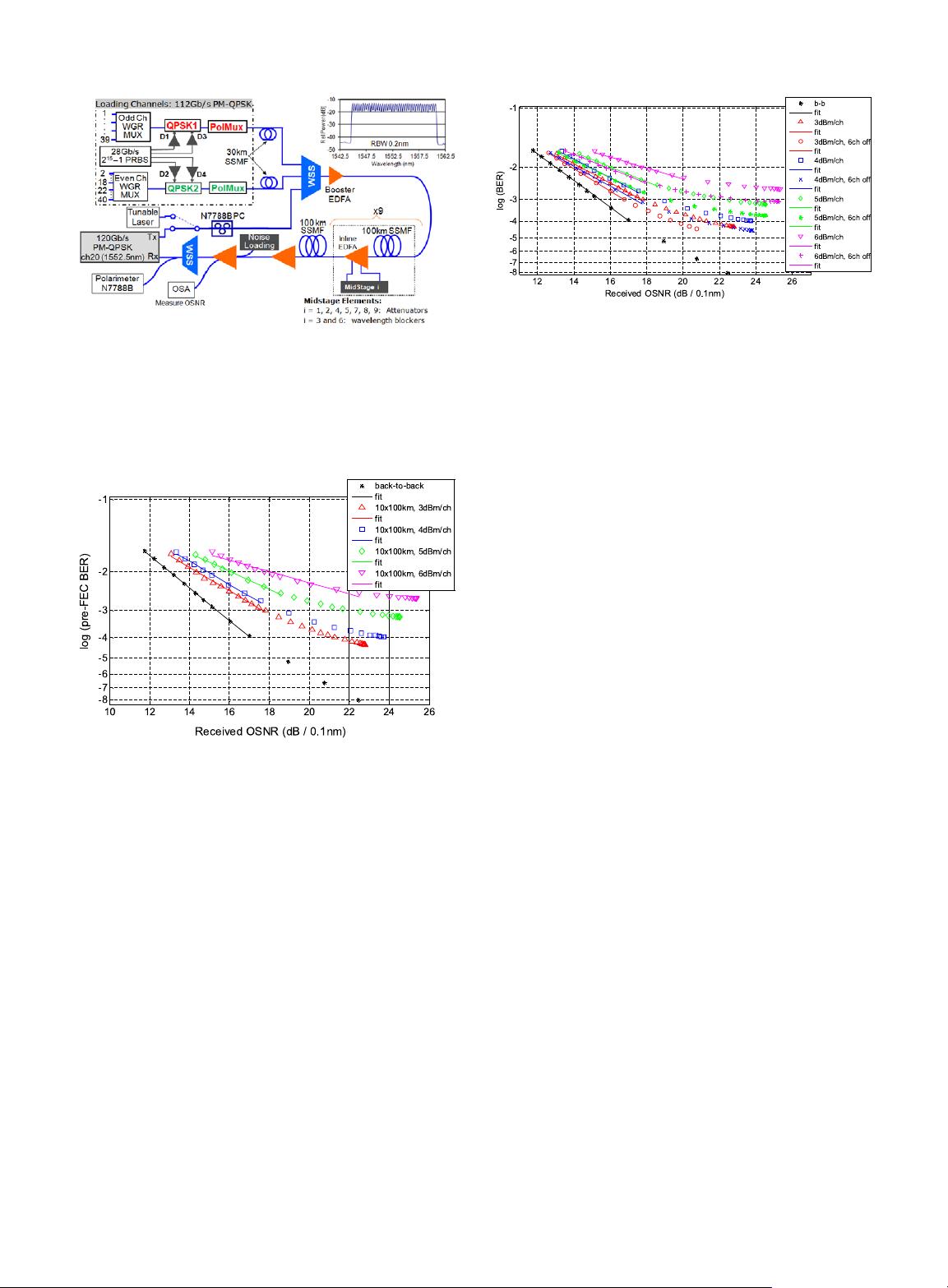

Fig. 2. (Color online) Block diagram of the 100 Gb/s WDM test

setup over the uncompensated 1000 km link. The tunable laser,

N7788B polarization controller (PC) and polarimeter were added for

the experiments of Section V. Inset: the 40-channel spectrum at the

booster output.

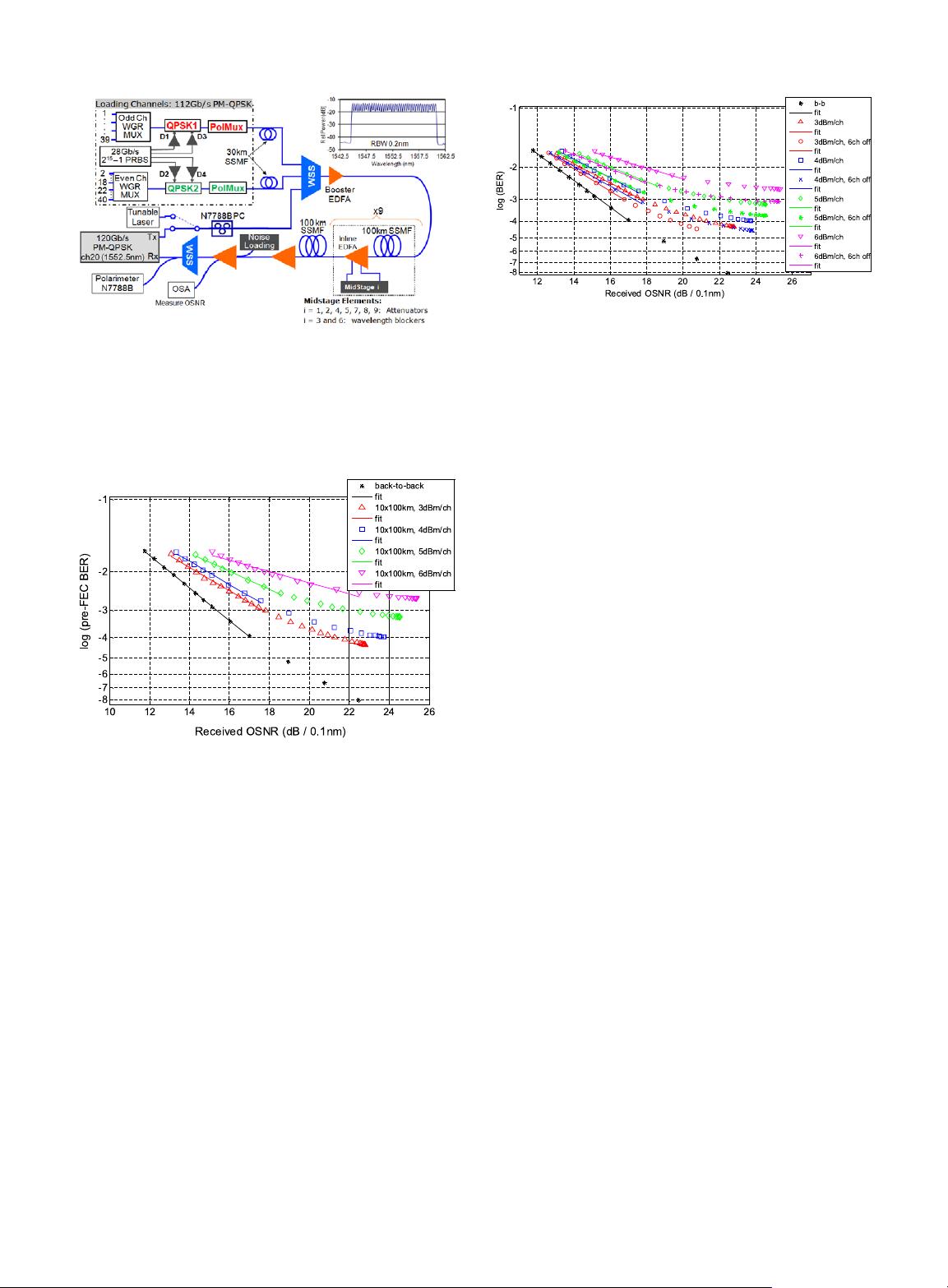

Fig. 3. (Color online) Measurements of pre-FEC BER versus OSNR

for the 100 Gb/s MSA transceiver as channel 20 of the 40 × 100 Gb/s

1000 km system, with +3 to +6 dBm/ch launch powers into the spans.

used in the link; hence, the MSA transceiver compensated

for approximately 17,000 ps/nm of chromatic dispersion. After

each span, a two-stage erbium-doped fiber amplifier (EDFA)

was used to amplify the optical signal power. To optimize the

gain tilt, variable optical attenuators were introduced at the

mid-stages of EDFAs 1, 2, 4, 5, 7, 8, and 9, while 50 GHz

grid wavelength blockers at the mid-stages of EDFAs 3 and 6

allowed per-channel equalization. The total launch power into

each span could be varied from +19 to +21 dBm, while still

maintaining a flat channel spectrum to within ±1.5 dB at the

input to each span. Following the tenth fiber span, the test

channel was noise loaded, and its OSNR was measured with an

optical spectrum analyzer (OSA). Finally, a second commercial

50 GHz WSS was used to de-multiplex the test channel before

it was sent to the receiver input of the 100G transceiver.

Figure 3 presents BER curves after 1000 km WDM trans-

mission for launch powers of +3, +4, +5 and +6 dBm/channel

into the fiber spans. (To reach +6 dBm/ch, 20 channels in the

center of the band were transmitted.) At +3 dBm/ch, the OSNR

Fig. 4. (Color online) Comparison of the measured pre-FEC BER

versus OSNR curves from Fig. 3 with the curves measured when the

three channels on both sides of channel 20 were turned off.

penalty relative to back-to-back is 1.0 dB for a BER of 1.9×10

−2

(the SD-FEC threshold). Moreover, the received OSNR after

1000 km is 22.8 dB, indicating that sufficient margin remains

for transmission distances of 2000 km. As shown in Fig. 3, the

OSNR penalty increases to 3 dB for +6 dBm/ch; however, at

that launch power, the BER floor is still well below the FEC

threshold. To test the impact of the neighboring 100G channels,

BER curves were also measured at the different launch powers

when the six nearest neighbors (i.e., ch 17–19 and 21–23)

were turned off. To maintain the same per-channel power and

EDFA loading, three additional channels were turned on at

the short and long wavelength ends of the spectrum. Figure 4

shows a comparison of the BER curves for the channel under

test with neighboring 50-GHz-spaced, 100G channels and with

nearest neighbors spaced 200 GHz from the channel under test

(i.e., with ch 17–19 and 21–23 turned off). At +3 dBm/ch, the

required OSNR difference is only 0.3 dB, while the difference

is 1.5 dB for +6 dBm/ch. Note that, given the SSMF dispersion

and the uncompensated link, we believe the 2 Gbaud lower

symbol rate of the loading channels compared with that of

the channel under test will have only a minor impact on

the measured WDM penalties. In fact, the 28 Gbaud loading

channels walk through the channel under test at a slightly

slower rate than 30 Gbaud loading channels would, and thus

the measured WDM penalties may be slightly higher than the

actual WDM penalties would be with loading channels at the

same 30 Gbaud symbol rate as the channel under test.

As mentioned previously, the SD-FEC has been designed to

convert a pre-FEC BER of 1.9 × 10

−2

to less than 1 × 10

−15

after SD-FEC decoding, corresponding to more than 11 dB net

coding gain. In the experiments, the measured FEC threshold

is in good agreement with prediction. Figure 5 presents the

recorded post-FEC errors after SD-FEC decoding as a function

of measured pre-FEC BER for the different launch powers,

including the points from the curves of Fig. 3. Comparing the

curve for back-to-back with those after transmission verifies

that the FEC threshold—and thereby the coding gain—is

essentially maintained in the presence of fiber nonlinearities.

The FEC threshold was measured to change by <0.15 dBQ

at power levels up to +6 dBm per channel, the maximum

launch power attainable in this setup. To test repeatability,

BER curves for 3 dBm/ch and 5 dBm/ch were measured twice,

with slightly different received OSNRs.