并行处理机原理与阵列结构详解

需积分: 0 95 浏览量

更新于2024-06-30

收藏 3.72MB DOCX 举报

第六章内容深入探讨了并行处理机及其在计算机体系结构中的核心地位。并行处理机,又称阵列处理机,是一种设计用于实现操作级并行的计算机架构,通过重复设置多个相同的处理单元(PE),每个PE独立处理分配的数据,同时在统一控制器(CU)的调度下协同工作。这种架构的特点包括:

1. **并行处理原理**:并行处理机通过资源重复实现并行执行,从CU角度看,指令按串行顺序执行,但每个PE能并行处理数据。其速度极快且有较大提升空间,具有模块化优势,易于生产和维护,具有高可靠性,能实现容错和重构。

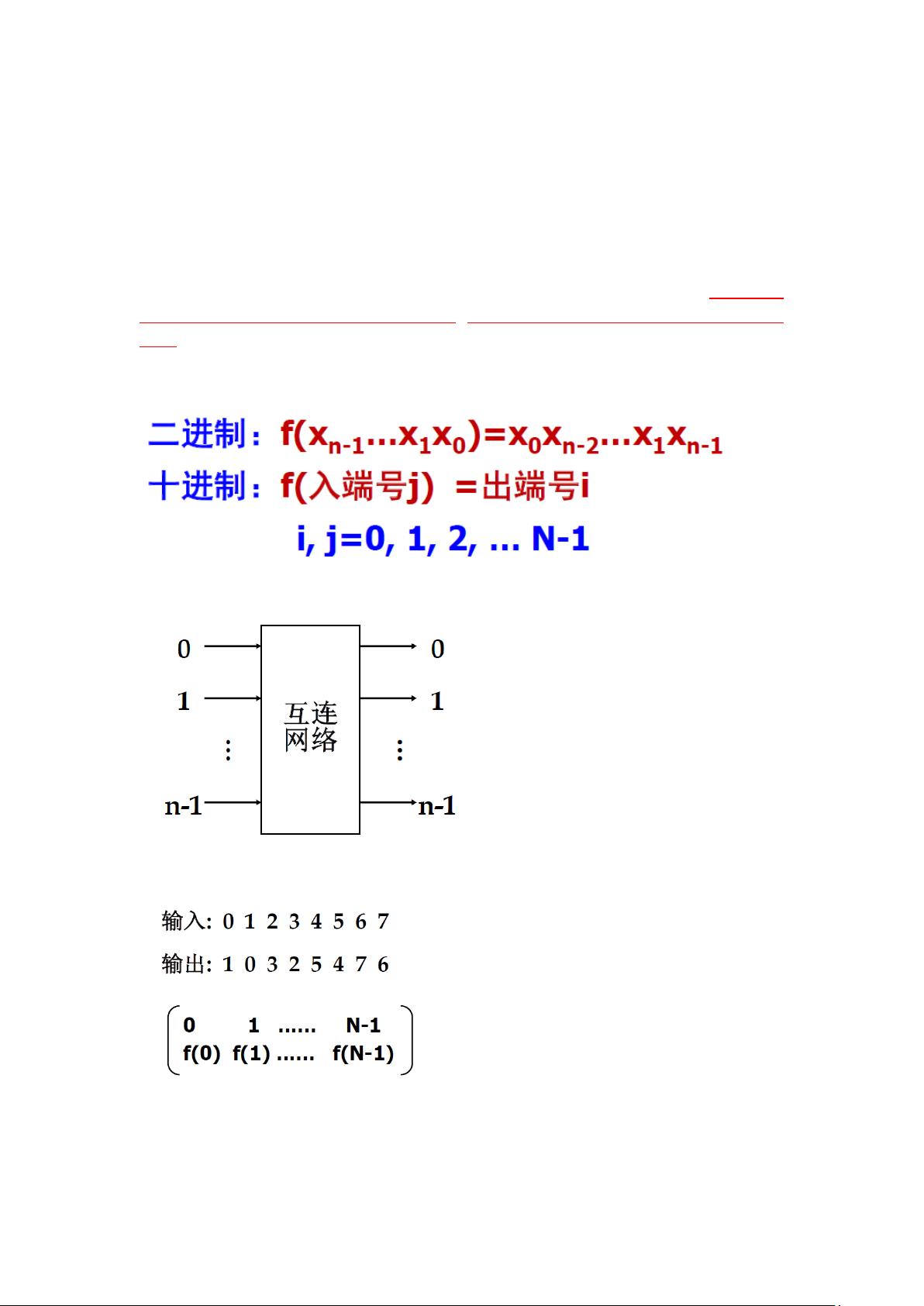

2. **组件构成**:并行处理机由CU(控制器)、多个PE(处理单元)、存储器模块(M)、互连网络(ICN)和输入输出处理机(IOP)组成。CU负责指令的编码和分发,而PE们执行实际的计算任务。

3. **存储器类型**:有两种基本构形:分布式存储器的阵列处理机,每个PE有独立的局部存储器(PEM),数据预分配至PEM以优化处理;集中式共享存储器的阵列处理机,所有PE共享存储资源,数据交换依赖于互连网络。

4. **性能与局限**:并行处理机虽然速度较快,但效率相对较低,特别是在与流水线或向量处理机等传统架构比较时。它往往作为专用计算机,高度依赖于并行算法,因为没有通用性和灵活性。同时,阵列处理机特别是大规模并行处理器(MPP)如需高效运作,必须依赖有效的并行算法,限制了其应用范围。

5. **阵列处理机的未来**:分布式存储器的阵列处理机在SIMD(Single Instruction Multiple Data,单指令流多数据流)领域占据主导,可以支持大量PE的并行处理,但需要高效的并行算法支持。相比之下,集中式共享存储器的阵列处理机虽然共享资源,但复杂性增加,适用于对数据访问一致性要求较高的应用场景。

总结来说,第六章重点讲解了并行处理机的结构、工作原理,以及它如何通过不同的存储器配置实现高效并行计算,同时也揭示了其在特定场景下的优势和局限性。对于理解现代计算机体系结构中并行计算的关键元素,这一章提供了深入的洞察。

2010-04-06 上传

2022-11-21 上传

142 浏览量

2172 浏览量

2021-12-07 上传

456 浏览量

114 浏览量

2021-09-28 上传

无声远望

- 粉丝: 1127

- 资源: 298

最新资源

- Star UML指导手册

- FAT32文件系统白皮书(中文)

- 领域驱动模型详细介绍

- Asp.net开发必备51种代码(非常实用)

- 智能手机操作系统简介

- 当前,CORBA、DCOM、RMI等RPC中间件技术已广泛应用于各个领域。但是面对规模和复杂度都越来越高的分布式系统,这些技术也显示出其局限性:(1)同步通信:客户发出调用后,必须等待服务对象完成处理并返回结果后才能继续执行;(2)客户和服务对象的生命周期紧密耦合:客户进程和服务对象进程都必须正常运行;如果由于服务对象崩溃或者网络故障导致客户的请求不可达,客户会接收到异常;(3)点对点通信:客户的一次调用只发送给某个单独的目标对象。

- JSP 《标签啊,标签!》

- UDDI 注册中心介绍

- Thinking in C++, Volume 2, 2nd Edition 英文版 (pdf)

- 完全精通局域网.rar

- mtk的make命令分析

- Essential-MATLAB-for-Engineers-and-Scientists-Third-Edition

- Maven 权威指南 简体中文版

- 深入理解计算体系结构英文版

- AT&T汇编学习资料

- 计算机故障查询手册(非高手用)