使用VHDL设计与实现8位加法器

需积分: 50 117 浏览量

更新于2024-09-11

收藏 447KB DOC 举报

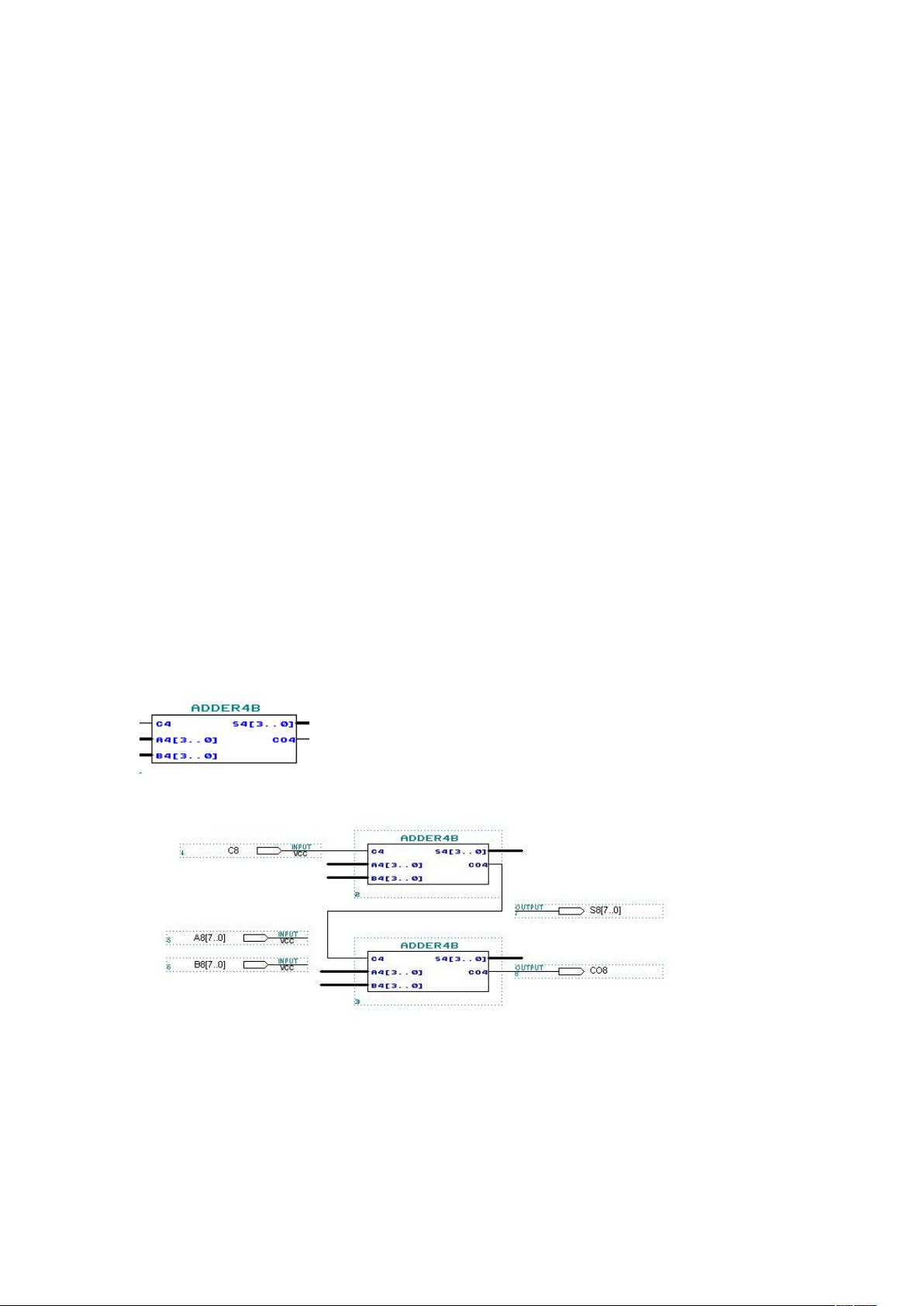

"8位加法器的设计文档包含了加法器设计的理论与实践,通过VHDL编程实现,包括4位加法器的级联来构成8位加法器,并在GW48-CKEDA实验开发系统上进行硬件验证。"

在数字逻辑设计中,加法器是基本的计算单元,用于执行二进制数的加法操作。本实验的目标是设计和实现一个8位加法器,它由两个4位并行加法器级联组成,整个过程涉及VHDL语言编程以及硬件验证。以下是详细的步骤和知识点:

1. **实验目的**:

- 学习使用isEXPERT/MAX+plusⅡ/FoudationSeries等软件,这些都是常见的EDA工具,用于编写、仿真和综合数字逻辑电路。

- 掌握GW48-CKEDA实验开发系统,这是一个硬件平台,用于验证设计的电路功能。

- 了解VHDL语言的基本结构,VHDL是一种硬件描述语言,用于描述数字系统的结构和行为。

2. **实验内容**:

- 设计8位并行加法器,其中每个4位加法器负责处理二进制数的一部分。

- 编写VHDL源程序,包括4位和8位加法器的实体和结构体,以实现逻辑功能。

- 创建仿真测试文件,用于在软件环境中验证设计的正确性。

- 准备硬件验证所需的管脚锁定文件,确保设计能正确映射到实际的FPGA芯片isPLSI1032E。

3. **实验设计**:

- **系统原理图框架**:一个8位加法器由两个4位加法器连接,每个4位加法器的进位输出连接到下一个4位加法器的进位输入,最终形成完整的8位加法。

- **VHDL源程序**:

- `adder4b.vhd`:定义了4位二进制并行加法器,输入包括4位的a4和b4,进位输入c4,输出是4位的结果s4和进位输出co4。在代码中,首先将输入扩展为5位,然后进行加法运算,最后截取低4位作为输出s4,最高位作为进位co4。

- `adder8b.vhd`:8位加法器的源代码会基于两个4位加法器实例化,并正确连接它们的输入和输出。

4. **VHDL程序详解**:

- `entity`声明了加法器的接口,包括输入和输出信号。

- `architecture`定义了加法器的内部结构,使用信号(signal)存储中间计算结果。

- `process`语句通常用于描述时序逻辑,这里没有使用,因为加法器是组合逻辑。

- 使用`std_logic_vector`类型表示二进制数,`std_logic`表示单个比特。

5. **实验流程**:

- 首先绘制原理图,理解每个部分的功能。

- 编写VHDL代码,实现加法逻辑。

- 在软件中进行仿真,观察逻辑是否正确。

- 生成硬件描述文件,配置FPGA。

- 在GW48-CKEDA平台上进行硬件验证,确保设计能在实际硬件上正常工作。

- 记录实验过程中的问题及解决方案,以便于后续的学习和改进。

通过这个实验,学习者不仅能够掌握加法器的设计,还能熟悉VHDL编程和硬件验证流程,这是数字系统设计的基础。同时,此实验也强调了问题解决能力和实践经验的重要性。

615 浏览量

1337 浏览量

2526 浏览量

304 浏览量

1003 浏览量

435 浏览量

247 浏览量

166 浏览量

2024-12-05 上传

qq_25751453

- 粉丝: 0

最新资源

- Vmware Mac OS完美补丁:解锁器203

- MySQL 5.6.4-m7版本压缩包下载与使用指南

- 易语言实现文字上下滚动效果示例

- Java网上书店系统设计与实现

- 赛普拉斯快照测试:新增DOM元素值对象支持

- 春节拜年专用PPT模板设计

- CGAL-4.6.3软件包发布:代码与文档完整安装指南

- Eurostyle Plugin-CRX 插件简介与应用

- Android Studio中实现百度地图应用开发教程

- Visual C++图像处理系统开发案例源代码

- SIMOTION DCC编程英文版详细说明书

- CoffeeScript开发的2D游戏引擎:coffee-game-engine介绍

- Labview自动化测试:CSV数据读取与上位机控制

- KubeSanity:实现Kubernetes集群的健康检查与管理

- 探索Maxima Products-crx插件:快速导航折扣商品

- 响应式Banner幻灯片特效源码下载 - HTML5自适应切换