基于FPGA的三相PWM发生器设计与VHDL实现

需积分: 12 123 浏览量

更新于2024-08-08

收藏 745KB PDF 举报

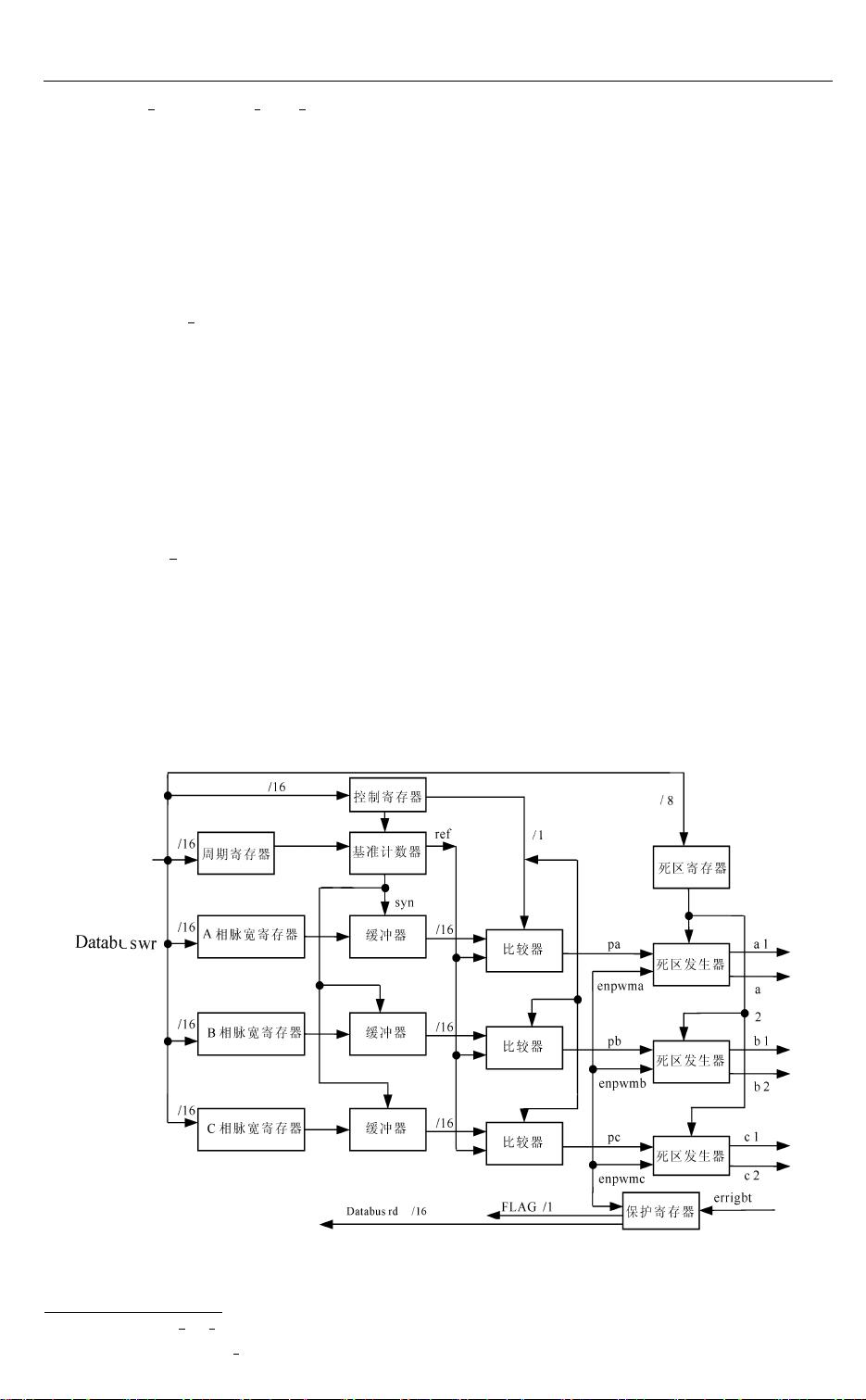

本文主要探讨了基于FPGA的三相PWM发生器的实现方法,发表于2006年的论文中。作者邓清秀和文小玲在武汉化工学院电气信息学院,利用VHDL语言在FPGA中设计了一种高效的三相PWM发生器。该发生器主要包括PWM信号产生和IGBT IPM模块故障保护两个核心部分,其设计特点是灵活性高、易于扩展和通用性,适合多种逆变器应用场景。

PWM信号的生成是逆变器的重要组成部分,它决定了输出电压的质量。设计者利用高速微处理器(如TMS320VC33)提供的信息,并结合IGBT IPM模块的故障检测信号,生成满足三相两电平逆变器需求的PWM波形。通过增加特定的脉宽寄存器和缓冲寄存器,此设计可以适应三相三电平逆变器甚至更多电平的系统。

文章提到市场上的主流FPGA/CPLD芯片如LATTICE、XILINX和ALTERA提供了丰富的选择,作者选择了ALTERA公司的产品和MAX+PLUS II软件进行开发。在VHDL编程中,设计者精细地控制了FPGA内部的各个模块,通过一个16位的控制寄存器来管理,其中低6位具有明确的功能,如计数使能、比较使能和PWM输出控制等。

图1展示了FPGA内部的详细设计结构,清晰地展示了各部分的连接和工作流程。该设计的成功通过MAX+PLUS II软件的仿真得到了验证,证明了其在实际应用中的可行性和有效性。这篇论文提供了一种实用且可扩展的三相PWM发生器设计,对于从事电力电子领域的工程师具有重要的参考价值。

2020-12-09 上传

2021-07-13 上传

2021-05-17 上传

2021-07-13 上传

2020-08-07 上传

2020-10-22 上传

2021-07-13 上传

2021-07-13 上传

2020-08-07 上传

weixin_38715048

- 粉丝: 7

- 资源: 960

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践