优化DDR2-800/DDR3内存的信号完整性和PCB布局策略

需积分: 9 37 浏览量

更新于2024-07-15

收藏 555KB PDF 举报

本文将深入探讨信号完整性(SI)和电源完整性(PI)在DDR2-800兆比特/秒(Mbps)和DDR3内存模块的PCB设计中的关键考虑因素。随着DDR2技术的普及,尤其是在800Mbps和更高速度的应用中,如1066Mbps,以及DDR3内存目标达到1600Mbps,对PCB的设计挑战日益突出。在低层数PCB设计中,如4-6层的传统工艺,信号延迟匹配是主要的关注点,因为这受到电路定时要求的严格控制。

首先,信号完整性涉及多个相互关联的因素。PCB的层堆栈设计是至关重要的,因为它影响了信号的传输速度和完整性。通过优化层数和材料选择,可以确保信号在不同层之间的传播延迟保持一致,从而避免信号畸变。此外,阻抗管理是另一个核心部分,包括信号线的宽度、间距和阻抗控制,以维持正确的信号幅值和相位一致性。

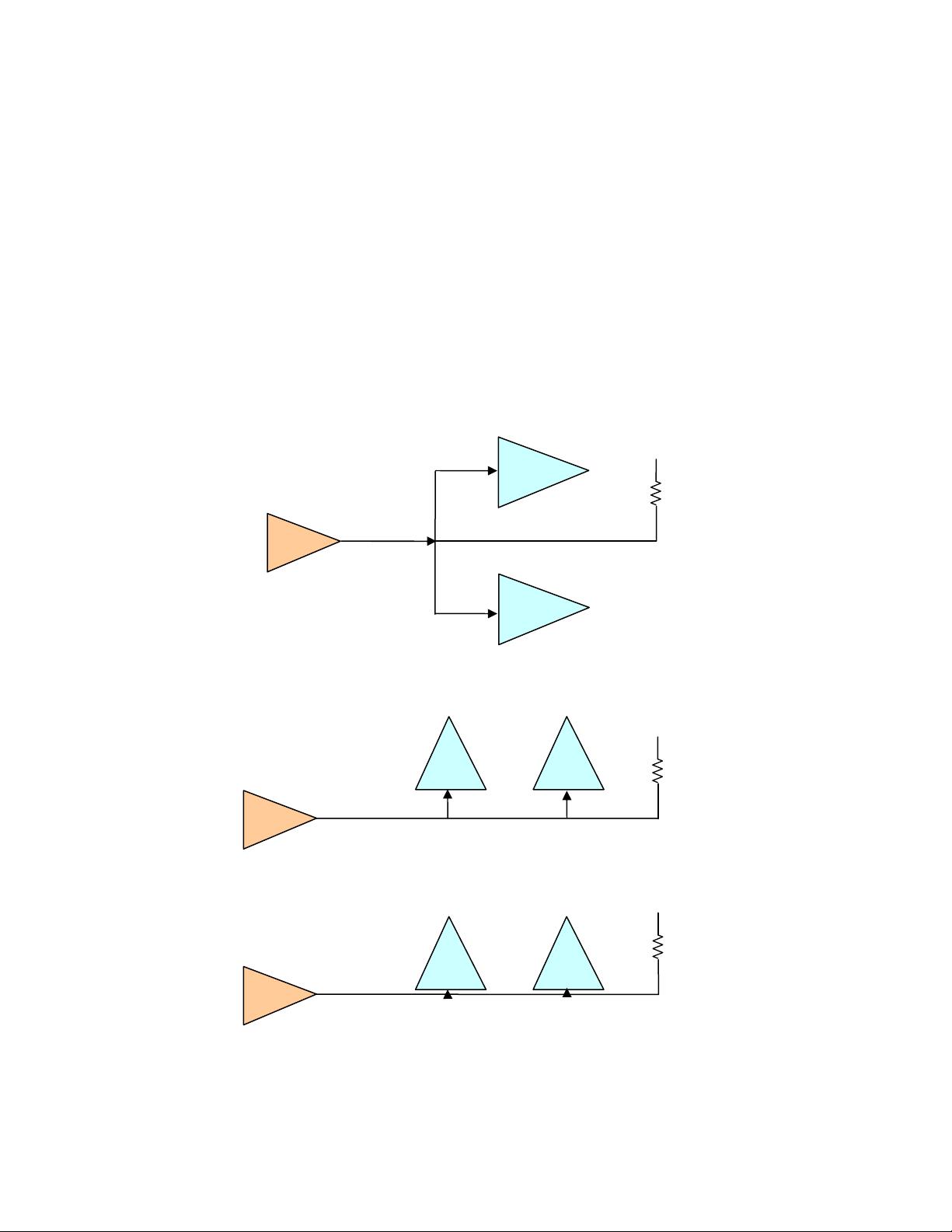

其次,不同类型的互连拓扑,如星形、总线或网格结构,对信号完整性有显著影响。设计师需要选择适合高速数据传输的布局策略,同时减少信号回路耦合和串扰(cross-talk),这可能涉及到信号线的布线策略和隔离技术。

电源完整性也是一大挑战,特别是在高数据速率下。电源噪声可能会对信号质量造成负面影响。因此,电源平面的布局、滤波和去耦网络的设计必不可少,以减小电压波动并保持稳定的电源供应。

延迟匹配是一个关键技术,它要求信号在不同阶段之间保持精确的时间差,这对于满足时序要求至关重要。为了实现这一点,可能需要利用特殊的阻抗控制和走线技术,以及考虑信号路径上的各个阶段的延迟补偿。

最后,CAD工具,如Cadence ALLEGRO等,对于进行完整的SI和PI分析是不可或缺的。这些工具可以帮助设计师模拟信号行为,识别潜在问题,并提供改进建议,以确保最终设计满足严格的规范和标准。

设计DDR2-800 Mbps和DDR3内存的PCB需要综合考虑信号完整性、电源完整性、延迟匹配、互连设计和使用先进的设计工具。每个环节的优化都是为了在高速数据传输中提供稳定、无干扰的信号性能,这是保证系统性能和可靠性的基础。

2013-04-07 上传

2021-11-04 上传

139 浏览量

165 浏览量

A dynamic and adaptive load balancing strategy for parallel file system with large-scale I/O servers

2021-02-21 上传

117 浏览量

178 浏览量

不折腾会死

- 粉丝: 0

- 资源: 6

最新资源

- Alaamimi

- StoryScrip-crx插件

- btw_deploy_test:btw的playtest存储库

- 29500-g30.zip

- Single Click for for Google:trade_mark: Apps-crx插件

- getallpropertynames:获取原型链中的所有属性名称

- github-bot:GitHub自动处理问题,PR,发布机器人

- JavaScript和DOM操作

- VB隐藏或显示“开始”菜单中的各种选项

- mriscv:带有C&Rust应用程序的Mini RISC-V 32位计算机

- SQLserver2008.rar

- Geekmarks client-crx插件

- ExeBinder.7z

- competencies

- 建筑电气自动化控制技术的相关分析 (1).rar

- MyFoody:第2周作业-食品应用