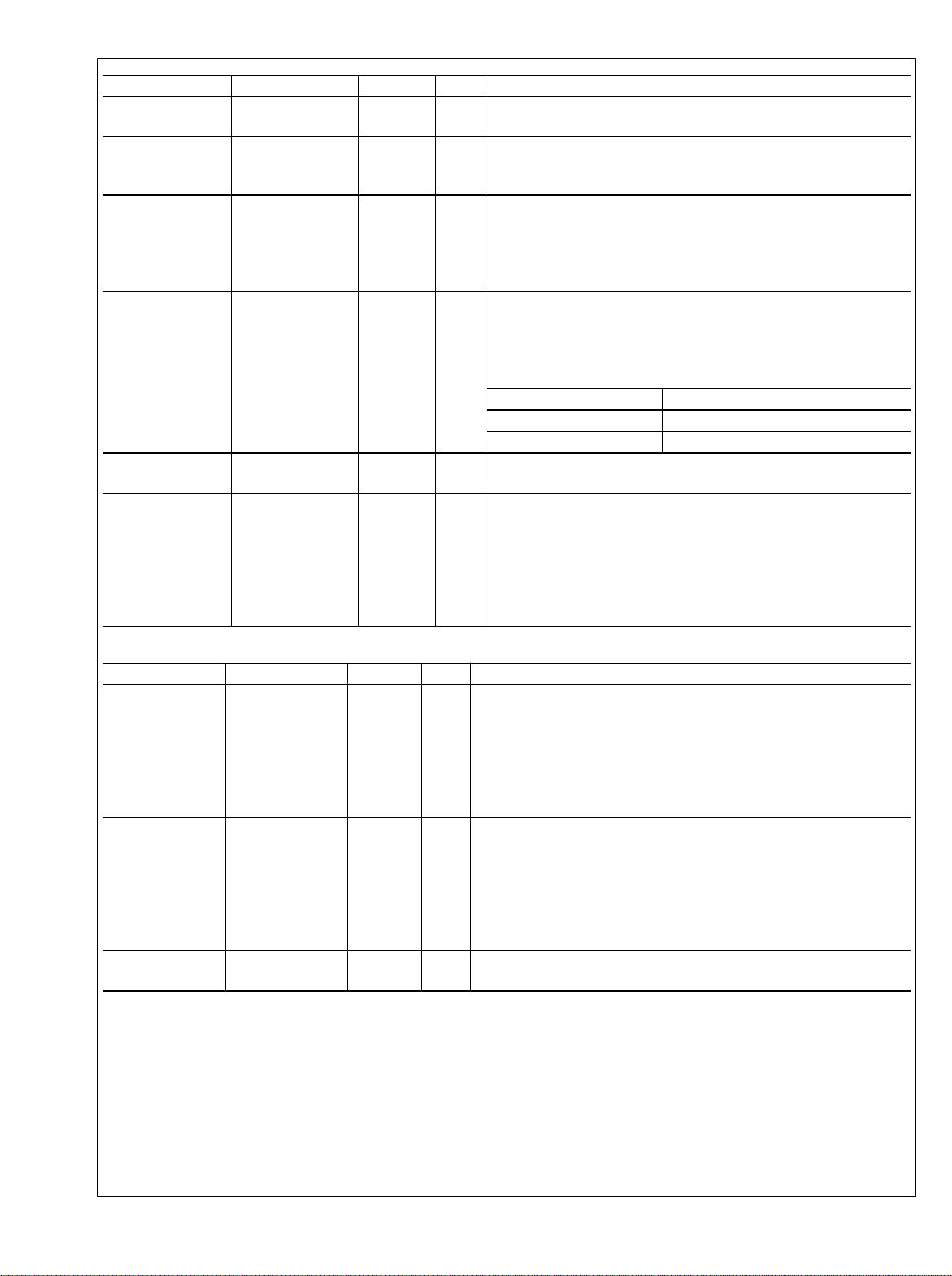

The Auto-Negotiation Expansion Register (ANER) indicates

additional Auto-Negotiation status. The ANER provides sta-

tus on:

•

Whether or not a Parallel Detect Fault has occurred

•

Whether or not the Link Partner supports the Next Page

function

•

Whether or not the DP83640 supports the Next Page

function

•

Whether or not the current page being exchanged by Auto-

Negotiation has been received

•

Whether or not the Link Partner supports Auto-Negotiation

9.2.3 Auto-Negotiation Parallel Detection

The DP83640 supports the Parallel Detection function as de-

fined in the IEEE 802.3u specification. Parallel Detection

requires both the 10 Mb/s and 100 Mb/s receivers to monitor

the receive signal and report link status to the Auto-Negotia-

tion function. Auto-Negotiation uses this information to con-

figure the correct technology in the event that the Link Partner

does not support Auto-Negotiation but is transmitting link sig-

nals that the 100BASE-TX or 10BASE-T PMAs recognize as

valid link signals.

If the DP83640 completes Auto-Negotiation as a result of

Parallel Detection, bits 5 and 7 within the ANLPAR register

will be set to reflect the mode of operation present in the Link

Partner. Note that bits 4:0 of the ANLPAR will also be set to

00001 based on a successful parallel detection to indicate a

valid 802.3 selector field. Software may determine that nego-

tiation completed via Parallel Detection by reading a zero in

the Link Partner Auto-Negotiation Able bit once the Auto-Ne-

gotiation Complete bit is set. If configured for parallel detect

mode and any condition other than a single good link occurs

then the parallel detect fault bit will be set.

9.2.4 Auto-Negotiation Restart

Once Auto-Negotiation has completed, it may be restarted at

any time by setting bit 9 (Restart Auto-Negotiation) of the BM-

CR to one. If the mode configured by a successful Auto-

Negotiation loses a valid link, then the Auto-Negotiation

process will resume and attempt to determine the configura-

tion for the link. This function ensures that a valid configura-

tion is maintained if the cable becomes disconnected.

A renegotiation request from any entity, such as a manage-

ment agent, will cause the DP83640 to halt any transmit data

and link pulse activity until the break_link_timer expires

(~1500 ms). Consequently, the Link Partner will go into link

fail and normal Auto-Negotiation resumes. The DP83640 will

resume Auto-Negotiation after the break_link_timer has ex-

pired by issuing FLP (Fast Link Pulse) bursts.

9.2.5 Enabling Auto-Negotiation via Software

It is important to note that if the DP83640 has been initialized

upon power-up as a non-auto-negotiating device (forced

technology), and it is then required that Auto-Negotiation or

re-Auto-Negotiation be initiated via software, bit 12 (Auto-Ne-

gotiation Enable) of the Basic Mode Control Register (BMCR)

must first be cleared and then set for any Auto-Negotiation

function to take effect.

9.2.6 Auto-Negotiation Complete Time

Parallel detection and Auto-Negotiation take approximately

2-3 seconds to complete. In addition, Auto-Negotiation with

next page should take approximately 2-3 seconds to com-

plete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full de-

scription of the individual timers related to Auto-Negotiation.

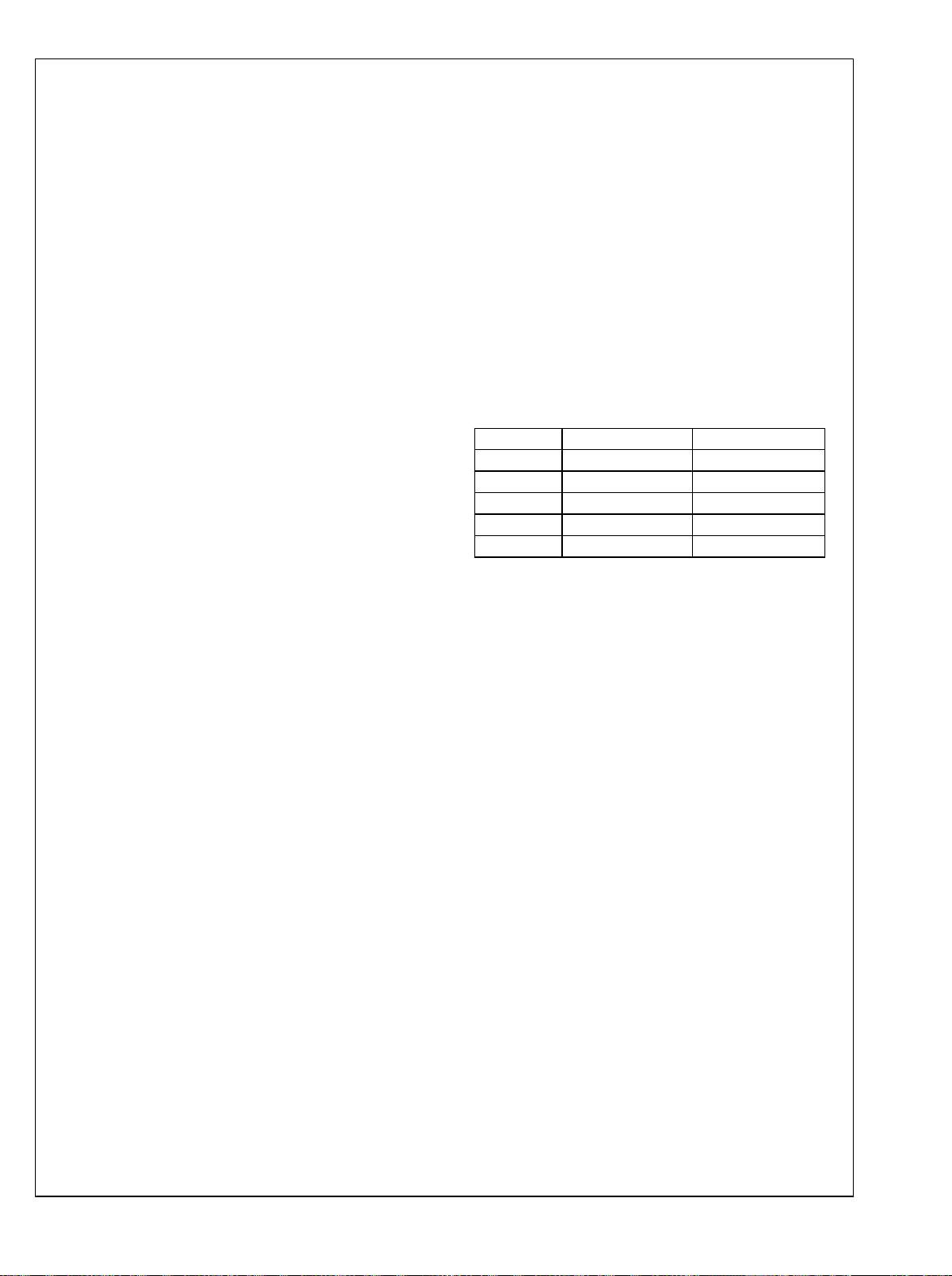

9.3 AUTO-MDIX

When enabled, this function utilizes Auto-Negotiation to de-

termine the proper configuration for transmission and recep-

tion of data and subsequently selects the appropriate MDI pair

for MDI/MDIX operation. The function uses a random seed to

control switching of the crossover circuitry. This implementa-

tion complies with the corresponding IEEE 802.3 Auto-Nego-

tiation and Crossover Specifications.

Auto-MDIX is enabled by default and can be configured via

PHYCR (19h) register, bits [15:14].

Neither Auto-Negotiation nor Auto-MDIX is required to be en-

abled in forcing crossover of the MDI pairs. Forced crossover

can be achieved through the FORCE_MDIX bit, bit 14 of

PHYCR (19h) register.

NOTE: Auto-MDIX will not work in a forced mode of operation.

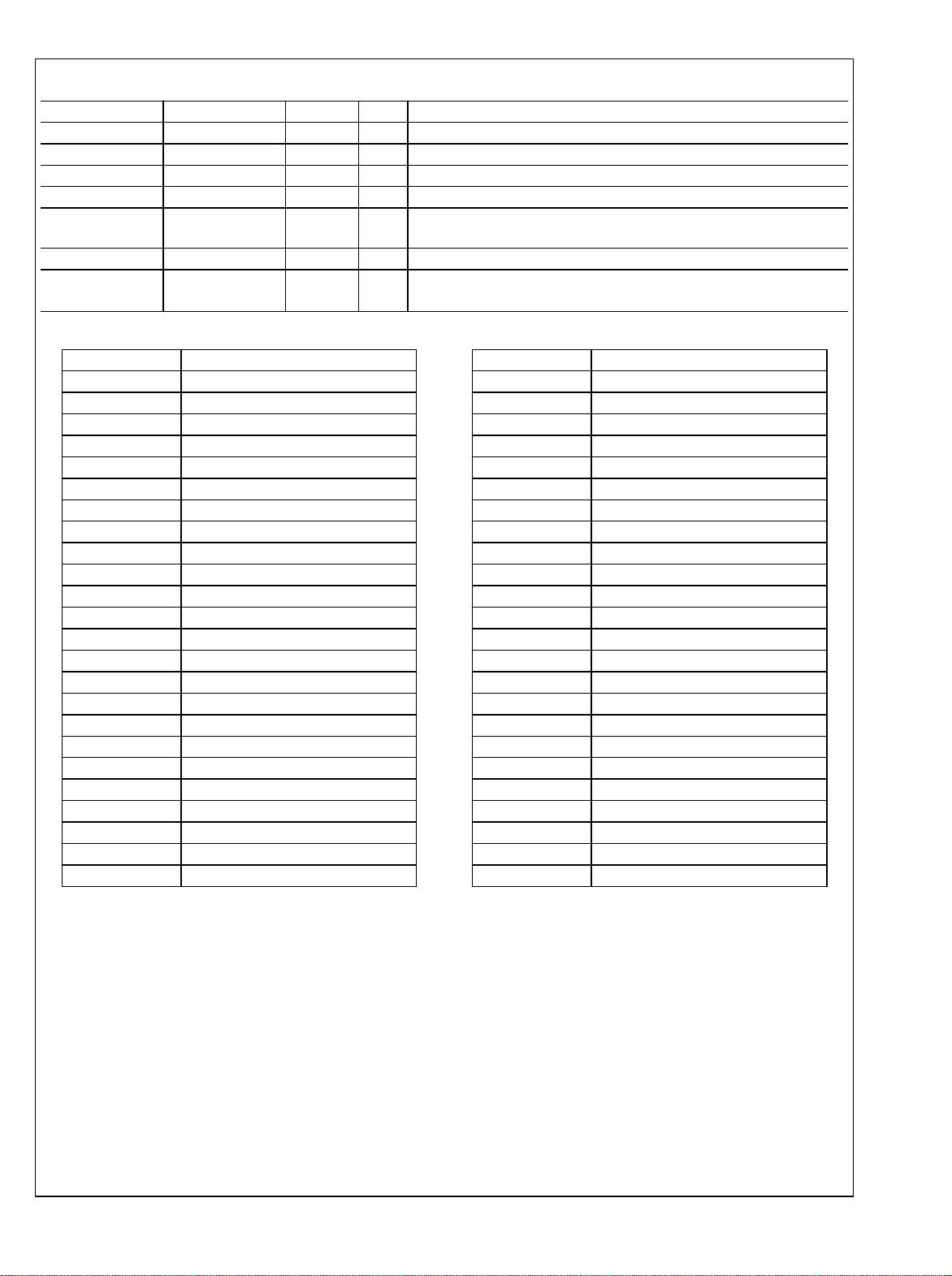

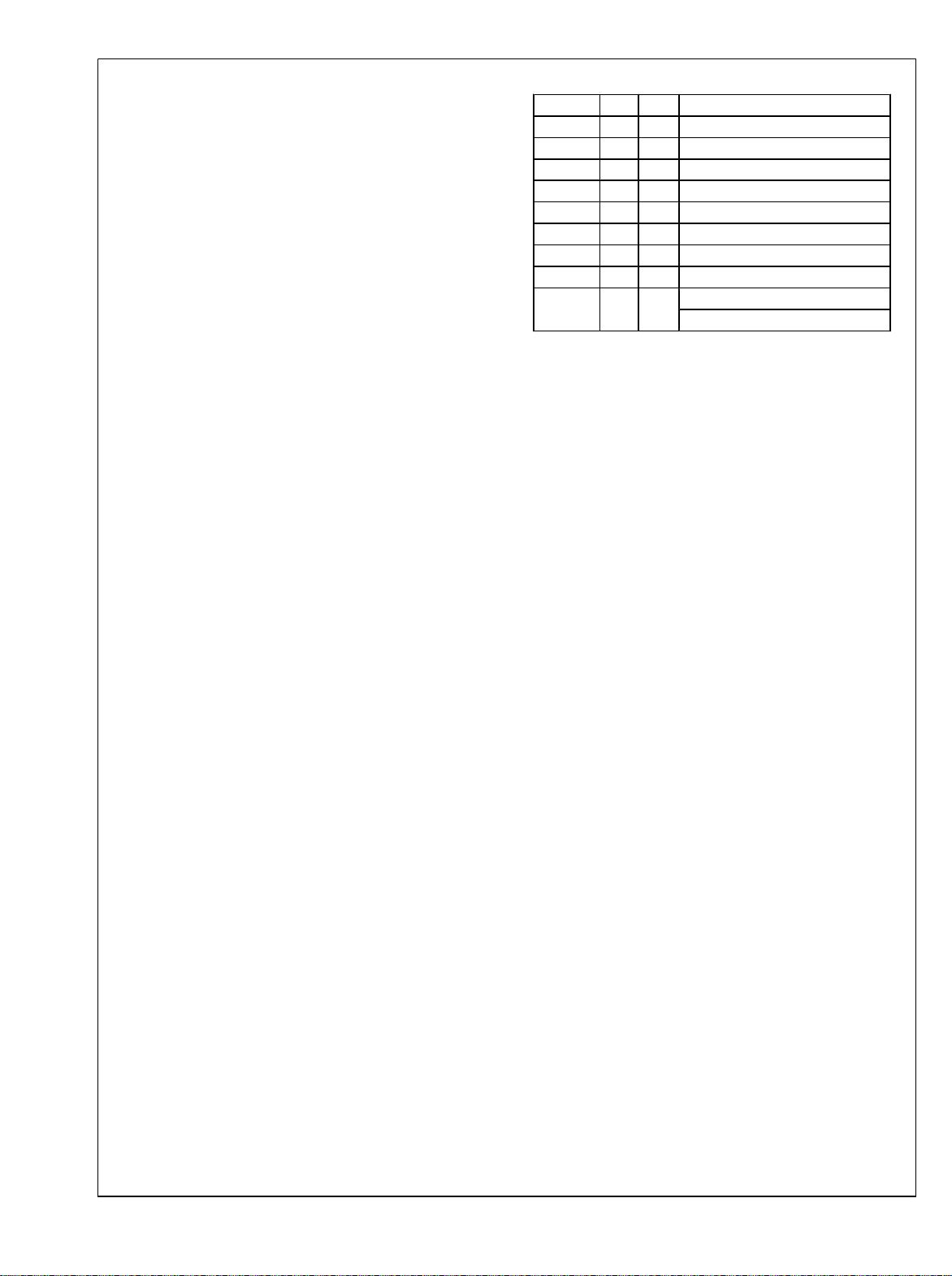

9.4 PHY ADDRESS

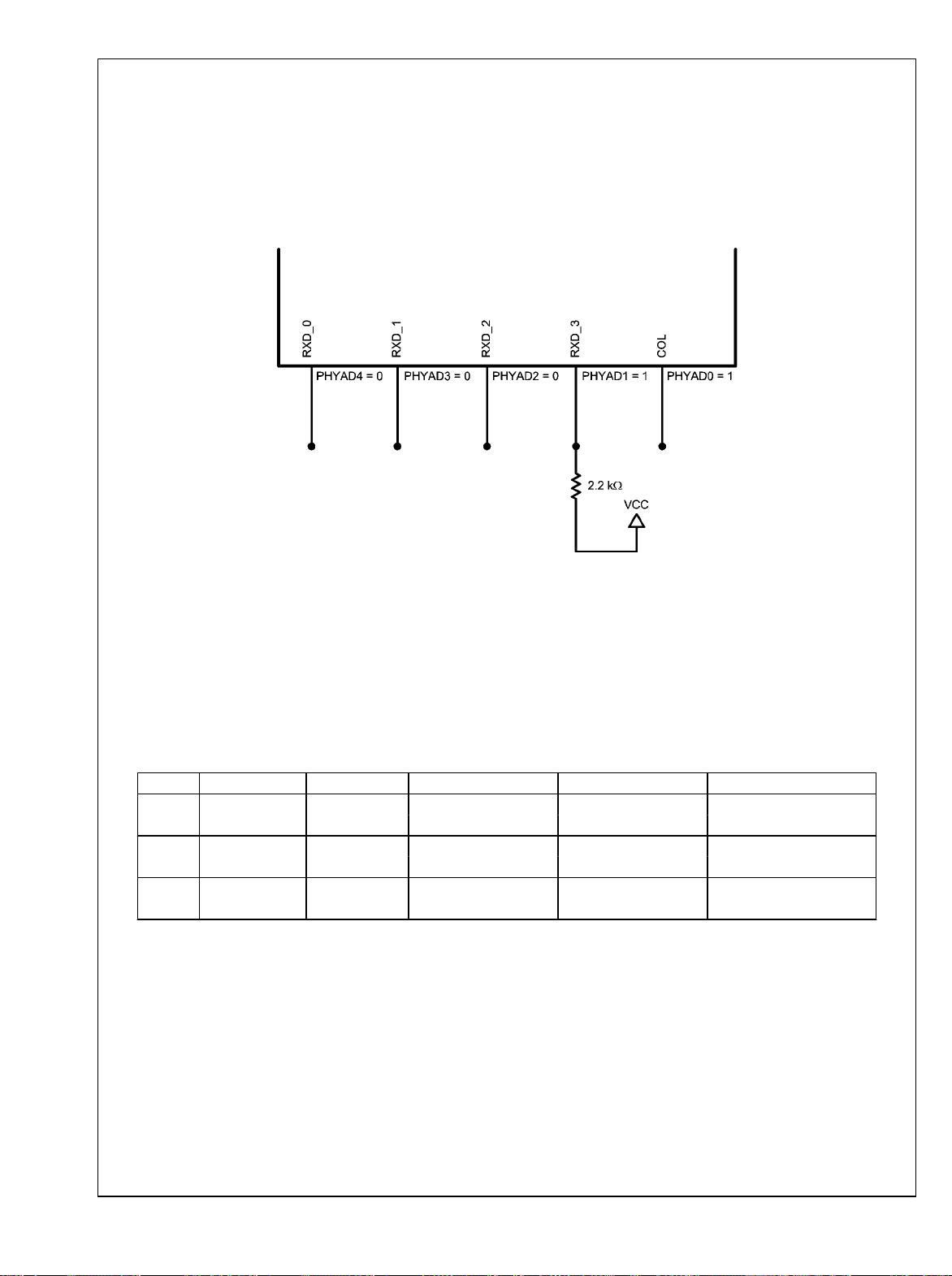

The five PHY address strapping pins are shared with the RXD

[3:0] pins and COL pin as shown below.

TABLE 2. PHY Address Mapping

Pin # PHYAD Function RXD Function

42 PHYAD0 COL

43 PHYAD1 RXD_3

44 PHYAD2 RXD_2

45 PHYAD3 RXD_1

46 PHYAD4 RXD_0

The DP83640 can be set to respond to any of 32 possible

PHY addresses via strap pins. The information is latched into

the PHYCR register (address 19h, bits [4:0]) at device power-

up and hardware reset. Each DP83640 or port sharing an

MDIO bus in a system must have a unique physical address.

The DP83640 supports PHY Address strapping values 0

(<00000>) through 31 (<11111>). Strapping PHY Address

0 puts the part into Isolate Mode. It should also be noted

that selecting PHY Address 0 via an MDIO write to PHYCR

will not put the device in Isolate Mode. See for more infor-

mation.

For further detail relating to the latch-in timing requirements

of the PHY Address pins, as well as the other hardware con-

figuration pins, refer to the Reset summary in Section 12.0

Reset Operation.

Since the PHYAD[0] pin has weak internal pull-up resistor and

PHYAD[4:1] pins have weak internal pull-down resistors, the

default setting for the PHY address is 00001 (01h).

Refer to Figure 2for an example of a PHYAD connection to

external components. In this example, the PHYAD strapping

results in address 00011 (03h).

9.4.1 MII Isolate Mode

It is recommended that the user have a basic understanding

of Clause 22 of the 802.3u standard.

The DP83640 can be put into MII Isolate Mode by writing a 1

to bit 10 of the BMCR register. Strapping the PHY Address to

0 will force the device into Isolate Mode when powered up. It

should be noted that selecting Physical Address 0 via an

MDIO write to PHYCR will not put the device in the MII isolate

mode.

When in the MII Isolate Mode, the DP83640 does not respond

to packet data present at TXD[3:0] and TX_EN inputs and

presents a high impedance on the TX_CLK, RX_CLK,

RX_DV, RX_ER, RXD[3:0], COL, and CRS/CRS_DV outputs.

19 www.national.com

DP83640