"16340198孙肖冉数电实验报告:JK触发器异步计数器设计与仿真图分析"

需积分: 0 35 浏览量

更新于2024-03-25

收藏 3.18MB DOCX 举报

16340198 Sun Xiaoran Digital Experiment Report 1; (2) Simulation diagram: corresponding waveform diagram: from top to bottom are CP-Q0-Q1-Q2-Q3

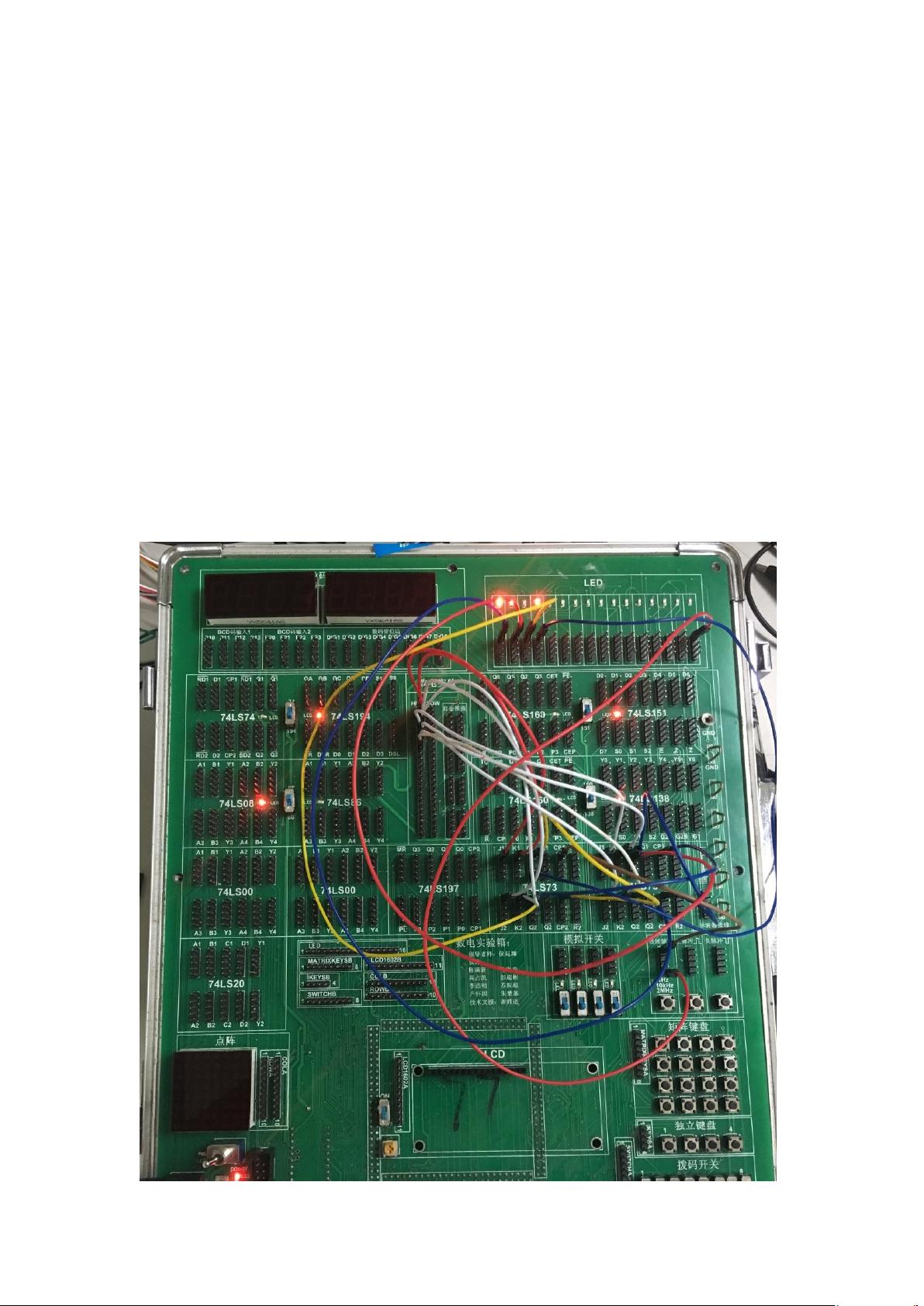

(1) Function of 74LS194: Right shift simulation diagram: corresponding waveform diagram from top to bottom corresponds to CP, Q0, Q1, Q2, Q; "Digital Circuits and Logic Design" Experimental Report of the class Education Three Class College School of Data Science and Computer Science Student Number 16340198 Student Name Sun Xiaoran December 6, 2017 1. Purpose of the Experiment Familiarize with the logical function of J-K flip-flops and master the asynchronous counter and synchronous counter composed of J-K flip-flops. 2. Experimental Instruments and Devices 1. Experimental box, multimeter, oscilloscope 2. 74LS73, 74LS00, 74LS08, 74LS20 3. Experimental Content 1. Design a 16-bit hexadecimal asynchronous adder using JK flip-flops, and observe and record the CP and waveform output of each bit with a logic analyzer. (1) Design process: State table of 16-bit addition counter: Q3Q2Q1Q00000000100100011010001010110011110001001101010111100110111101111 Asynchronous counter, 4 JK flip-flops are not the same clock signal, when Qi goes from 1 to 0, carry out the flip to achieve carry; we change the next flip-flop clock signal by changing (J, K are both 1; ".

2022-08-08 上传

2012-04-14 上传

2022-08-08 上传

2022-08-03 上传

2022-08-03 上传

2022-08-08 上传

士多霹雳酱

- 粉丝: 22

- 资源: 299

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析