异步M进制计数器设计与实现

版权申诉

PPTX格式 | 29.7MB |

更新于2024-06-25

| 68 浏览量 | 举报

"该资源是关于数字电子技术的PPT,重点讲述了异步N进制计数器的设计和实现,包括二进制计数器、异步任意M进制计数器的两种实现方法(脉冲反馈法和阻塞反馈法),以及具体的10进制计数器的实例分析。"

在数字电子技术中,计数器是一种常见的时序逻辑电路,用于对输入的脉冲进行计数,从而产生不同频率的输出。异步N进制计数器是一种计数器,其计数模(即最大计数值)不是2的幂次。在给定的资源中,主要讨论了如何设计和实现这种计数器。

首先,为了得到八分频的输出波形,即输出频率为输入频率的八分之一,我们需要一个8进制计数器,因为它会每接收8个脉冲才翻转一次状态。N位异步二进制加法计数器的构建方法是使用N个T'触发器,并将低位的进位信号连接到相邻高位的时钟输入,这样随着每个脉冲的来临,计数器会按照二进制数的增法规则依次改变状态。

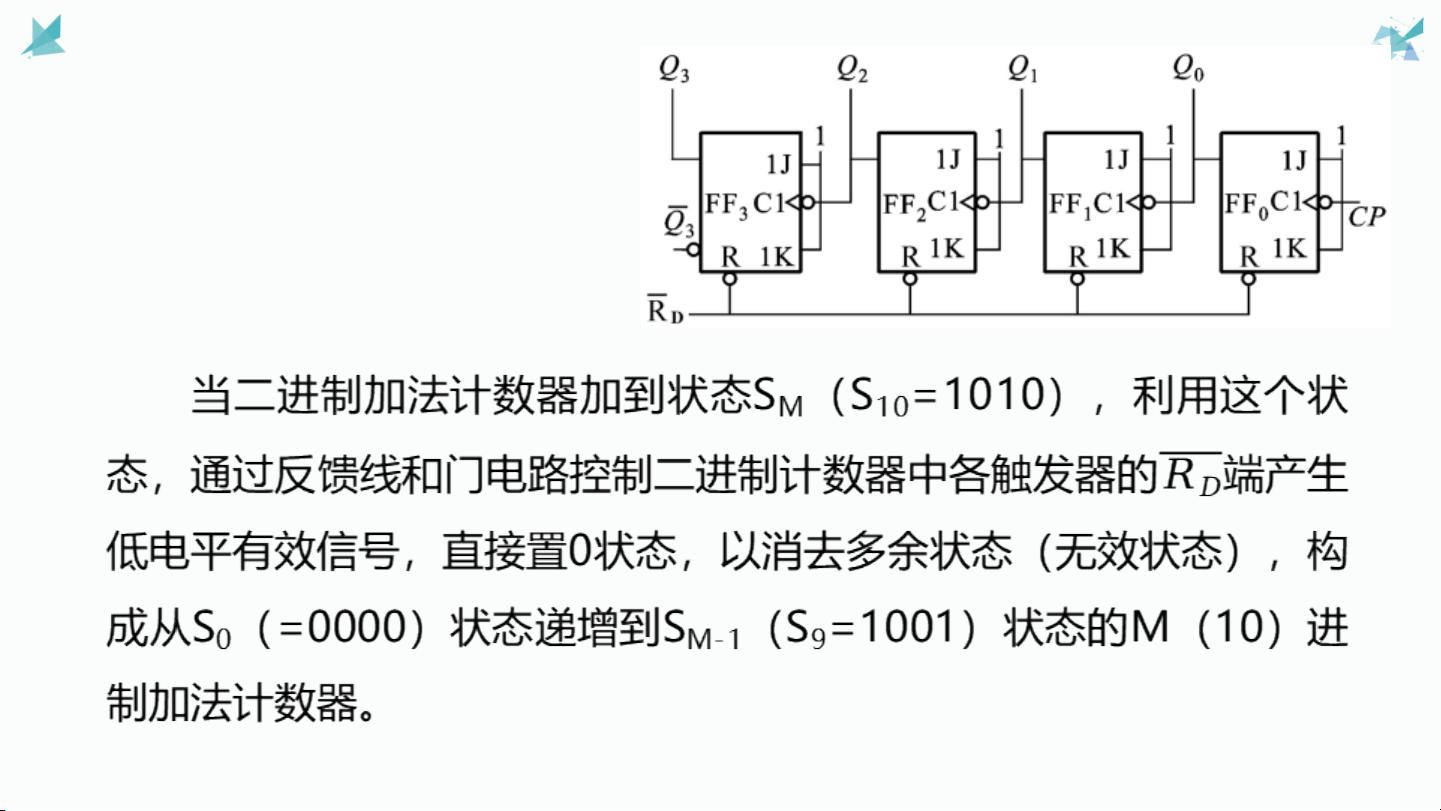

异步任意M进制计数器的实现通常有两种方法:脉冲反馈法和阻塞反馈法。脉冲反馈法是通过反馈线路和门电路控制二进制计数器中某些触发器的输入,消除多余的二进制状态,以达到M进制计数的目的。例如,10进制计数器需要4位二进制计数器,因为2^4=16,大于10,可以覆盖所有有效的10进制数。当计数达到1001(二进制)时,通过反馈机制将计数器复位回0000。

10进制计数器的状态转换表、状态转换图和逻辑电路图详细展示了这一过程。状态转换表列出了所有可能的状态和它们之间的转换,状态转换图直观地表示了状态之间的路径,而逻辑电路图则揭示了实际电路的组成,包括与非门等基本逻辑门。

阻塞反馈法则是通过在特定状态阻止时钟脉冲传递到某些触发器,使得计数器跳过无效状态,直接进入下一个有效状态。这种方法同样适用于构建任意M进制计数器,但具体电路设计会有所不同。

时序图则展示了计数器在不同时间点的状态变化,这对于理解和验证计数器的正确性至关重要。通过这些图表和分析,我们可以理解如何设计和实现异步M进制计数器,并能应用到其他M值的计数器设计中。

这份资料详细讲解了数字电子技术中的异步M进制计数器,包括理论基础、设计思路、实现方法和实例分析,对于学习数字逻辑电路和时序逻辑设计的人员来说,是一份非常有价值的参考资料。

相关推荐

知识世界

- 粉丝: 376

最新资源

- just-uuid4: 简单快速生成UUID v4的JavaScript工具

- MATLAB实现图像转AVI格式的编程方法

- OpenCAL:跨平台开源动画技术解析

- Phenny-Mumble-Plugin: 利用ICE技术实现Python IRC机器人与Murmur的交互

- YAPF: Python代码智能格式化工具详解

- CSS3和SVG打造精美镂空效果图标按钮

- MLA格式人文论文LaTeX模板解析与使用指南

- 深入理解C++模板与STL库

- 电子商务应用内计费Java示例分析

- NSU/AIUB/达卡/BRACU大学生CGPA计算器应用

- CxGo: 高效实现C到Go代码转换的工具

- JavaScript领域的windsorview_offline功能与应用

- rollup-plugin-screeps:简化代码上传至Screeps平台的Rollup插件

- wxListbook控件页面切换使用示例

- 披萨爱好者的新选择:Mini Pizza JS项目入门指南

- Pure360天气测试实践:单元测试与API调用