没有合适的资源?快使用搜索试试~ 我知道了~

首页第四版全面升级:数字逻辑设计涵盖新主题与应用

《数字逻辑设计第四版》是一本全面更新后的教材,旨在教授学生最新的数字系统理论和技术。本书覆盖了广泛的主题,包括但不限于EBCDIC(Extended Binary Coded Decimal Interchange Code)编码、格雷码(一种二进制编码方式,常用于减少相邻码元之间的差异),以及实际应用中的触发器(flip-flops)和编码器(如线性和旋转编码器)。新增章节探讨了内存元素(如RAM和FPGA)的设计与应用,强化了故障诊断部分,并特别介绍了数字组件与模拟电压接口的理论。 第1章详尽介绍了数字逻辑的基础概念,包括介绍、术语、基本运算、进位链、补码表示、二进制和十进制运算、加法和减法操作,以及图形化展示的二进制运算。随后,作者详细讲解了浮点数运算、最后一位的处理,以及定点和浮点数的差异。此外,错误检测和纠正技术,以及编码转换规则,都是这一章的重要内容。 第2章深入到二进制逻辑设计的具体实现,包括介绍逻辑门电路,如与门、或门和非门,以及真值表的构建。章节还涉及译码器的工作原理、译码逻辑以及与ASCII代码的关联分析。这部分内容对于理解硬件层面的逻辑设计至关重要。 整本书以易于理解的方式呈现,并紧跟现代课程的需求,是HND/一年级学生的理想学习资源。通过《数字逻辑设计第四版》,读者能够掌握从基础原理到实践应用的完整知识体系,对数字系统的设计和维护有着深厚的理解。

资源详情

资源推荐

6 Digital logic design

Subtraction

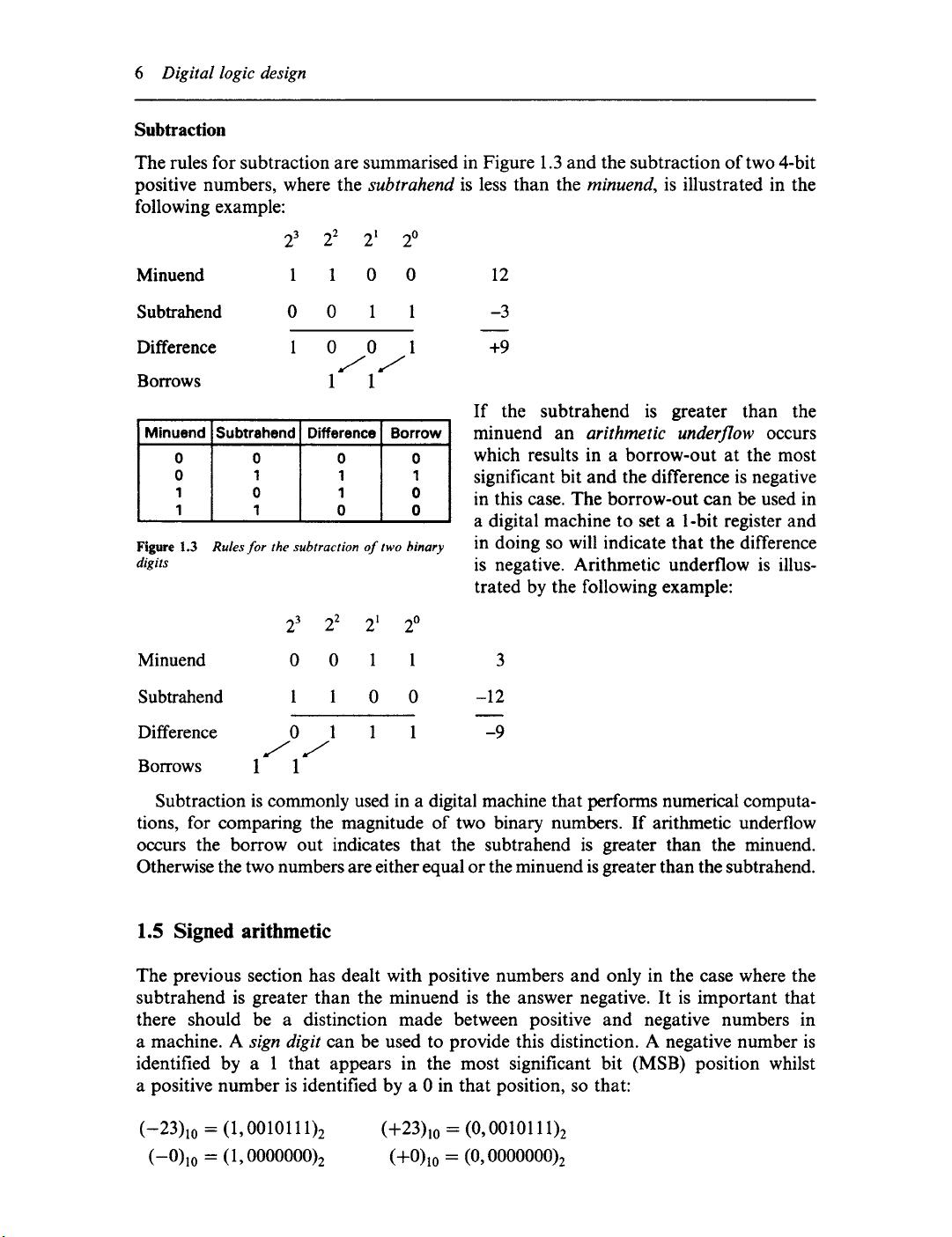

The rules for subtraction are summarised in Figure 1.3 and the subtraction of two 4-bit

positive numbers, where the

subtrahend

is less than the

minuend,

is illustrated in the

following example:

2 3 2 2

21 2 0

Minuend 1 1 0 0 12

Subtrahend 0 0 1 1 -3

Difference 1 0 0 1 +9

.1,"/"

Borrows 1 1

Minuend Subtrahend

0 0

0 1

1 0

1 1

Difference Borrow

0 0

1 1

1 0

0 0

Figure 1.3

Rules for the subtraction of two binary

digits

2 3 2 2

21 2 0

If the subtrahend is greater than the

minuend an

arithmetic underflow

occurs

which results in a borrow-out at the most

significant bit and the difference is negative

in this case. The borrow-out can be used in

a digital machine to set a 1-bit register and

in doing so will indicate that the difference

is negative. Arithmetic underflow is illus-

trated by the following example:

Minuend 0 0 1 1

Subtrahend 1 1 0 0 -12

Difference 0 1 1 1

.,,/i,,,

Borrows 1 1

-9

Subtraction is commonly used in a digital machine that performs numerical computa-

tions, for comparing the magnitude of two binary numbers. If arithmetic underflow

occurs the borrow out indicates that the subtrahend is greater than the minuend.

Otherwise the two numbers are either equal or the minuend is greater than the subtrahend.

1.5 Signed arithmetic

The previous section has dealt with positive numbers and only in the case where the

subtrahend is greater than the minuend is the answer negative. It is important that

there should be a distinction made between positive and negative numbers in

a machine. A

sign digit

can be used to provide this distinction. A negative number is

identified by a 1 that appears in the most significant bit (MSB) position whilst

a positive number is identified by a 0 in that position, so that:

(-23)10

= (1,0010111)2

(-0)~0 = (1,0000000)2

(+23)10 = (0, O010111)2

(+O)lo = (0, 0000000)2

Number systems and codes 7

....

This is termed

signed magnitude

representation. The range of numbers available

with an 8-bit signed integer is from -127 to + 127 with two possible representations

for zero.

Because the design of a logic circuit capable of numerical computation in signed

magnitude representation is somewhat complex it is rarely used. In practice, numerical

computation in a machine is performed using

complement arithmetic.

1.6 Complement arithmetic

This is a powerful yet simple technique which minimises the hardware implemen-

tation of signed arithmetic operations in a digital machine. In practice, when using

complement arithmetic, the process of subtraction becomes one of addition.

In any number system two complements are available. In the binary system they are

(a) the

2's complement

or

radix complement,

and (b)

1 's complement

or

diminished radix

complement.

For the decimal system they are: (a) the

1O's complement

or

radix com-

plement

and (b) the

9's complement

or

diminished radix complement.

It is worth noting

that the use of the l's complement in the binary system raises certain hardware

implementation difficulties so that signed arithmetic processes are invariably per-

formed using 2's complement notation.

1.7 Complement representation for binary numbers

The 2's complement of a binary number X is defined by the equation

IX ]2 -"

2" - X

where

[X]2

is the 2's complement representation and n is the number of binary digits

contained in X. For X = 1010 and n = 4 the 2's complement is given by:

IX]2 -~

2 4-

1010

= 10000- 1010

--0110

Two other methods are available for determining the 2's complement of X. In the

first method, all the digits are inverted and a 1 is added in the least significant place.

For the second method, the lowest order 1 in X is sensed, and all succeeding higher

digits are inverted. Examples of these two methods follow:

Method 1 Method 2

X= 1010 X = 1010

0101 Invert /

Invert Sense

1 Add

[X]2 =0110

[X]2 = O110

8 Digital logic design

In the 2's complement representation a number is positive if its MSB is 0.

Alternatively, it is negative if its MSB is 1. Examples of two 8,bit numbers in 2's

complement form are given below"

+(19)10 = 0,0010011 -(19)10 = 1,1101101

S.D. Magnitude X S.D. 2's comp [X]2

An n-bit 2's complement number can be changed into an m-bit one, where m > n, by

adding copies of the sign digit to the left of the MSB of the n-bit number. This process

called

sign extension

is illustrated in the following examples:

n=4 m=8

+7 = 0,111 = 0,0000111

-3 = 1,101 = 1,1111101

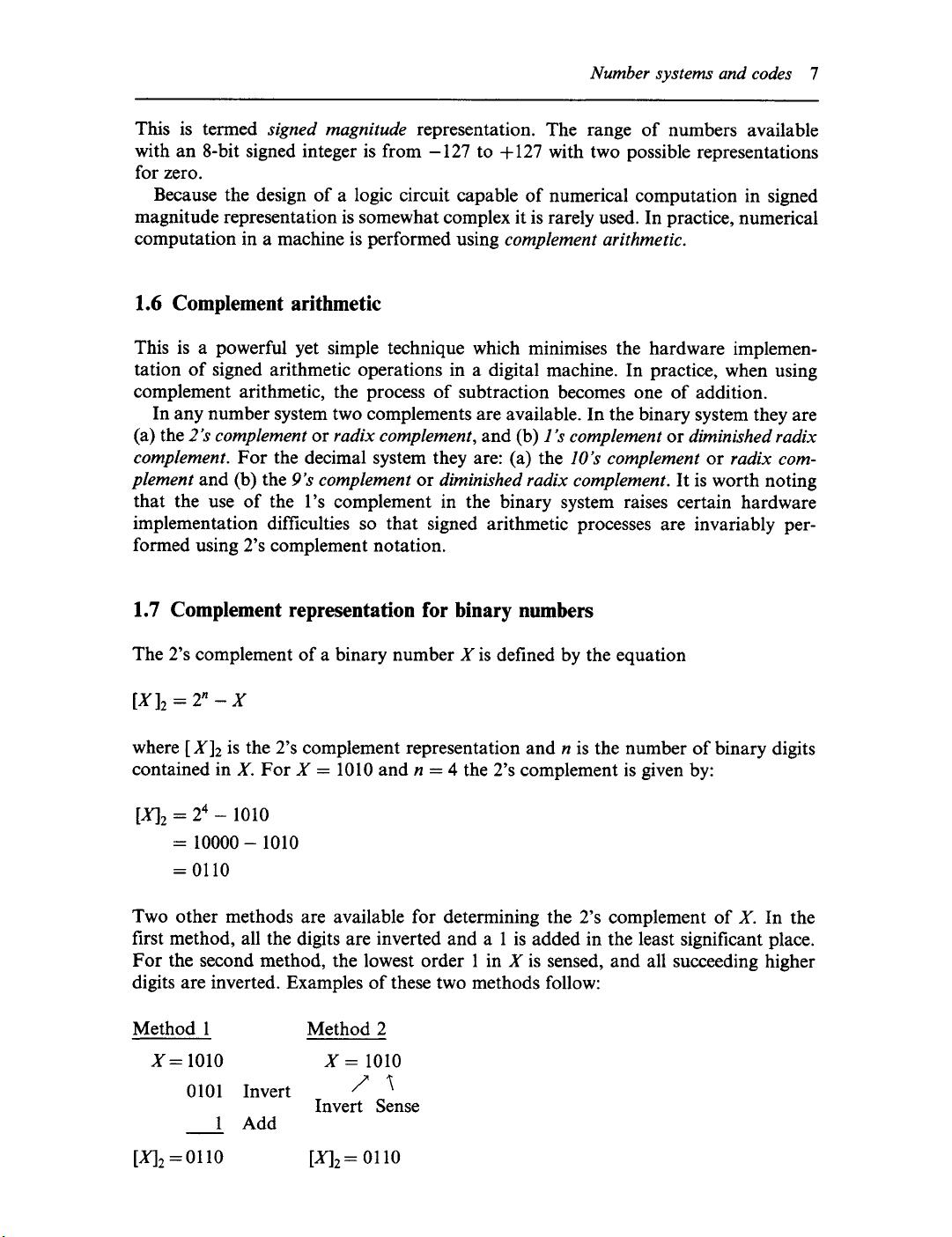

The table shown in Figure 1.4 gives some of the 8-bit numbers available in 2's

complement form with their corresponding decimal values. The range of these numbers

is from -128 to + 127 and it will be noticed that it is not symmetrical since there is no

2's complement number corresponding to -128. It will also be observed that zero in

this system is regarded as positive since its sign bit is 0.

The diminished radix complement, as in all number systems, is one less than the

radix complement. In the binary system the l's complement [X] l is one less than the 2's

complement and is found by inverting all the digits in the binary number, as shown in

the following example"

X = 1010

[X] l - 0101 Invert

Weighting,

-27

Value -128

=

0

0

0

0

' 1

1

1

2 e 2 s 24

64 32 16

= =

1 1 1

1 1 1

1 0 0

0 0 0

0 0 0

1 1 1

1 1 1

0 0 0

= =

23

8

1

1

0

~

o

0

1

1

0

22 . 21 . 20 I

Decimal

4 2 1 i

value

= 9

1 1 1 +127

1 1 0 +128

i

0 0 0 +64

i

J =

0 0 1 +1

0 0 0 +0

1 1 1 -1

1 1 0 -2

0 0 0 -128

, , 9

Figure

1.4 Tabular representation of 8-bit 2's complement numbers

Number systems and codes 9

Weighting

2 7 2 8 2 5 2 4 2 3 2 2 2 ~

0 1 1 1 1 1 1

0 1 1 1 1 1 1

0 1 0 0 0 0 0

2 o

1

0

Dec. value

+127

+126

0 +64

0 0 0 0 0 0 0 1 +1

0 0 0 0 0 0 0 0 +0

1 1 1 1 1 1 1 1 -0

1 1 1 1 1 1 1 0 -1

1 1 1 1 1 1 0 1 -2

1 0 0 0 0 0 0 0 -127

,,

Figure

1.5

Tabular representation of 8-bit l's complement numbers

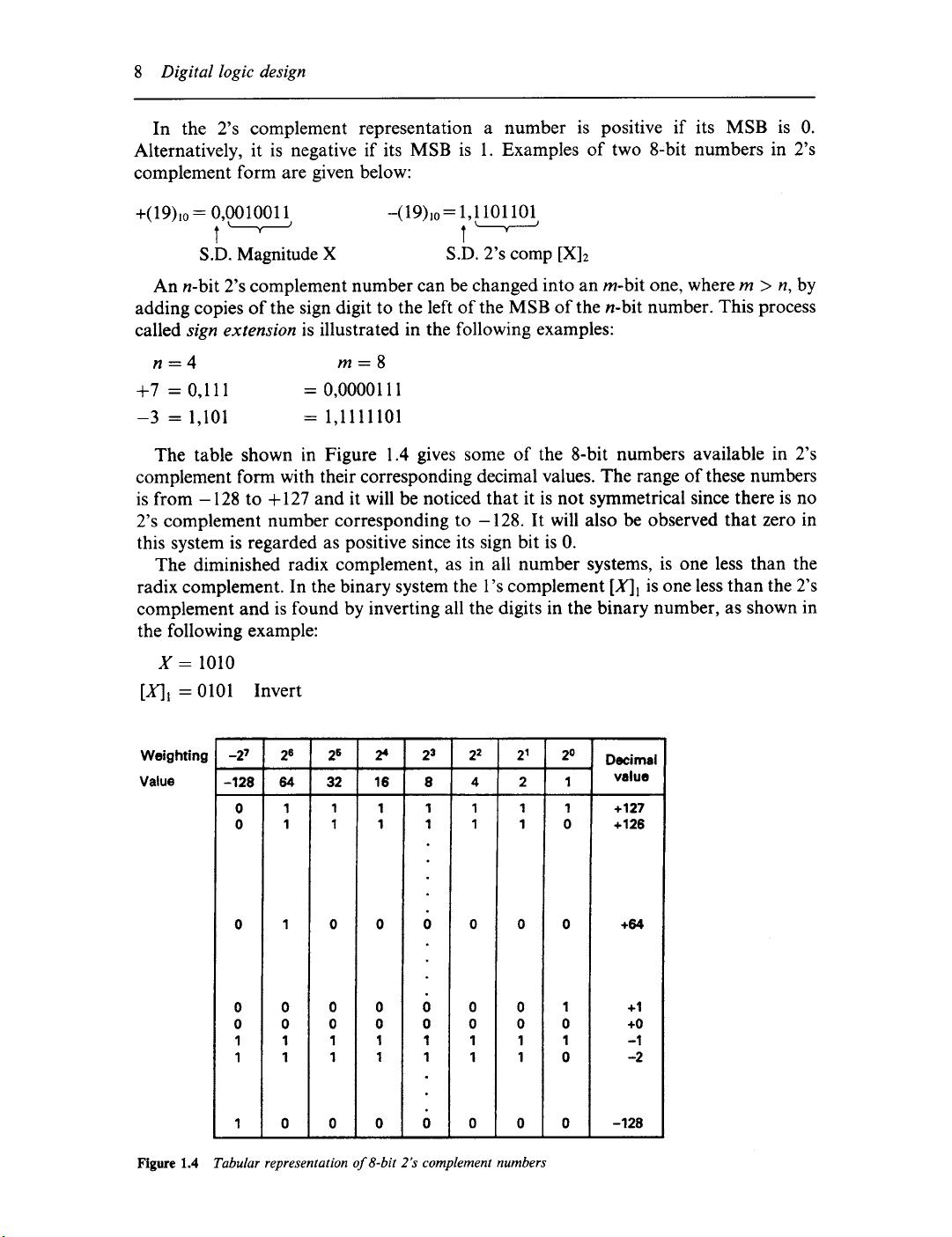

A sign digit is added in the most significant place to distinguish between positive and

negative numbers, 0 for a positive number and 1 for a negative number. The com-

plement is only taken in the case of negative numbers. Examples of 8-bit numbers in

the l's complement representation follow:

-72 - 1,0110111

+25 - 0, 0011001

Although complementation is easily achieved in hardware, the system has the dis-

advantage that there are both positive and negative representations of zero and in the

cases of some numerical computations an end-about carry is generated which has to be

added in at the least significant place. For these reasons the 2's complement represen-

tation is generally preferred for numerical computations in a digital machine.

The table in Figure 1.5 gives a list of some of the 8-bit numbers available in l's

complement form with their corresponding decimal values. The range of values is from

- 127

to

+ 127.

1.8 The validity of l's and 2's complement arithmetic

By definition

[X]2 --

2 n

--

X and the subtraction Y - X where Y and X are both binary

integers may be written as the addition of Y and the 2's complement of X.

Hence

Y-X= Y+ [X]2 - 2 n

where n is the number of binary digits contained in X.

The l's complement [X]I is always one less than the 2's complement so that

[X]2--[X]I-~-

1.

To establish that [X]l is the logical inversion of X it is only necessary to show that

X-X=O-X+X+ 1--2 n

or

X+X+ 1

--2 n

10

Digital logic design

_ w

Assuming X - 1010 and X - 0101 then the sum of X, X and 1 is

1010 X

0101 X

1

10000

and the underlined digit in this sum has the significance of 2" and it has been shown

that X + X + 1 - 2 n as required.

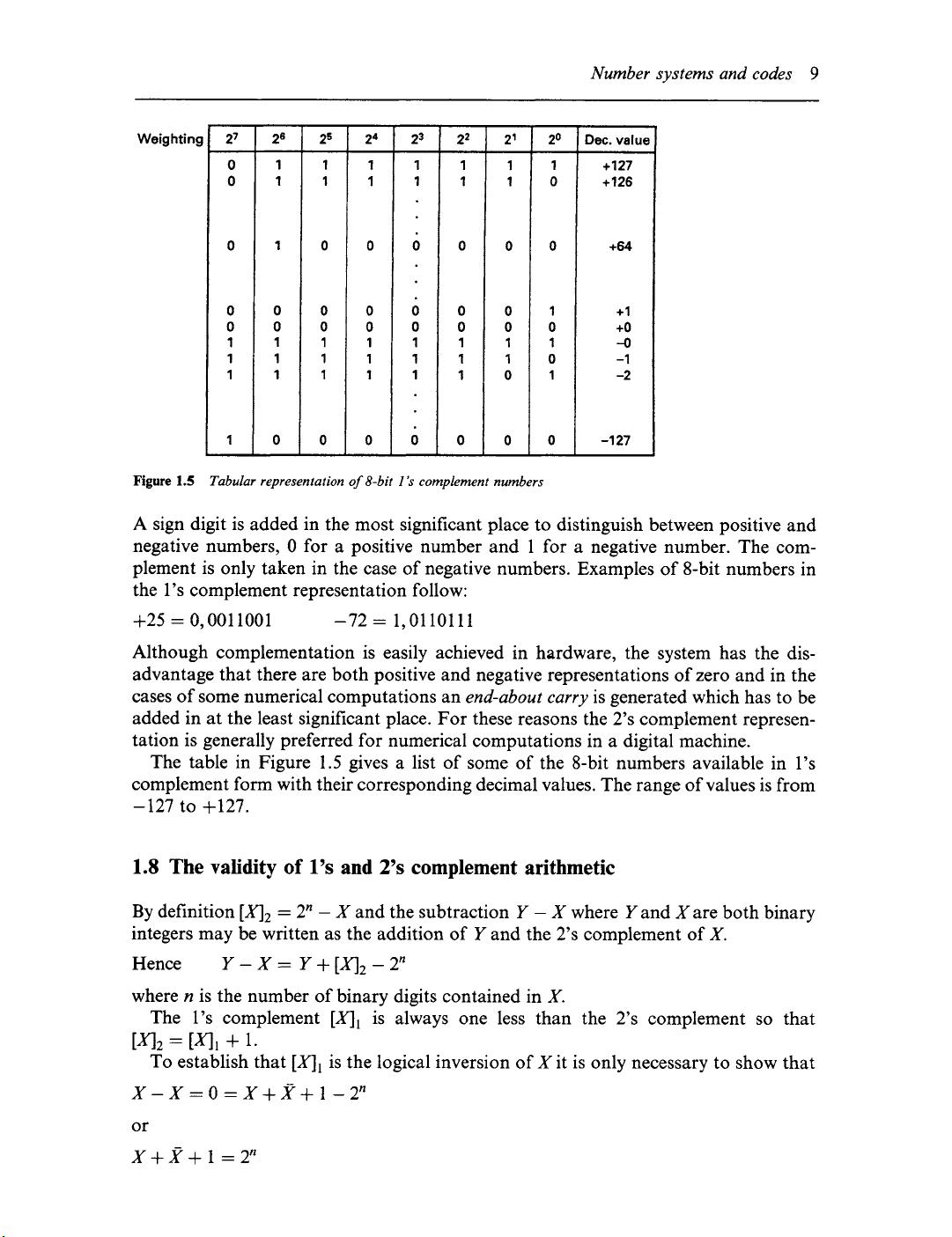

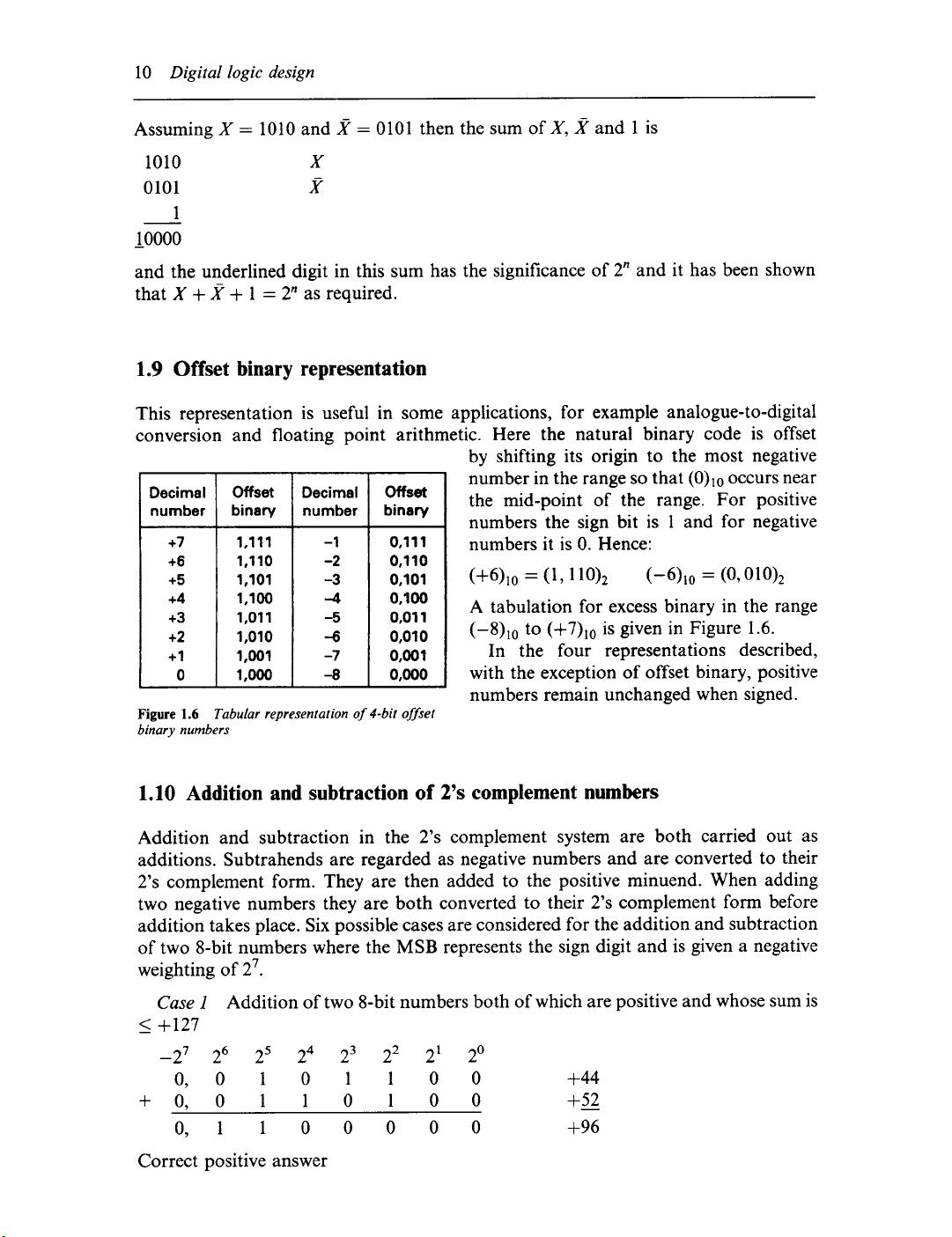

1.9 Offset binary representation

This representation is useful in some applications, for example analogue-to-digital

conversion and floating point arithmetic. Here the natural binary code is offset

Decimal

number

+7

+6

+5

+4

+3

+2

+1

0

Offset

binary

1,111

1,110

1,101

1,100

1,011

1,010

1,001

1,000

Decimal

number

-1

-2

-3

-4

-5

-6

-7

-8

Offset

binary

0,111

0,110

0,101

0,100

0,011

0,010

0,001

o,ooo

Figure 1.6 Tabular representation of 4-bit offset

binary numbers

by shifting its origin to the most negative

number in the range so that (0)~o occurs near

the mid-point of the range. For positive

numbers the sign bit is 1 and for negative

numbers it is 0. Hence"

(+6)10 = (1, 110)2 (-6)10 = (0, 010)2

A tabulation for excess binary in the range

(-8)10 to (+7)10 is given in Figure 1.6.

In the four representations described,

with the exception of offset binary, positive

numbers remain unchanged when signed.

1.10 Addition and subtraction of 2's complement numbers

Addition and subtraction in the 2's complement system are both carried out as

additions. Subtrahends are regarded as negative numbers and are converted to their

2's complement form. They are then added to the positive minuend. When adding

two negative numbers they are both converted to their 2's complement form before

addition takes place. Six possible cases are considered for the addition and subtraction

of two 8-bit numbers where the MSB represents the sign digit and is given a negative

weighting of 27 .

Case

1

< +127

m

Addition of two 8-bit numbers both of which are positive and whose sum is

_27 26

0, 0

0, 0

0,

1

2 5 2 4 2 3

22 21 20

1 0 1 1 0 0

1 1 0 1 0 0

1 0 0 0 0 0

+44

+52

+96

Correct positive answer

剩余528页未读,继续阅读

Artemis_Melete

- 粉丝: 1

- 资源: 35

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 最优条件下三次B样条小波边缘检测算子研究

- 深入解析:wav文件格式结构

- JIRA系统配置指南:代理与SSL设置

- 入门必备:电阻电容识别全解析

- U盘制作启动盘:详细教程解决无光驱装系统难题

- Eclipse快捷键大全:提升开发效率的必备秘籍

- C++ Primer Plus中文版:深入学习C++编程必备

- Eclipse常用快捷键汇总与操作指南

- JavaScript作用域解析与面向对象基础

- 软通动力Java笔试题解析

- 自定义标签配置与使用指南

- Android Intent深度解析:组件通信与广播机制

- 增强MyEclipse代码提示功能设置教程

- x86下VMware环境中Openwrt编译与LuCI集成指南

- S3C2440A嵌入式终端电源管理系统设计探讨

- Intel DTCP-IP技术在数字家庭中的内容保护

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功