5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

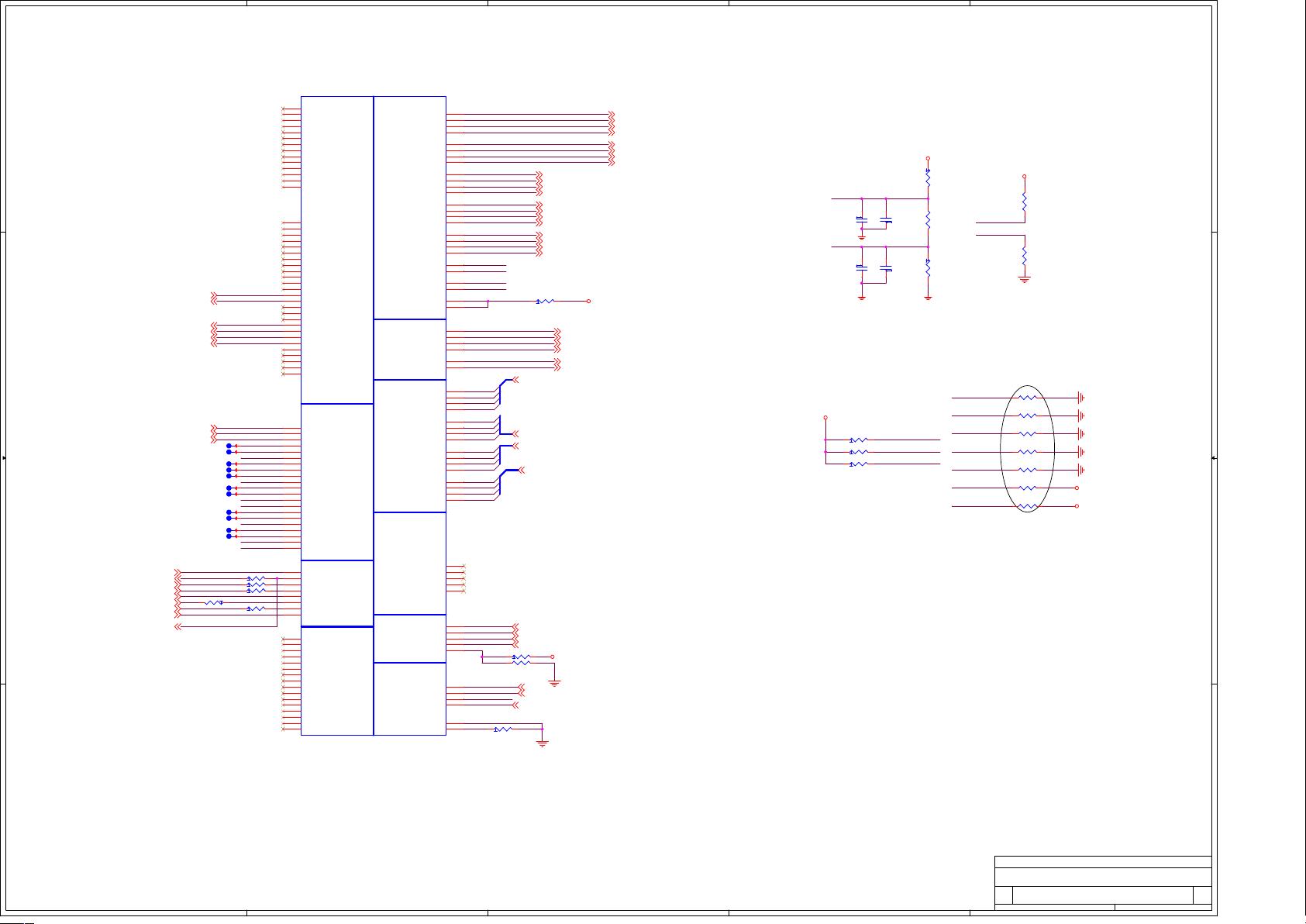

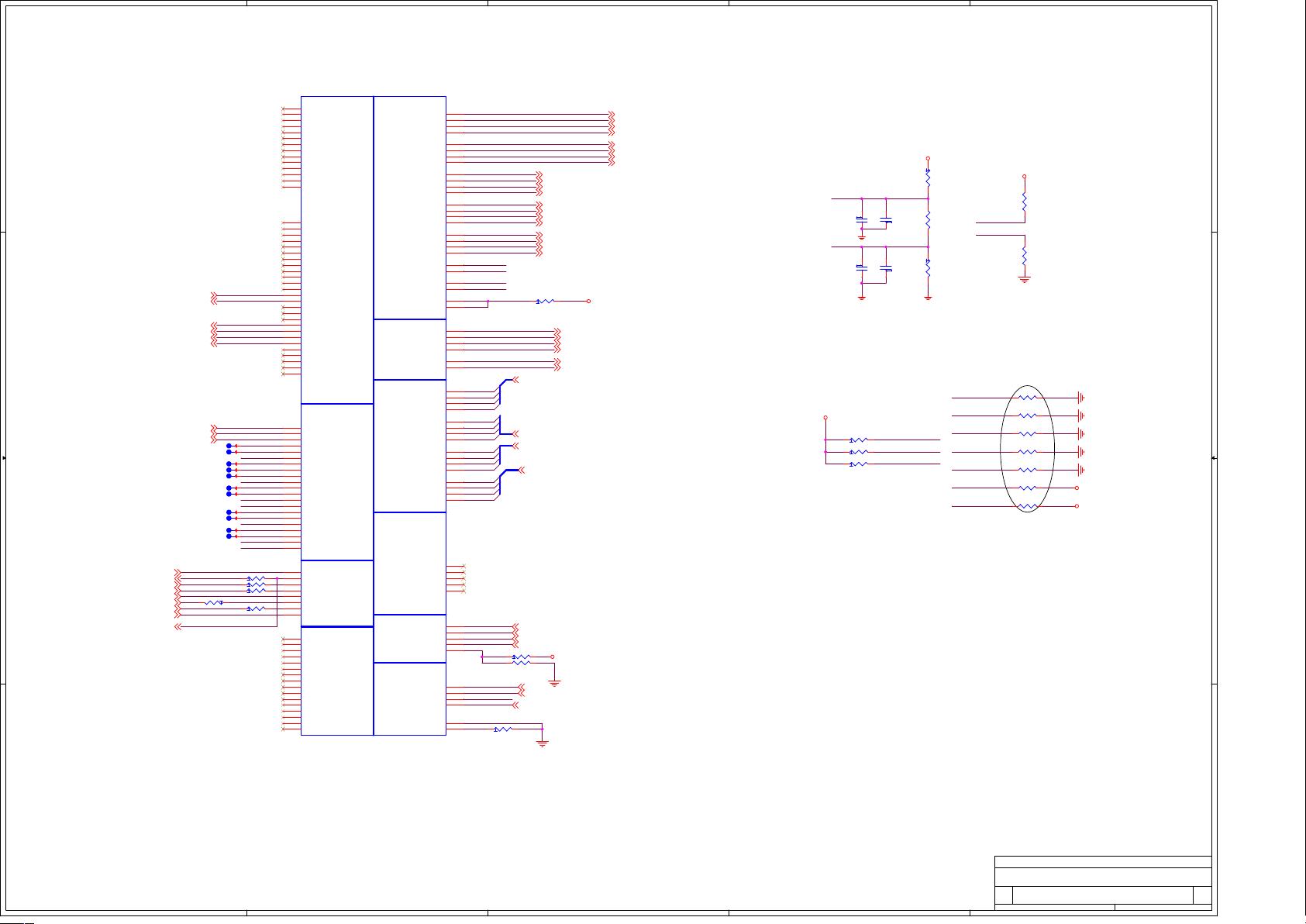

< 0.1" . 15mils/15mils space

use 1% R

GMCH Strap pin

Change from 80.6 to 20 ref Intel 1.201

2.MCH_CFG_9 PCI Exp Graphics Lane: Low =Reserved,High=Normal operation

4.MCH_CFG_16 FSB Dynmic ODT: Low=Dynamic ODT Disabled,

High=Dynamic ODT Enabled.

1.MCH_CFG_5 Low = DMI X2, High=DMIX4

5.MCH_CFG_18 VCC Select: LOW=1.05V, High=1.5V

6.MCH_CFG_19 DMI LANE Reversal: Low=Normal,High=LANES Reversed.

7.MCH_CFG_20 PCIE Backward interpoerability mode: Low= only

SDVO or PCIE x1 is operational (defaults) ,High=SDVO and

PCIE x1 are operation simultaneously via the PEG port.

Change to 4.02K 7/24

3. CFG[13:12] control the entry of the GMCH into different test modes

CFG[17:3] have internal pull-up

CFG[19:18] have internal pull-down

update per design guide v1.1

8/31

MCH_CFG_9

MCH_CFG_20

MCH_CFG_16

MCH_CFG_5

MCH_CFG_19

MCH_CFG_13

MCH_CFG_12

PM_EXTTS#1

PM_EXTTS#0

M_RCOMP

CLK_MCH_OE#

PM_BMBUSY#

MCH_CFG_9

M_ODT1

SM_RCOMP_VOL

DMI_RXN0

MCH_CFG_17

MCH_CFG_13

M_CS#2

M_CLK_DDR0#

DMI_TXP3

MCH_ICH_SYNC

CLK_MCH_OE#

CL_RST#0

DMI_RXP3

M_ODT2

M_CLK_DDR2#

M_A_A14

M_CLK_DDR3

DMI_TXP1

MCH_CFG_8

M_CKE3

M_CLK_DDR2

CL_VREF

DMI_TXP0

MCH_CFG_15

M_CLK_DDR3#

DMI_TXP2

MCH_CFG_12

MCH_CFG_4

M_ODT3

M_CS#3

SDVO_CTRL_DAT

DMI_RXP0

DMI_RXN3

DMI_TXN1

MCH_CFG_14

MCH_CFG_5

MCH_CFG_19

M_CKE0

DMI_RXP2

PWROK

MCH_CFG_6

MCH_CFG_3

DMI_RXP1

DMI_TXN0

DMI_TXN2

RST IN# MCH

MCH_CFG_11

M_CKE1

M_CLK_DDR1

SM_RCOMP_VOH

MCH_CFG_16

SMDDR_VREF_MCH

CL_DATA0

CL_CLK0

DMI_RXN1

MCH_CFG_18

M_ODT0

M_CKE2

DMI_RXN2

DMI_TXN3

MCH_CFG_7

M_CLK_DDR1#

M_CLK_DDR0

M_RCOMP#

PM_DPRSLPVR

MCH_CFG_10

PM_EXTTS#0

SM_RCOMP_VOH

SM_RCOMP_VOL

M_RCOMP

SDVO_CTRL_CLK

M_RCOMP#

MCH_CFG_20

LVDS_TXL3-

LVDS_TXL3+

M_CS#1

M_CS#0

DREFSSCLK#

DREFSSCLK

DREFCLK#

DREFCLK

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

MCH_BSEL2

MCH_BSEL0

MCH_BSEL1

M_B_A14

MCH_DPRSTP#

CPU_DPRSTP#

PM_THRMTRIP#

PM_EXTTS#1

MPWROK

LVDS_TXL3N

LVDS_TXL3P

SMDDR_VREF

+3V

+3V

+1.8VSUS

+1.25V

+1.8VSUS

+3V

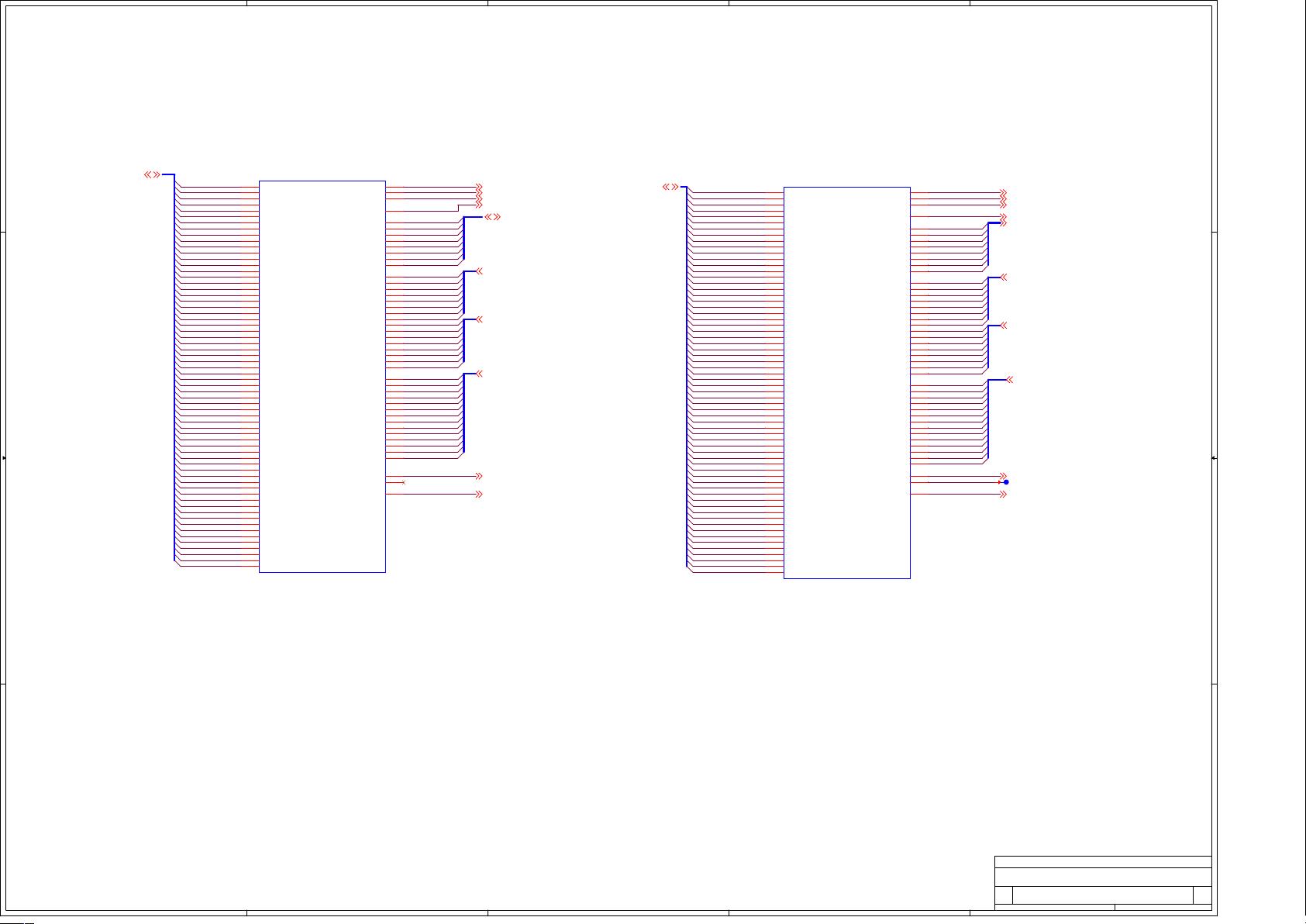

M_CS#2 37

M_CS#3 37

M_ODT2 37

M_ODT3 37

M_CKE3 37

M_CKE2 37

M_CLK_DDR2 38,39

M_CLK_DDR3 38,39

M_CLK_DDR2# 38,39

M_CLK_DDR3# 38,39

CL_RST#0 17

SDVO_CTRL_CLK 35

SDVO_CTRL_DAT 35

LVDS_TXL3+30

LVDS_TXL3-30

M_CLK_DDR1 14

M_CLK_DDR0 14

M_CLK_DDR1# 14

M_CLK_DDR0# 14

M_CKE0 14

M_CKE1 14

M_CS#0 14

M_CS#1 14

M_ODT0 14

M_ODT1 14

DMI_TXN[3:0] 16

DMI_TXP[3:0] 16

DMI_RXN[3:0] 16

DMI_RXP[3:0] 16

PM_BMBUSY#17

DREFSSCLK 4

DREFSSCLK# 4

DREFCLK 4

DREFCLK# 4

CLK_PCIE_3GPLL 4

CLK_PCIE_3GPLL# 4

MCH_BSEL04

MCH_BSEL14

MCH_BSEL24

M_B_A14

PWROK17,21,26,31

PLT_RST-R#16

CL_CLK0 17

CL_DATA0 17

PM_EXTTS#014

M_A_A1414

PM_DPRSLPVR17,31

MCH_ICH_SYNC 17

PM_THRMTRIP#5,15

MCH_DPRSTP#31

CPU_DPRSTP#5

PM_EXTTS#1

LVDS_TXL3P30

LVDS_TXL3N30

MPWROK 17,31

Title

Size

Document Number R e v

Date: Sheet o f

CPCI 965 0.1

09--GMCH DMI & STRAP (3 of 7)

C

9 41Saturday, September 12, 2009

Title

Size

Document Number R e v

Date: Sheet o f

CPCI 965 0.1

09--GMCH DMI & STRAP (3 of 7)

C

9 41Saturday, September 12, 2009

Title

Size

Document Number R e v

Date: Sheet o f

CPCI 965 0.1

09--GMCH DMI & STRAP (3 of 7)

C

9 41Saturday, September 12, 2009

T24

1

R83 0

T22

1

R79 0_4

R65

3K_6F

1 2

R71 *4.02K/F

1 2

R86 20K

R64

20

1 2

T25

1

R76 *4.02K/F

1 2

R80 0_4

C69

0.01U

T21

1

R72 10K

PM

MISC

NC

DDR MUXINGCLKDMI

CFGRSVD

GRAPHICS VIDME

U5B

CRESTLINE_1p0

SM_CK_0

AV29

SM_CK_1

BB23

RSVD28

BF23

SM_CK_3

BA25

SM_CK#_0

AW30

SM_CK#_1

BA23

RSVD29

BG23

SM_CK#_3

AW25

SM_CKE_0

BE29

SM_CKE_1

AY32

SM_CKE_3

BD39

SM_CKE_4

BG37

SM_CS#_0

BG20

SM_CS#_1

BK16

SM_CS#_2

BG16

SM_CS#_3

BE13

RSVD34

BH39

SM_ODT_0

BH18

SM_ODT_1

BJ15

SM_ODT_2

BJ14

SM_ODT_3

BE16

SM_RCOMP

BL15

SM_RCOMP#

BK14

SM_VREF_0

AR49

SM_VREF_1

AW4

CFG_18

L32

CFG_19

N33

CFG_2

N24

CFG_0

P27

CFG_1

N27

CFG_20

L35

CFG_3

C21

CFG_4

C23

CFG_5

F23

CFG_6

N23

CFG_7

G23

CFG_8

J20

CFG_9

C20

CFG_10

R24

CFG_11

L23

CFG_12

J23

CFG_13

E23

CFG_14

E20

CFG_15

K23

CFG_16

M20

CFG_17

M24

PM_BM_BUSY#

G41

PM_EXT_TS#_0

L36

PM_EXT_TS#_1

J36

PWROK

AW49

RSTIN#

AV20

DPLL_REF_CLK

B42

DPLL_REF_CLK#

C42

DPLL_REF_SSCLK

H48

DPLL_REF_SSCLK#

H47

DMI_RXN_0

AN47

DMI_RXN_1

AJ38

DMI_RXN_2

AN42

DMI_RXN_3

AN46

DMI_RXP_0

AM47

DMI_RXP_1

AJ39

DMI_RXP_2

AN41

DMI_RXP_3

AN45

DMI_TXN_0

AJ46

DMI_TXN_1

AJ41

DMI_TXN_2

AM40

DMI_TXN_3

AM44

DMI_TXP_0

AJ47

DMI_TXP_1

AJ42

DMI_TXP_2

AM39

DMI_TXP_3

AM43

RSVD10

AR37

RSVD12

AL36

RSVD11

AM36

RSVD13

AM37

RSVD22

BJ20

RSVD23

BK22

RSVD24

BF19

RSVD25

BH20

RSVD26

BK18

PM_DPRSTP#

L39

SM_CK_4

AV23

SM_CK#_4

AW23

RSVD30

BC23

RSVD31

BD24

RSVD35

AW20

RSVD36

BK20

RSVD5

AR12

RSVD6

AR13

RSVD7

AM12

RSVD8

AN13

RSVD1

P36

RSVD2

P37

RSVD3

R35

RSVD4

N35

GFX_VID_0

E35

GFX_VID_1

A39

GFX_VID_2

C38

GFX_VID_3

B39

GFX_VR_EN

E36

RSVD27

BJ18

SM_RCOMP_VOH

BK31

SM_RCOMP_VOL

BL31

THERMTRIP#

N20

DPRSLPVR

G36

RSVD9

J12

CL_CLK

AM49

CL_DATA

AK50

CL_PWROK

AT43

CL_RST#

AN49

CL_VREF

AM50

RSVD37

C48

RSVD38

D47

RSVD39

B44

RSVD40

C44

SA_MA14

BJ29

SB_MA14

BE24

RSVD21

B51

NC_1

BJ51

NC_2

BK51

NC_3

BK50

NC_4

BL50

NC_5

BL49

NC_6

BL3

NC_7

BL2

NC_8

BK1

NC_9

BJ1

NC_10

E1

NC_11

A5

NC_12

C51

NC_13

B50

NC_14

A50

NC_15

A49

SDVO_CTRL_CLK

H35

SDVO_CTRL_DATA

K36

CLK_REQ#

G39

RSVD14

D20

ICH_SYNC#

G40

RSVD20

H10

RSVD41

A35

RSVD42

B37

RSVD43

B36

RSVD44

B34

RSVD45

C34

PEG_CLK#

K45

PEG_CLK

K44

TEST_1

A37

NC_16

BK2

TEST_2

R32

T15

1

R77 *4.02K/F

1 2

R85 392_6F

1 2

T18

1

T23

1

R74 *4.02K/F

1 2

C66

2.2UF_4

R73 10K

R82 100

R67

1K

R69 *4.02K/F

1 2

C68

2.2UF_4

R66

20

1 2

T20

1

R75 10K

T16

1

R81 0_4

R84 1K

R68 0

R78 *4.02K/F

1 2

R63

1K

R70 4.02K_NA

1 2

T17

1

T19

1

C67

0.01U