MAX10 FPGA时钟与PLL配置指南

需积分: 50 43 浏览量

更新于2024-07-21

收藏 1.67MB PDF 举报

"MAX10时钟和用户PLL指南-cn"

MAX10 FPGA是Altera公司推出的一款可编程逻辑器件,其在时钟管理和 PLL(Phase-Locked Loop,相位锁定环路)方面具有独特的特点和设计。本指南详细介绍了MAX10 FPGA的时钟系统,包括时钟网络、内部振荡器和PLL的功能、架构以及设计考虑。

1. MAX10时钟和PLL概述:

- 时钟网络概述:这部分介绍FPGA中用于传输时钟信号的网络结构,确保时钟的稳定性和低延迟。

- 内部振荡器概述:内部振荡器是FPGA的基础时钟源,提供稳定的频率输入,支持系统时钟和各种内部操作。

- PLL概述:PLL用于频率合成,可以将输入的时钟信号倍频、分频或移相,以满足不同频率和时序需求。

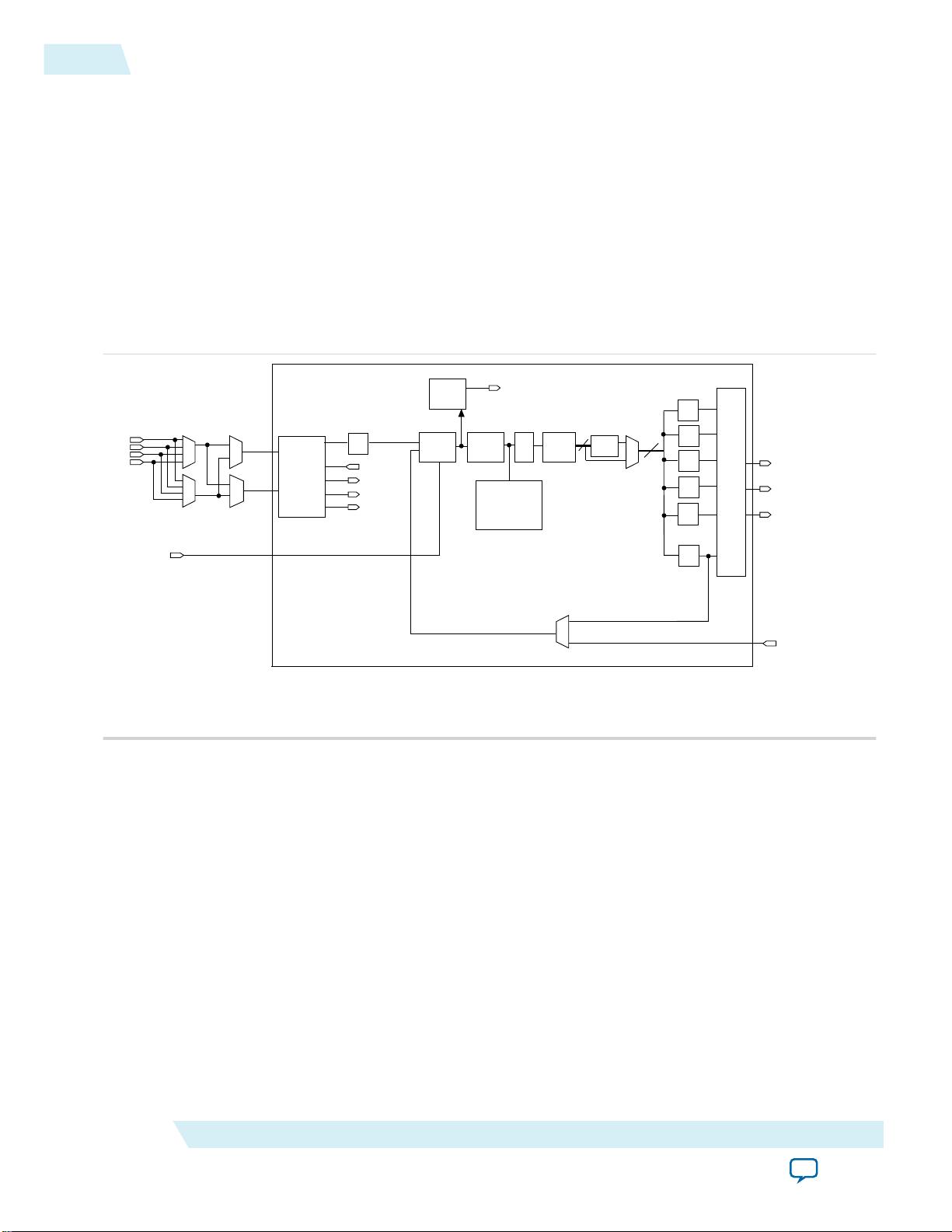

2. MAX10时钟和PLL体系结构及功能:

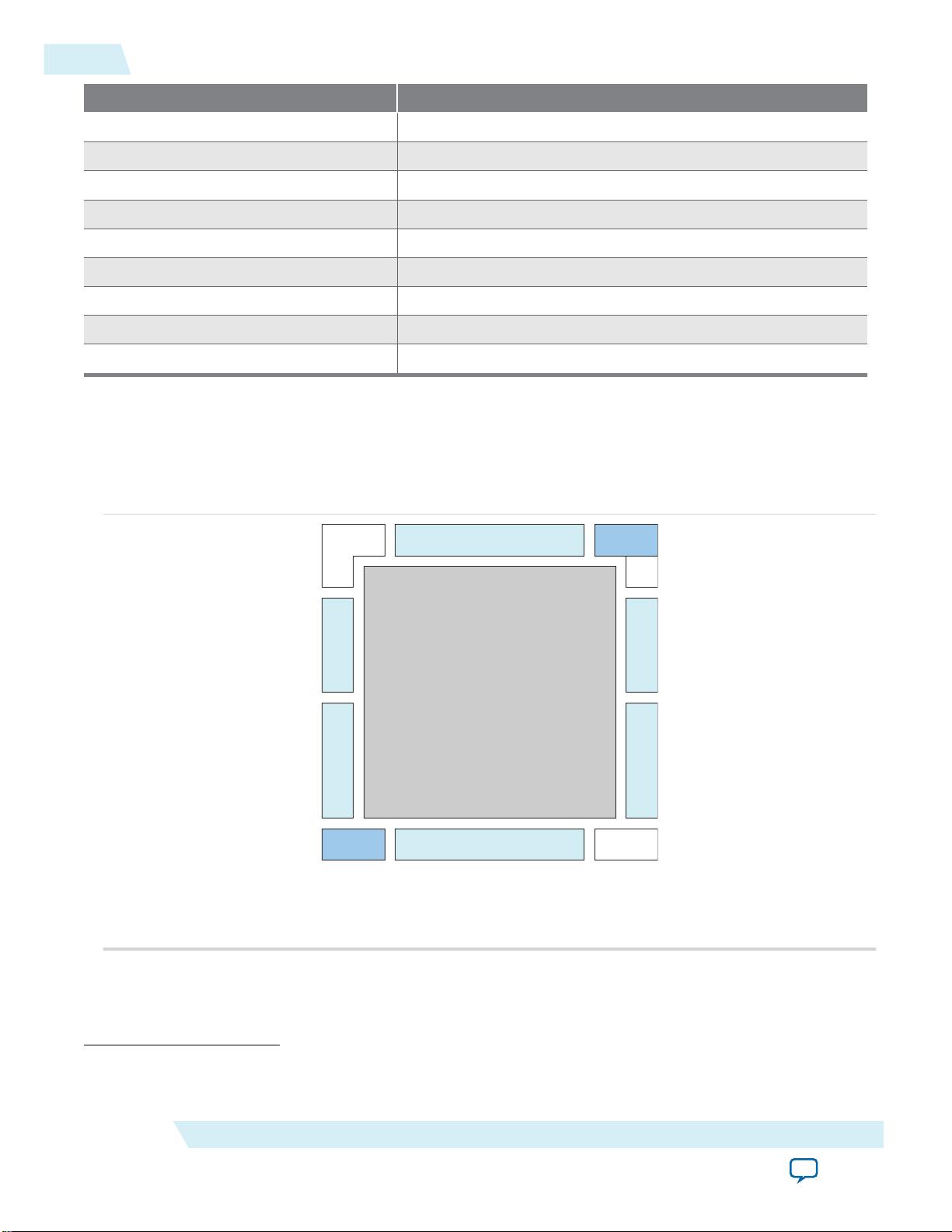

- 时钟网络体系结构和特性:包括全局时钟网络,它们提供低抖动、高精度的时钟信号,具有全局覆盖范围。

- 全局时钟网络:这些网络确保时钟信号在整个芯片上的同步。

- 时钟管脚介绍:讨论了输入和输出时钟引脚的配置和用法。

- 时钟资源:涵盖不同类型的时钟源、控制模块和电源管理功能。

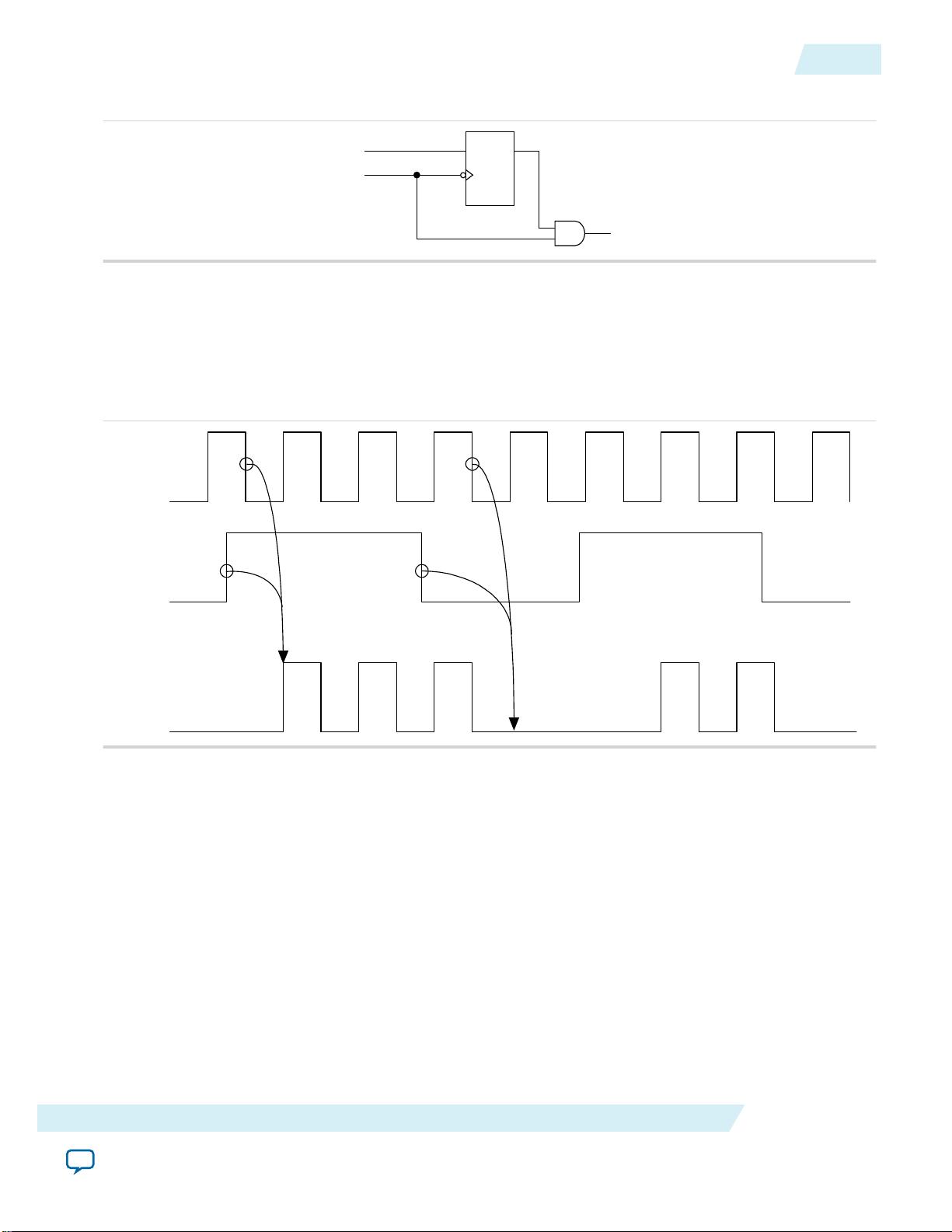

- PLL体系结构和特性:详细解析了PLL的内部结构,如分频器、倍频器、相位检测器等,并列出了其关键特性。

- PLL位置、时钟管脚连接、反馈模式等:说明如何将时钟信号路由到PLL,以及PLL如何生成输出时钟。

3. 设计考量:

- 时钟网络设计考量:提供了关于时钟分配、扇出和信号完整性方面的指导。

- 内部振荡器设计考量:讨论了使用内部振荡器的注意事项和限制。

- PLL设计考量:涵盖了PLL的控制信号选择、自复位、输出时钟设置以及级联和重配置的最佳实践。

4. 实现指南:

- ALTCLKCTRLIP内核:这是Altera提供的IP核,用于管理时钟资源,包括参数配置。

- ALTPLLIP内核:用于创建和配置PLL,支持多种时钟合成需求。

- ALTPLL_RECONFIGIP内核:用于在运行时重配置PLL,增加了设计的灵活性。

- 资源使用情况报告:设计完成后,可以通过这个工具检查时钟和PLL资源的利用率。

该指南是MAX10 FPGA开发者的重要参考资料,它提供了解决方案和设计建议,以优化时钟系统的性能和功耗,确保FPGA系统运行的高效和稳定。

142 浏览量

点击了解资源详情

点击了解资源详情

120 浏览量

213 浏览量

159 浏览量

2019-09-17 上传