FPGA实现的ARINC429总线接口设计与USB通信

96 浏览量

更新于2024-09-03

1

收藏 246KB PDF 举报

"本文主要介绍了基于EDA/PLD技术,使用FPGA实现ARINC429总线接口卡的设计,该设计替代了传统昂贵的专用接口芯片,通过ALTERA公司的FPGA芯片实现了与计算机USB接口的连接,提升了系统的灵活性和成本效益。"

在航空航天领域,ARINC429总线是广泛应用的通信协议,尤其在商用飞机如空中客车和波音系列飞机上。这种总线使用异步双极性归零码编码数据,通过双绞线传输,以增强抗干扰能力。传统的ARINC429接口设计通常依赖于如Device Engineering公司的DEI-1016或INTERSIL公司的HS-3282等专用接口芯片,但这些芯片不仅价格高昂,而且通道数量有限,限制了设计的灵活性。

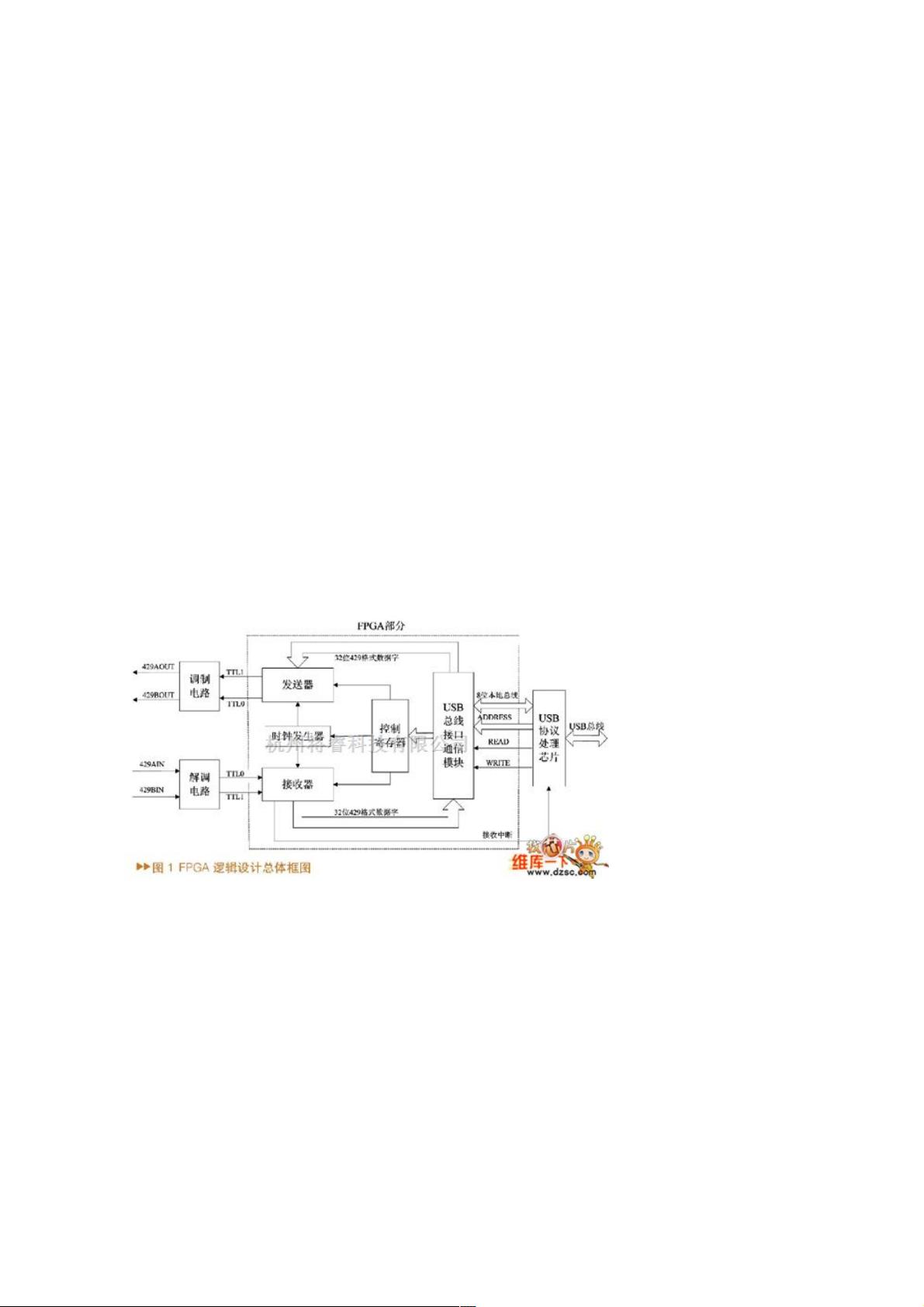

本文提出了一种创新设计,采用ALTERA公司的FPGA(现场可编程门阵列)来实现ARINC429标准数据传输。FPGA的优势在于其可编程性,允许根据需求定制逻辑功能,因此可以灵活地适应ARINC429协议的各种需求。同时,设计还整合了USB接口,使得FPGA能与计算机进行高效通信,进一步简化了系统架构,降低了硬件成本,并提高了系统的小型化程度。

ARINC429协议规定每个数据字由32位构成,包括标志位、源/目的标识码、数据区、符号/状态位以及奇偶校验位。数据以12.5kb/s或100kb/s的速率发送,使用双极性归零码,通过脉冲形式传输,确保了数据的可靠性和同步性。双极性归零码在每个脉冲间隔内提供时钟信息,增强了系统的同步能力。

在FPGA内部,设计需要实现的主要逻辑包括接收和发送模块,这两个模块需要处理数据的解码、编码、错误检测和校验功能。接收模块要能识别ARINC429的信号格式,解析出各个字段,并通过USB接口将数据传送到计算机。发送模块则需要将来自计算机的指令转换成符合ARINC429协议的数据格式,通过双绞线发送出去。

此外,FPGA设计还需要考虑错误处理和恢复机制,确保在数据传输过程中遇到错误时能够及时检测并采取相应的纠正措施。这通常包括对奇偶校验位的检查,以及在必要时重新发送数据。为了提高系统的可靠性,可能还需要实现流量控制和错误重试机制。

这个基于FPGA的ARINC429总线接口卡设计提供了一种成本效益高、灵活性强的解决方案,适用于航空电子设备的开发和测试。通过这种方式,开发者可以更加自由地配置接口功能,满足各种复杂的系统需求,同时降低整体系统的复杂性和成本。

2020-06-22 上传

2020-11-05 上传

2020-11-04 上传

2020-11-09 上传

2020-12-10 上传

2020-10-20 上传

2020-11-09 上传

点击了解资源详情

2020-12-13 上传

weixin_38716460

- 粉丝: 4

- 资源: 928

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍