高速PCB设计:串扰分析与抑制策略

170 浏览量

更新于2024-08-31

收藏 207KB PDF 举报

"高速PCB串扰分析及其最小化"

在高速PCB设计中,串扰是一个关键的问题,它直接影响到电子设备的性能和稳定性。随着技术的发展,电子产品的功能日益复杂,工作频率不断提高,PCB的密度增大,信号边沿速度加快,这使得串扰现象更为突出。如果不加以控制,串扰可能导致电路误触发,从而影响系统正常运行。

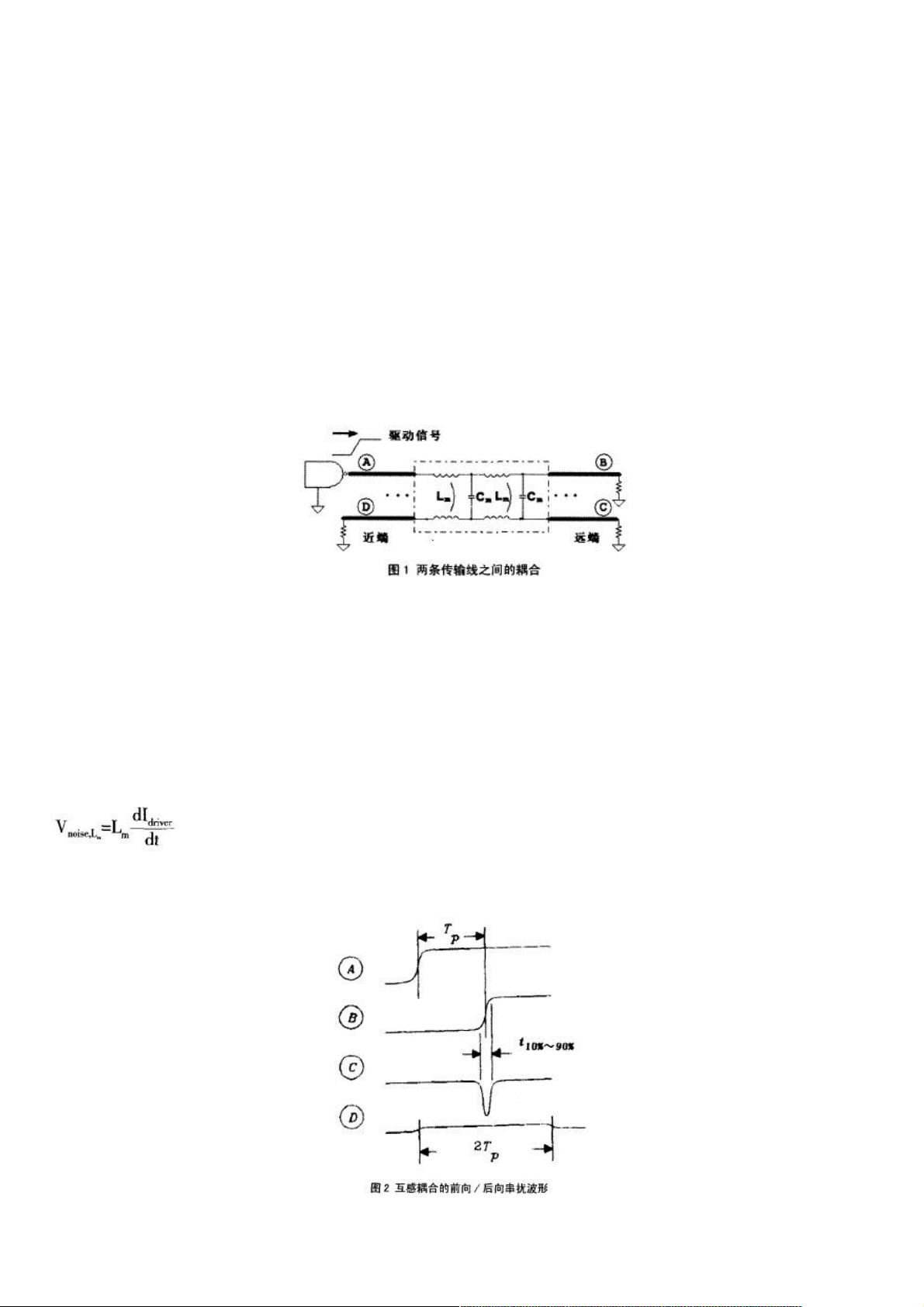

串扰的产生主要是由于相邻信号线之间的电磁场耦合。当一条线上的信号变化时,会通过互感(Lm)和互容(Cm)在相邻线路上产生不期望的噪声电压。这种噪声可以分为近端串扰和远端串扰。近端串扰发生在干扰源网络的驱动端附近,而远端串扰则发生在接收端附近。感性耦合是主要的耦合形式之一,如同分布式变压器,信号线上的磁场会在相邻线路上感应出电压尖脉冲。

计算互感耦合产生的噪声电压可以用以下公式表示,其中耦合的极性因位置不同而变化,导致干扰能量沿被干扰网络向前和向后传播,但极性相反。在图2中,前向干扰能量与输入电压和每个互感分量Lm成正比,所有的前向干扰能量在C点累积,而后向干扰能量则在D点积累。

为了最小化串扰的影响,设计师需要掌握串扰的机理,并采取有效的设计策略。这些策略包括但不限于:

1. **优化布线布局**:避免长距离的并行布线,减少信号线之间的耦合面积,使用地平面隔离或电源平面隔离来降低串扰。

2. **使用屏蔽层**:在PCB层间添加屏蔽层可以有效地抑制串扰,减少信号间的相互影响。

3. **正确选择信号线的间距**:间距的设定应根据信号的频率和幅度来确定,通常间距越宽,串扰越小,但也会占用更多的PCB空间。

4. **使用合适的阻抗匹配**:确保信号线的特性阻抗Z0与连接的负载阻抗匹配,可以减少反射,从而降低串扰。

5. **采用差分信号**:差分信号对由于其信号对内的互相抵消特性,可以显著降低串扰。

6. **利用模拟电路和数字电路的分区设计**:将模拟部分与数字部分分开,可以减少不同类型的信号间的干扰。

7. **使用适当的PCB材料**:选择低介电常数和低介电损耗的材料,可以减少信号的传播延迟和能量损失,从而降低串扰。

8. **仿真工具的应用**:借助于PCB设计软件进行仿真分析,预测和评估串扰程度,以便在设计阶段就找出并解决问题。

9. **调整信号的上升时间和下降时间**:减慢信号的上升和下降时间,可以降低边沿速率,从而降低串扰效应。

通过上述措施,设计者可以有效地管理和减轻高速PCB设计中的串扰问题,保证电子设备的性能和可靠性。在实际设计过程中,通常需要综合运用多种方法,根据具体设计需求和约束条件来进行权衡和优化。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-08 上传

2021-07-25 上传

2020-08-27 上传

2021-07-25 上传

2009-12-02 上传

2009-09-08 上传

weixin_38543120

- 粉丝: 6

- 资源: 932

最新资源

- How to Create a OneNote Toolbar Addin,怎样在onenote工具栏上添加按钮

- 移植到Symbian平台C-C.开放移动开发

- DOS批处理高级教程精选合编

- JAVA,CHM 3

- 云计算与网格计算360比较

- BO SERVER 连接BW SERVER

- Ubuntu、Windows XP、Windows Vista三系统启动引导教程.pdf

- 在MapX下读取属性值

- tomcat5.5.28支持EL 表达式的解决方法.

- 服务器运行命令(Windows server 2003)

- ActionScript3.0 Cookbook中文

- FlexUnit4熟悉与使用

- Dom4J生成XML的完整方法希望大家能用到

- WINFORM+ORACLE客户端打包教程

- delphi考试题目

- codewarrior快速入门