VHDL入门:硬件描述语言的关键要素与设计流程

需积分: 8 121 浏览量

更新于2024-07-22

收藏 1.53MB PPT 举报

"这篇资料主要介绍了VHDL语言的基础知识,包括其定义、功能、标准以及在硬件描述语言中的重要地位。"

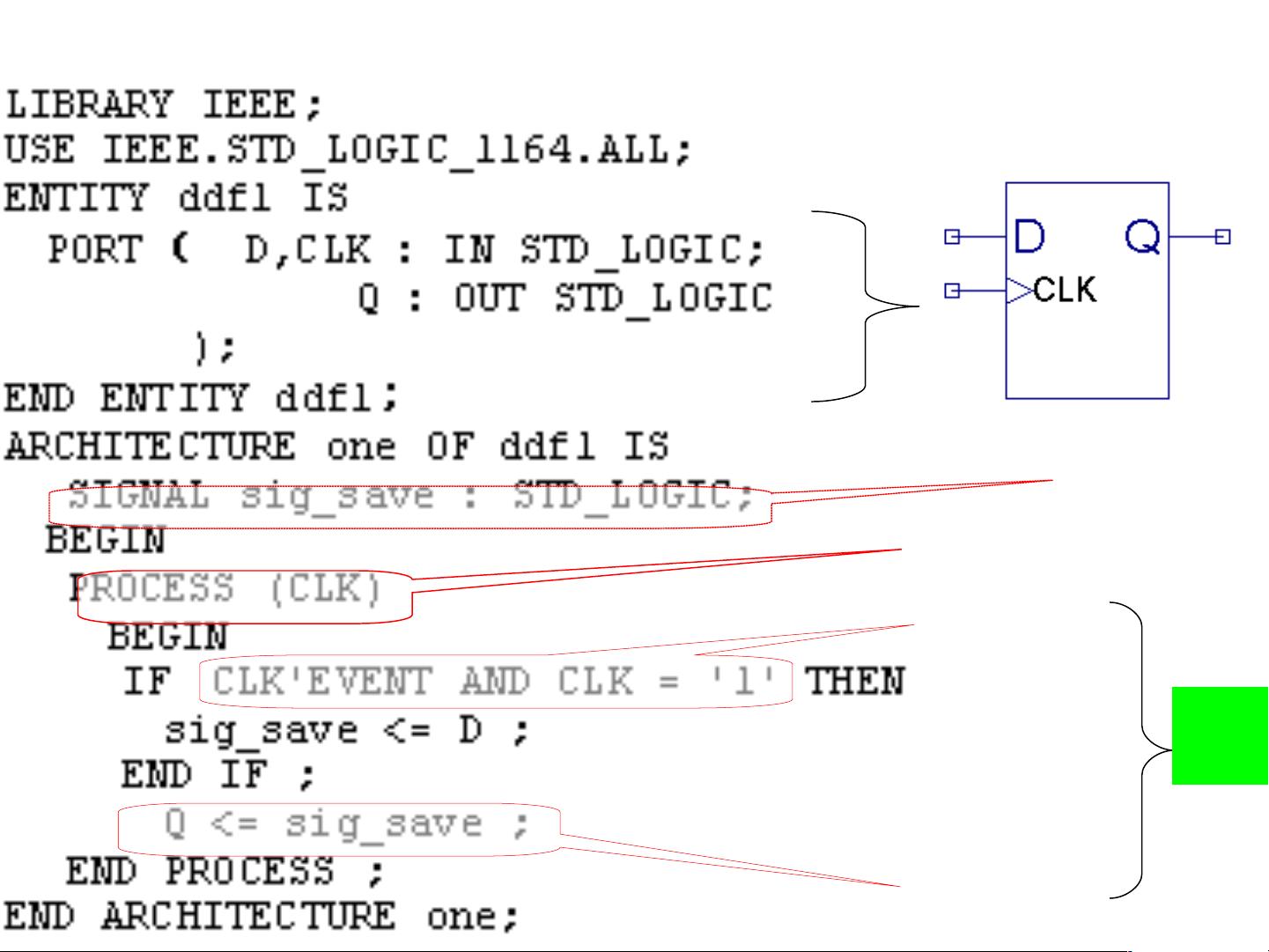

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种广泛使用的硬件描述语言,它由IEEE制定并成为行业标准,允许工程师以文本形式描述电子电路的行为和结构。与软件描述语言如C、PASCAL等不同,VHDL专门针对硬件设计,提供了更直观和灵活的方法来建模和验证数字系统。

在VHDL中,标识符是关键组成部分,用于命名常量、变量、信号、端口、子程序和参数等。这使得设计者能够清晰地组织和理解设计的各个部分。例如,可以使用VHDL来定义复杂的组合逻辑电路,如译码器、编码器、加减法器、多路选择器和地址译码器,以及状态机和其他数字系统。

VHDL有两个主要的IEEE标准:IEEE Std 1076-1987(VHDL-1987)和IEEE Std 1076-1993(VHDL-1993)。Altera公司的Max+Plus II工具支持这两个版本,并且只处理VHDL的可综合子集,这意味着不是所有的VHDL代码都可以直接转换为实际的硬件。

VHDL的设计流程通常包括以下步骤,即V-S-F-P:V(VHDL描述),S(仿真),F(功能验证),P(实现)。在这个过程中,首先用VHDL编写设计描述,然后通过仿真工具进行功能验证,确保设计符合预期。最后,经过综合和布局布线等步骤,将VHDL代码转化为物理电路。

EDA(Electronic Design Automation)工具在VHDL设计中扮演着重要角色,如Altera的Quartus、Lattice的ispEXPERT和Xilinx的Foundation等,它们为VHDL提供了一整套的开发环境,包括编译、仿真、综合和编程等。此外,还有许多其他知名的EDA公司如Cadence、Mentor Graphics、Synopsys等,它们提供的工具进一步丰富了VHDL的设计和实现。

VHDL作为一种强大的硬件描述语言,不仅方便了复杂电路设计的修改和保存,还促进了大规模和复杂数字系统的开发。通过学习和掌握VHDL,工程师能够更高效地设计和优化硬件电路,从而推动电子技术的进步。

2018-10-10 上传

2023-07-31 上传

2023-07-04 上传

2023-04-02 上传

2023-07-31 上传

2023-12-27 上传

2023-08-02 上传

cnoman

- 粉丝: 0

- 资源: 1

最新资源

- 社交媒体营销激励优化策略研究

- 终端信息查看工具:qt框架下的输出强制抓取

- MinGW Win32 C/C++ 开发环境压缩包快速入门指南

- STC8G1K08 PWM模块实现10K频率及易改占空比波形输出

- MSP432电机驱动编码器测路程方法解析

- 实现动静分离案例的css/js/img文件指南

- 爱心代码五种:高效编程的精选技巧

- MATLAB实现广义互相关时延估计GCC的多种加权方法

- Hive CDH Jar包下载:免费获取Hive JDBC驱动

- STC8G单片机实现EEPROM及MODBUS-RTU协议

- Java集合框架面试题精讲

- Unity游戏设计与开发资源全集

- 探索音乐盒.zip背后的神秘世界

- Matlab自相干算法GUI界面设计及仿真

- STM32智能小车PID算法实现资料

- Python爬虫实战:高效爬取百度贴吧信息