FPGA实现DDS信号发生器:高精度与多功能设计

"基于FPGA的DDS信号发生器设计,实现了频率可调的四种波形输出,包括高频率分辨率、高切换速度、相位连续、超宽频率范围以及多种波形产生等功能。采用DDS技术和FPGA,使得信号源具有良好的扩展性和成本效益。"

在电子工程领域,直接数字频率合成(DDS)是一种先进的信号生成技术,它通过数字方法生成连续的频率信号。基于FPGA(Field-Programmable Gate Array)的DDS信号发生器设计能够提供高度灵活和可配置的信号输出。

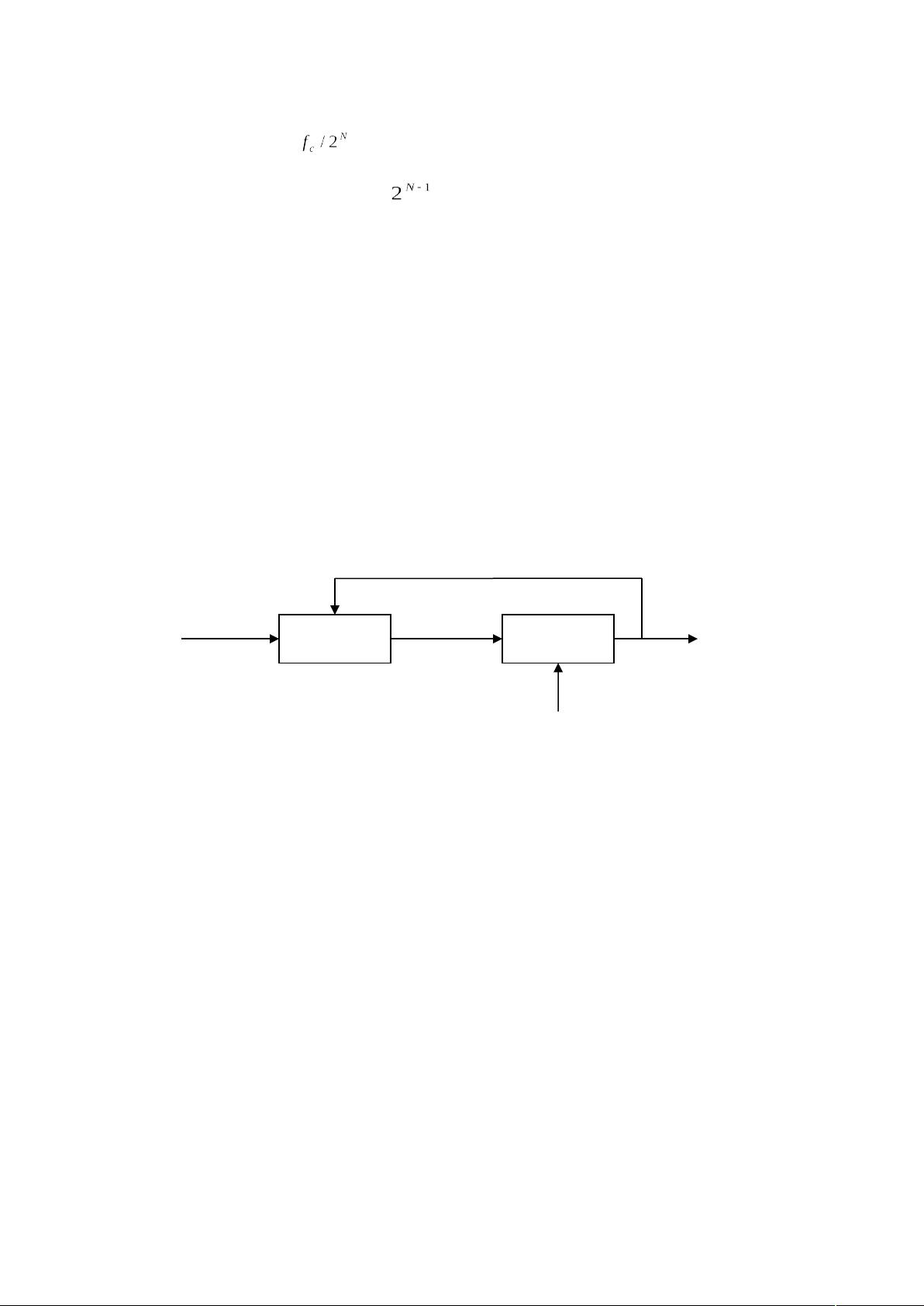

DDS的基本原理是利用高速数字逻辑来生成连续的频率变化。首先,通过频率预设和调节电路确定所需的输出频率。这个过程通常涉及到对参考时钟进行分频和倍频以获得所需频率。接着,累加器将一个初始相位值与一个频率控制字相加,每次时钟周期后相位值都会增加,形成一个不断变化的相位值。

控制相位加法器根据累加器的输出调整相位。波形存储器(通常是一个查找表)存储不同相位对应的幅度值,这些值与相位值对应。当相位变化时,波形存储器输出相应的幅度值,这些值经过D/A转换器转化为模拟信号。最后,低通滤波器用于平滑D/A转换后的信号,消除高频噪声,得到纯净的波形输出。

DDS的主要特点是频率分辨率高,意味着可以精确地设定输出频率;频率切换速度快,能在纳秒级别完成;相位连续性保证了在频率切换时没有突跳;超宽的频率范围覆盖了从几赫兹到几百兆赫兹;此外,DDS还能生成各种调制波形和任意形状的波形。

FPGA作为一种可编程逻辑器件,提供了设计DDS信号发生器的平台。利用FPGA的并行处理能力,可以快速实现DDS的各个部分,并且在不改变硬件的情况下,通过软件更新实现功能的扩展。这使得基于FPGA的DDS信号发生器具有很高的灵活性和成本效益。

设计过程中,通常会用到如Quartus II这样的FPGA开发工具进行硬件描述语言(如VHDL)编程,以及Matlab进行算法设计和仿真。在设计与仿真的阶段,会选择合适的方案,例如采用哪种DDS架构,如何分配FPGA的资源,以及如何进行顶层设计以整合所有组件。仿真结果的分析对于验证设计的正确性和性能至关重要。

总结来说,基于FPGA的DDS信号发生器是一个集高效、灵活和多功能于一身的信号生成解决方案,广泛应用于通信、测试测量、雷达系统等多个领域。其设计和实现充分体现了数字信号处理的优势,为现代电子系统提供了强大的信号源支持。

2018-09-24 上传

2012-07-07 上传

2024-02-24 上传

2023-02-15 上传

2023-05-14 上传

2023-05-20 上传

2023-05-12 上传

2024-05-16 上传

Tenyears

- 粉丝: 5

- 资源: 2

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析