多功能数字钟设计与FPGA实验开发——时分秒计数器设计思路总结

需积分: 0 70 浏览量

更新于2024-03-25

1

收藏 992KB PDF 举报

多功能数码时钟设计过程中,首先需要设计时分秒计数器。时分秒计数器都是模 M=60 的计数器,时计数器为一个 24 进制计数器。当数字钟运行到 23 时 59 分 59 秒时,秒的个位计数器再输入一个秒脉冲,数字钟应自动显示为 00 时 00 分 00 秒。整个数字钟的设计框图将整个数字钟设计分为几个模块,包括时钟分频模块、计时校时模块和 7 段数码管动态显示模块。

时钟分频模块的设计是通过对 B8 管脚对应的板载 50MHz 晶振进行分频,从而得到所需脉冲信号。首先,需要对晶振进行分频,然后通过相应的逻辑门电路进行处理,得到分频后的脉冲信号,用于时分秒计数器的计数。时钟分频模块的设计是数字钟设计中必不可少的一部分,为数字钟的精准计时提供了稳定的时钟信号。

计时校时模块用于对数字钟进行计时和校时操作。在数字钟运行过程中,需要实现时分秒的计数和显示,同时还需要实现校时功能,确保数字钟的时间准确无误。计时校时模块通过对时钟信号进行计数和控制,实现对数字钟时间的准确记录和显示,同时可以通过外部输入信号进行校时操作,确保数字钟时间的准确性。

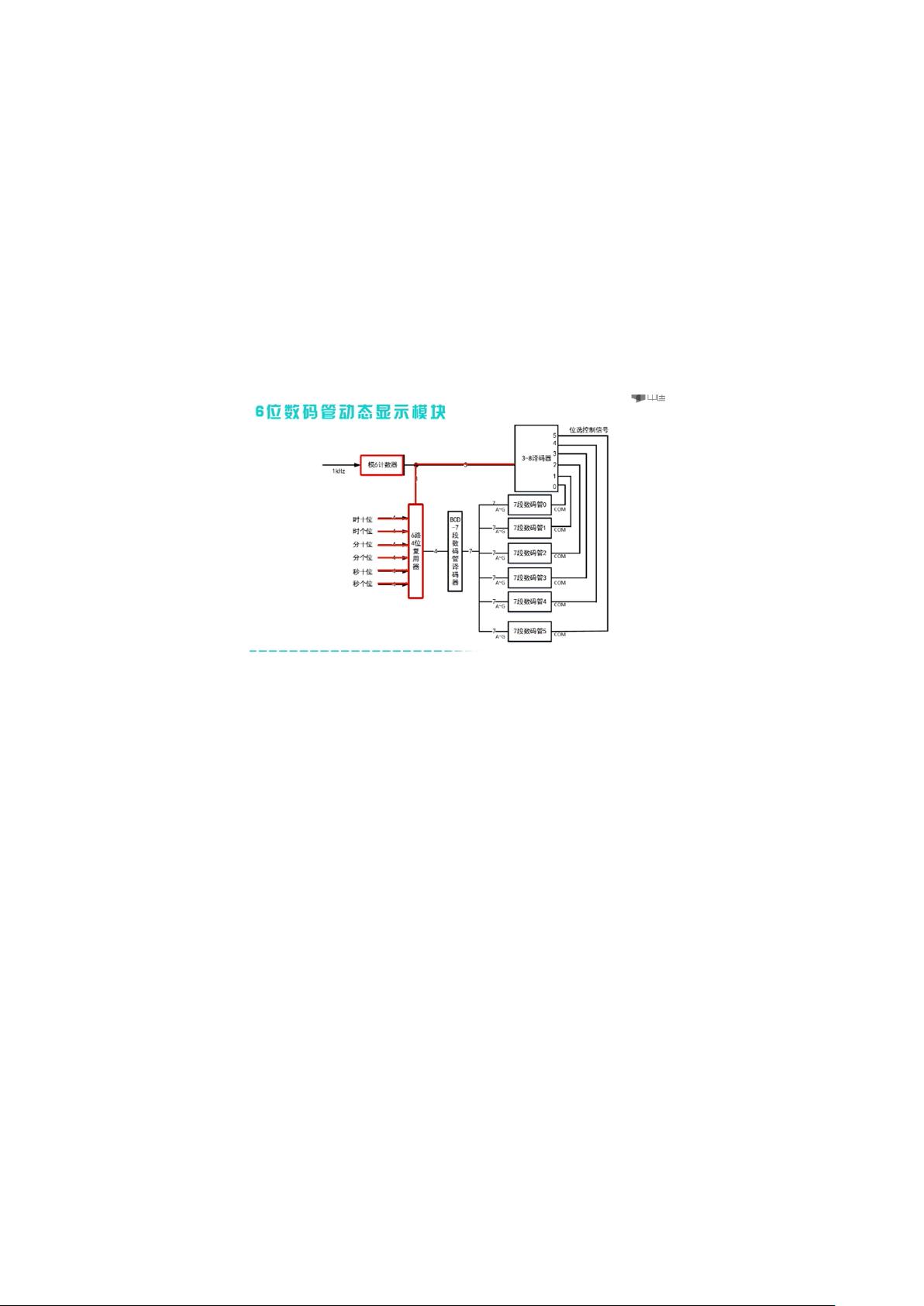

7 段数码管动态显示模块用于将时分秒计数器的结果以动态的方式显示在数码管上。通过适当的逻辑设计和控制,将计时器的计数结果以时分秒的形式显示在 7 段数码管上,实现数字钟时间的直观显示。动态显示模块还可以实现亮度调节和闪烁效果,增强数字钟的视觉效果和实用性。

在多功能数字钟设计中,除了基本的时分秒计数和显示功能外,还可以根据需要添加其他功能模块,如闹钟功能、温湿度显示等。通过对数字钟的模块化设计和功能扩展,可以实现更多实用功能,提高数字钟的实用性和功能性。华中科技大学人工智能与自动化学院的多功能数字钟设计实验,通过对 FPGA 实验开发装置的应用,掌握可编程逻辑器件的开发技术,熟悉 EDA 软件的使用,掌握 Verilog HDL 设计方法,从而实现多功能数字钟的设计和开发。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-03-30 上传

2024-06-26 上传

2011-05-30 上传

2010-05-05 上传

2010-05-28 上传

2010-05-25 上传

白羊的羊

- 粉丝: 45

- 资源: 280

最新资源

- 音乐播放次数最多的谱图还原:音乐播放次数最多

- Cpp_Project_1:C ++ Udacity课程的第一个项目

- eclipse-cpp-mars-R-linux-gtk-x86_64.tar.gz

- react-design-furnitures:我的第一个应用程序

- Titanic_Dataset_PurePython

- AndroidStudio_Projects

- opencv-demo-webapp-snap:一个简单的 OpenCV webapp 示例

- ACCESS网上聊天室ASP毕业设计(源代码+论文+开题报告+任务书+答辩PPT).zip

- Accuinsight-1.0.33-py2.py3-none-any.whl.zip

- Auth0-Regular-Web-App-Test

- WebFamily:Beetlex Web SPA应用组件

- 费利斯cumplea-os

- MainPartExtractor:获取句子的主谓宾

- tornado_circus_heroku:使用Circus在一个Heroku dyno上管理一堆Tornado应用程序进程

- 模拟量的转换程序1.rar

- test-deploy-actions