AD652

REV. B

–4–

ORDERING GUIDE

Gain

Drift Specified

Part ppm/ⴗC 1 MHz Temperature Package

Number

1

100 kHz Linearity % Range ⴗC Options

2

AD652JP 50 max 0.02 max 0 to +70 PLCC (P-20A)

AD652KP 25 max 0.005 max 0 to +70 PLCC (P-20A)

AD652AQ 50 max 0.02 max –40 to +85 Cerdip (Q-16)

AD652BQ 25 max 0.005 max –40 to +85 Cerdip (Q-16)

AD652SQ 50 max 0.02 max –55 to +125 Cerdip (Q-16)

NOTES

1

For details on grade and package offerings screened in accordance with MIL-

STD-883, refer to the Analog Devices Military Products Databook or current

AD652/883 data sheet.

2

P = Plastic Leaded Chip Carrier; Q = Cerdip.

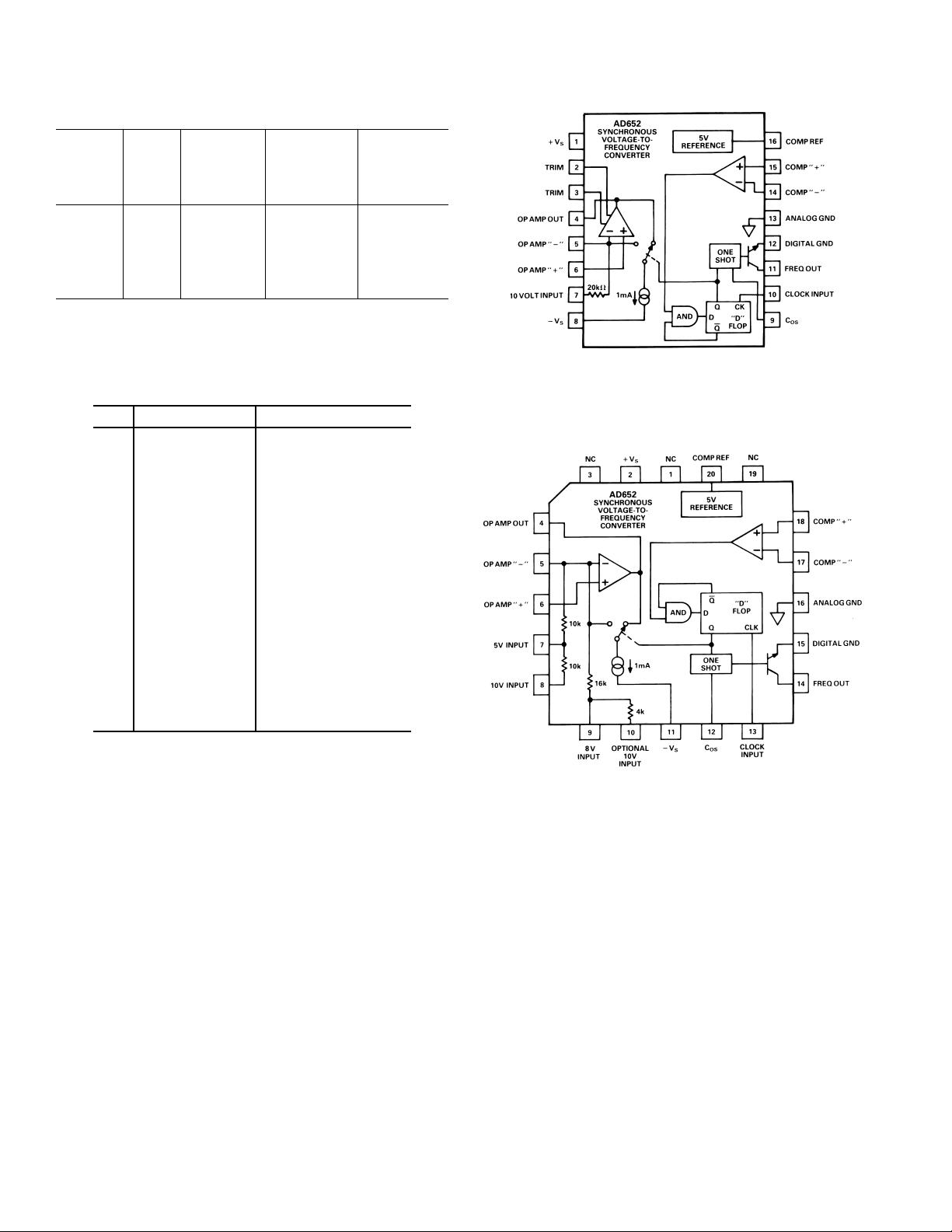

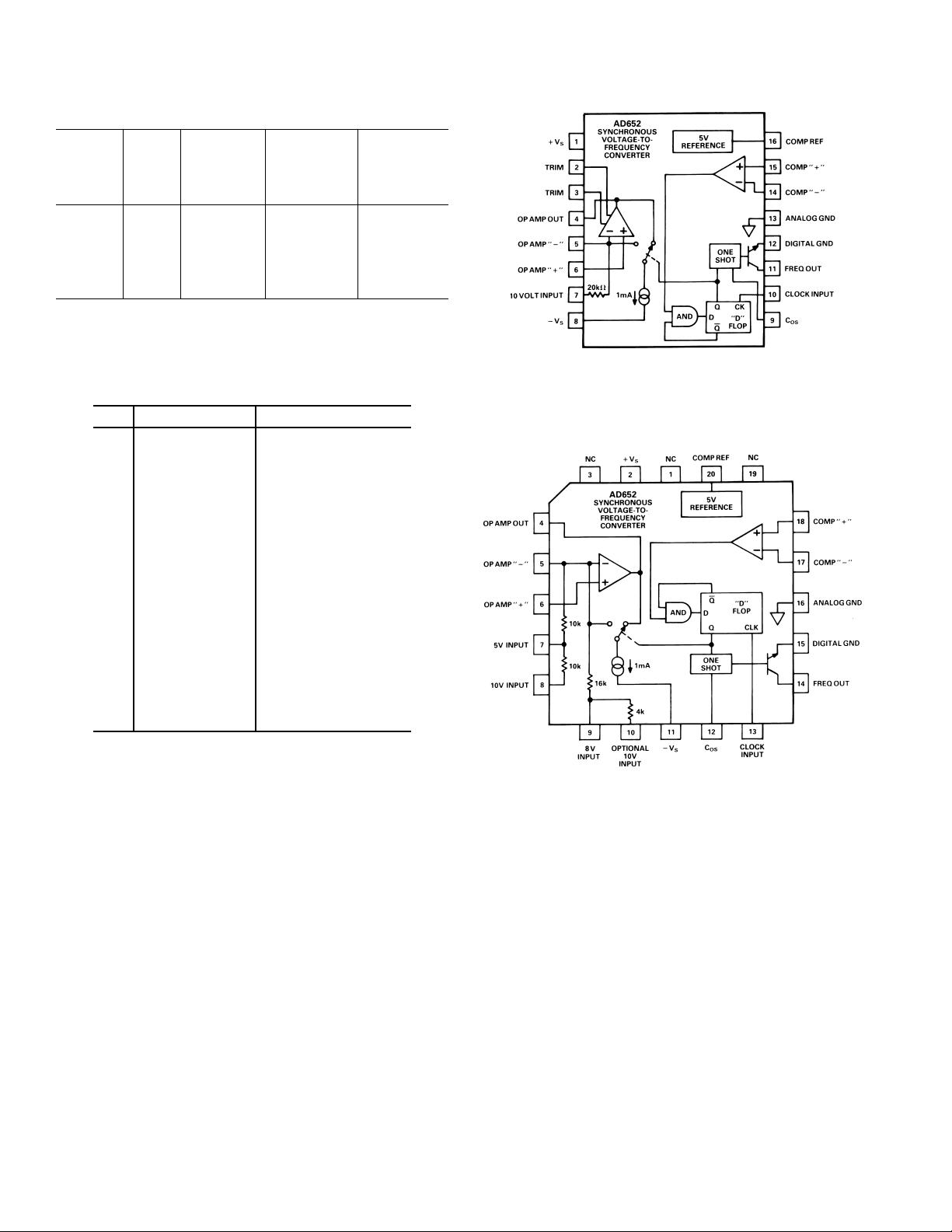

PIN CONFIGURATIONS

PIN Q-16 PACKAGE P-20A PACKAGE

1+V

S

NC

2 TRIM +V

S

3 TRIM NC

4 OP AMP OUT OP AMP OUT

5 OP AMP “—” OP AMP “—”

6 OP AMP “+” OP AMP “+”

7 10 VOLT INPUT 5 VOLT INPUT

8–V

S

10 VOLT INPUT

9C

OS

8 VOLT INPUT

10 CLOCK INPUT OPTIONAL 10 V INPUT

11 FREQ OUT –V

S

12 DIGITAL GND C

OS

13 ANALOG GND CLOCK INPUT

14 COMP “—” FREQ OUT

15 COMP “+“ DIGITAL GROUND

16 COMP REF ANALOG GND

17 COMP “—”

18 COMP “+”

19 NC

20 COMP REF

THEORY OF OPERATION

A synchronous VFC is similar to other voltage-to-frequency

converters in that an integrator is used to perform a charge-

balance of the input signal with an internal reference current.

However, rather than using a one-shot as the primary timing

element which requires a high quality and low drift capacitor,

a synchronous voltage-to-frequency converter (SVFC) uses an

external clock; this allows the designer to determine the system

stability and drift based upon the external clock selected. A crys-

tal oscillator may also be used if desired.

The SVFC architecture provides other system advantages besides

low drift. If the output frequency is measured by counting

pulses gated to a signal which is derived from the clock, the

clock stability is unimportant and the device simply performs as a

voltage controlled frequency divider, producing a high resolution

A/D. If a large number of inputs must be monitored simulta-

neously in a system, the controlled timing relationship between

the frequency output pulses and the user supplied clock greatly

simplifies this signal acquisition. Also, if the clock signal is pro-

vided by a VFC, then the output frequency of the SVFC will be

proportional to the product of the two input voltages.

Hence, multiplication and A-to-D conversion on two signals are

performed simultaneously.

Figure 1a. Cerdip Pin Configuration

The pinouts of the AD652 SVFC are shown in Figure 1. A

block diagram of the device configured as a SVFC, along with

various system waveforms, is shown in Figure 2.

Figure 1b. PLCC Pin Configuration

Figure 2 shows the typical up-and-down ramp integrator output

of a charge-balance VFC. After the integrator output has crossed

the comparator threshold and the output of the AND gate has

gone high, nothing happens until a negative edge of the clock

comes along to transfer the information to the output of the

D-FLOP. At this point, the clock level is low, so the latch does

not change state. When the clock returns high, the latch output

goes high and drives the switch to reset the integrator. At the

same time the latch drives the AND gate to a low output state.

On the very next negative edge of the clock the low output state

of the AND gate is transferred to the output of the D-FLOP

and then when the clock returns high, the latch output goes low

and drives the switch back into the Integrate Mode. At the same

time the latch drives the AND gate to a mode where it will truth-

fully relay the information presented to it by the comparator.

Since the reset pulses applied to the integrator are exactly one

clock period long, the only place where drift can occur is in a

variation of the symmetry of the switching speed with tempera-

ture. Since each reset pulse is identical to every other, the AD652

SVFC produces a very linear voltage to frequency transfer rela-

tion. Also, since all of the reset pulses are gated by the clock,