FPGA实现的同步与异步计数器详解及设计

需积分: 10 101 浏览量

更新于2024-11-10

收藏 264KB DOC 举报

计数器的FPGA实现是数字电子系统设计中的基础模块,它在许多应用领域如通信、计算机硬件、嵌入式系统等中发挥着关键作用。FPGA(Field-Programmable Gate Array)作为可编程逻辑器件,提供了灵活的硬件实现平台,使得计数器设计更为高效和定制化。

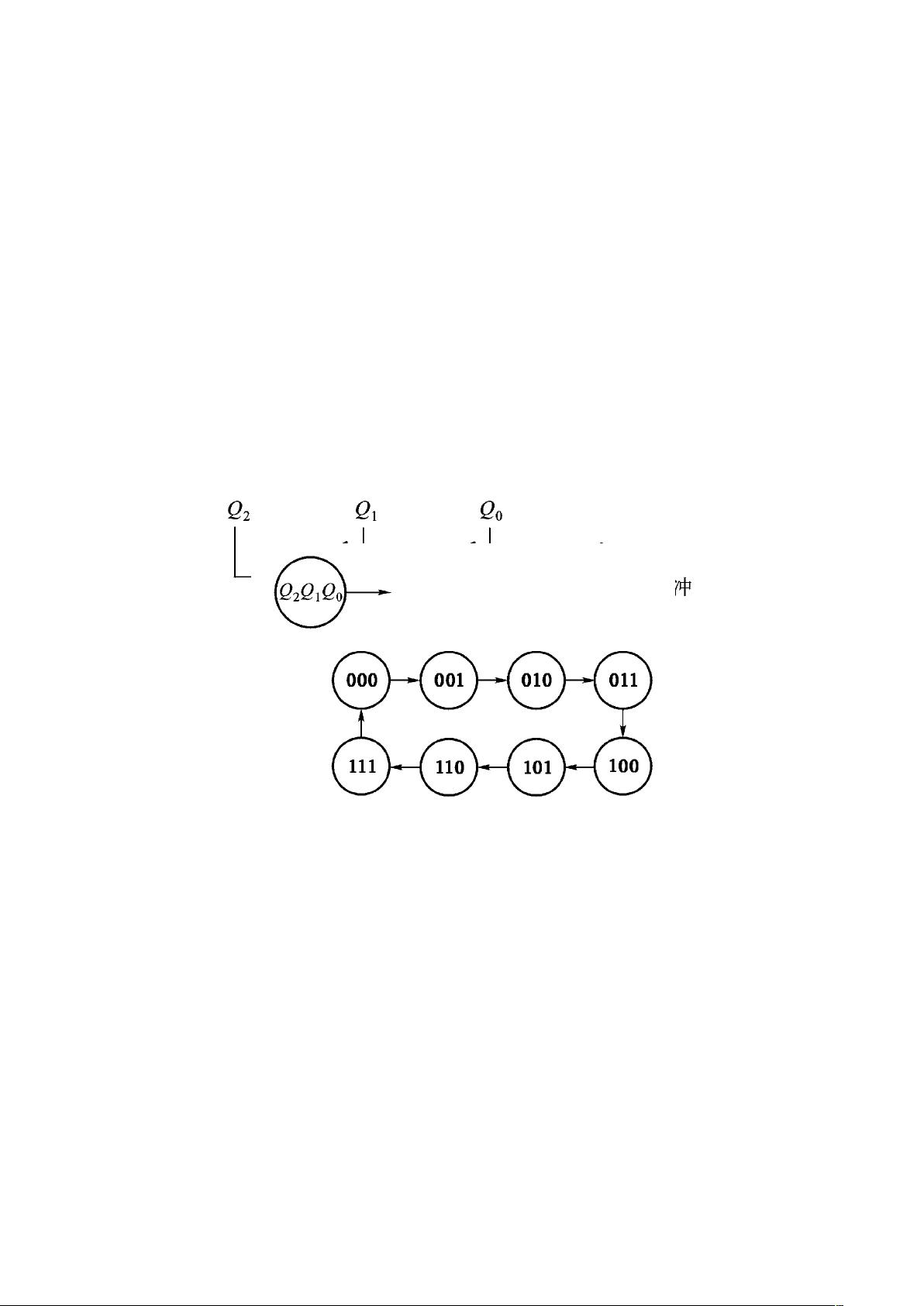

首先,计数器根据工作原理主要分为同步计数器和异步计数器。同步计数器的特点是在同一个时钟周期内,所有触发器的状态更新同步进行,适合对速度有较高要求的场景。例如,同步4位二进制加法计数器通过T触发器设计,其状态转换遵循特定规则,如最低位每来一个时钟脉冲翻转一次,高位随低位变化相应翻转。而异步计数器则不受全局时钟控制,每个触发器根据自身输入独立计数,虽然速度较慢,但结构相对简单。

同步二进制计数器包括加法、减法等类型,如图1所示的4位同步加法计数器,其状态转换过程在时序图图3中清晰展现。同步十进制计数器如图4所示,同样可以通过一般时序逻辑设计或利用T触发器设计,它们通常采用BCD编码以准确表示十进制数。

FPGA实现的计数器不仅限于二进制和十进制,还可以扩展到任意进制,这得益于其灵活性。在FPGA中,可以配置不同的逻辑门组合来实现不同进制的计数功能。此外,FPGA还支持用户自定义计数模式,如可逆计数器,这种计数器不仅能增加,还能减少计数状态,为设计者提供了更大的灵活性。

设计时,FPGA计数器的设计流程可能包括确定计数器类型、选择合适的触发器、构建状态机模型、编写VHDL或Verilog等硬件描述语言代码,并通过FPGA开发工具进行综合、布局布线和下载至目标板进行验证。FPGA计数器的实现可以显著提高系统的性能和效率,尤其是在需要大量计数或者对速度和精度要求高的应用场景。

FPGA技术为计数器设计提供了强大的平台,能够满足各种复杂度和实时性的需求,是现代电子系统设计中的重要组成部分。学习和掌握FPGA上的计数器实现,对于电子工程师来说是一项必不可少的技能。

2022-04-22 上传

2020-06-04 上传

点击了解资源详情

2010-05-15 上传

2022-03-27 上传

2011-04-07 上传

2021-08-23 上传

2021-08-23 上传

windhood911

- 粉丝: 3

- 资源: 8