A body-biasing of readout circuit for STT-RAM

with improved thermal reliability

Lun Yang

, Yuanqing Cheng

y

, Yuhao Wang

z

, Hao Yu

z

, Weisheng Zhao

yx

and Aida Todri-Sanial

{

School of Mathmatics and System Science

y

School of Electrical and Information Engineering Beihang University, Beijing, China 100191

y

School of Electrical and Elec tronic Engineering Nanyang Techn ological University, Singap ore, 639798

z

IEF, U niv. Paris-Sud 1 1, F-91405 Orsay, France

x

LIRMM CNRS/Universit´e d e Montpellier 2, Montpellier,France

Email: yuanqing@ieee.org

Abstract—As the integration density rockets up for contem-

porary VLSI circuits, power consumption li mits the scalability

of technology advancement of CMOS. Spin transfer torque-

magnetic random access memory (STT-MRAM), as one of the

emerging non-CMOS technologies, has the promising prospect of

low standby power, fast access speed and compatibili ty with the

CMOS fabrication process. However, with the technology node s-

caling down, typical 1 Transistor-1 Magnetic Tunnel Junction (1T-

1MTJ) STT-RAM cell suffers from severe reliability challenges,

especially for read op eration under temperature fluctuation. In

this paper, we quant itatively analyze the temperature effect on

read reliability of STT-RAM cell and propose a novel body-

biasing feedback readout circuit design to improve the read

sensing margin under different temperatures. The experiments

based on 40nm CMOS technology and MTJ compact model

validate the eff ectiveness of the proposed method. The improved

sensing margin also permits a smaller sensing current for reading

such that higher read energy efficiency can be achieved.

I. INTRODUCTION

Due to the endless pursuit for high performance computing,

multi-core or many core system comes into play to exploit

parallelism furthe r. However, this design paradigm shifting

also in troduces well-known “dark silicon” effect and elevated

leakage power, especially for memory systems.

Several emerging memory techn ologies, including STT-

MRAM, Phase charge random access memory (PCRAM),

memristor, etc., are proposed to mitiga te the elevating p ower

crisis. Among them, STT-MRAM is o ne of the most promising

candidates to replace SRAM or DRAM thanks to its fast access

speed, extremely low standby power and high integratio n den-

sity. Its promising prospect has already attracted many research

efforts on exploring STT-MRAM pote ntials from device level

to architecture level [1]–[5]. Mo st of the m f ocus on write

energy efficiency and write reliability issues. However, as the

technolo gy node con tinuously scales down, read current has

to be smaller in order to refrain read disturba nces. This makes

the read sensing reliability a severe challenge for STT-RAM

when the feature size shr inks below 50nm [6]. More over, STT-

RAM has to mee t the wide working temperature requirement

ranging from room temperature to 125°C for commercial use.

Therefore, it is also imperative to investigate the tempera ture

impact on STT-RAM access behavior to make sure reliable

data sensing over the whole temperature range. However,

Si/SiO

2

T

a

Ta

Ru

Al

2

O

3

Al

2

O

3

CoFeB

CoFeB

MgO

Ta

Ru

Cr/Au

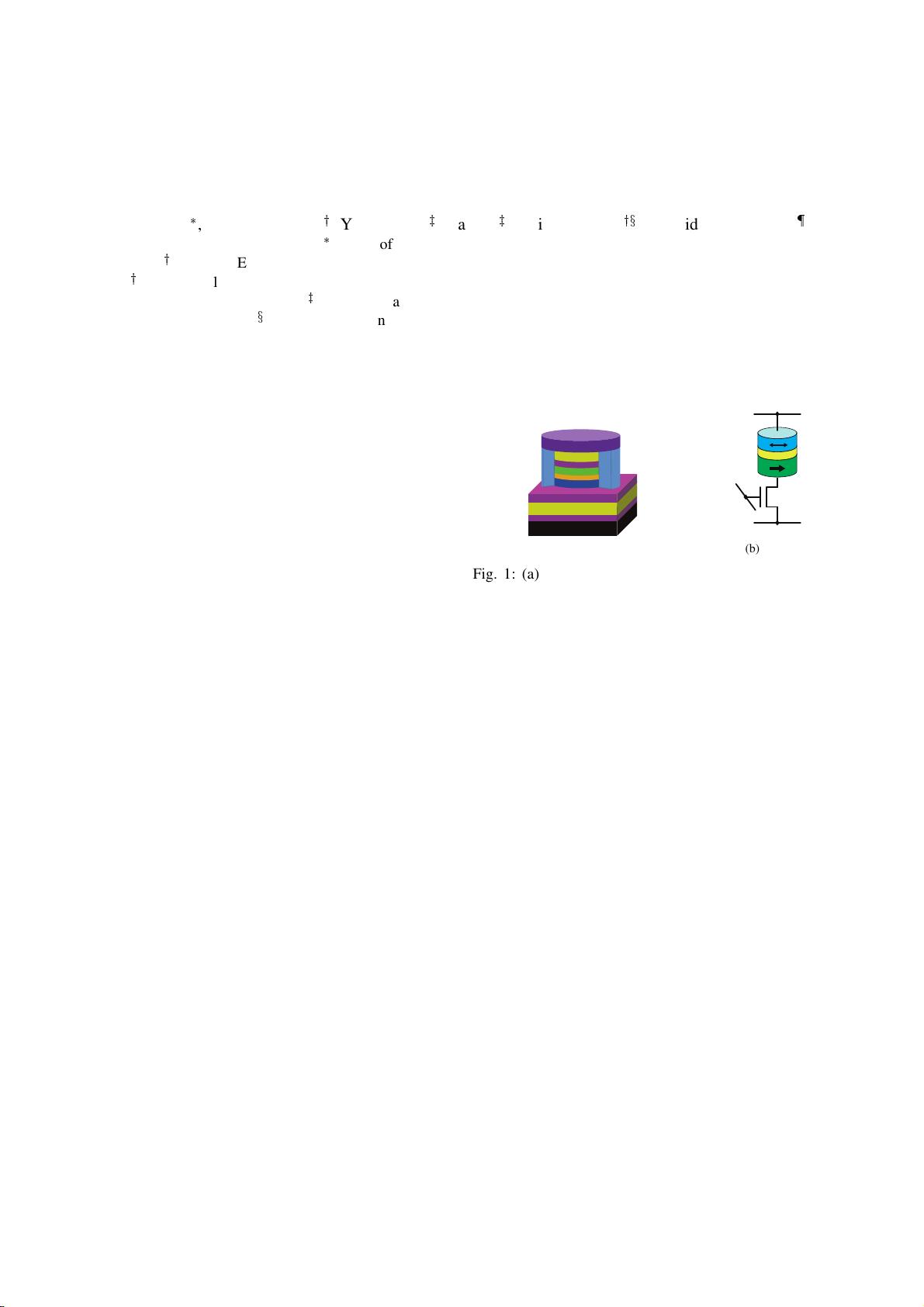

(a)

Free layer

Ba

rrier layer

Reference layer

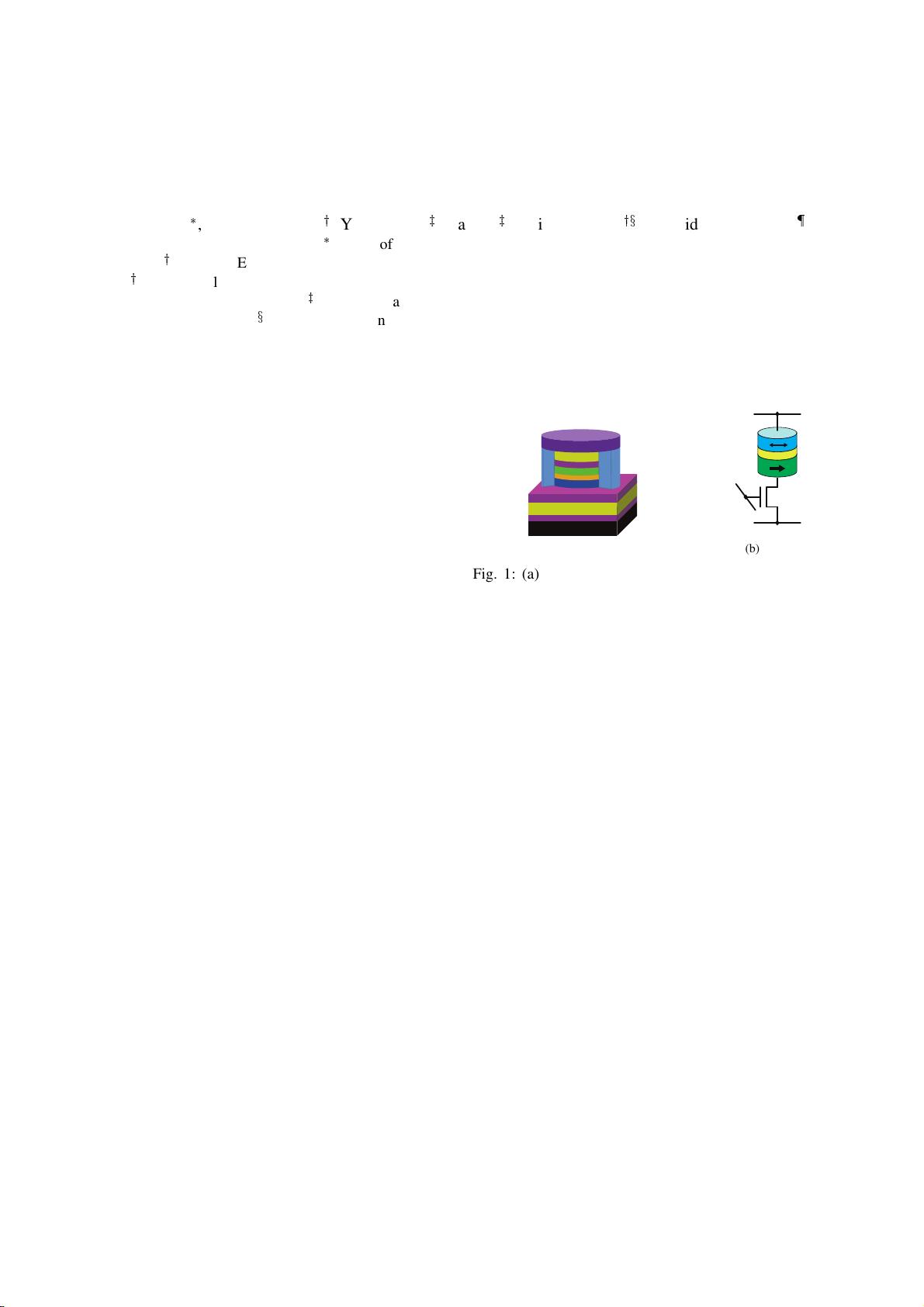

BL

WL

SL

Bit“0”

Bit“1”

(b)

F

ig. 1: (a) Th e structure of MTJ (b) A typical schematic of

1T-1MTJ STT-RAM cell

few research papers investigate this point, especially from the

circuit design perspective, which motivates the work in this

paper.

In the paper, we first ana lyze megneto-resistive tunnel junc-

tion (MTJ) and tr ansistor behavior for different temperatures.

Then, we evaluate the thermal impact on the typical sen sin g

circuit of 1T-1MTJ cell. Based on the ab ove an alyses, we

propose a novel body-biasing sensing circuit design to improve

the read sensing ma rgin conside ring the temperature variation.

The experimental results show that the sensing reliability can

be enha nced co mpared to the typical read circuit. Moreover,

the sensing energy efficiency can be improved significantly

under the same sensing margin.

The rest of the paper is organized as f ollows. T he prelim-

inaries of STT-RAM ac cess mechanism and related work are

introdu ced in Section II. Section III analyzes the variations of

MTJ and access tra nsistor caused by temperature. After that,

the temperature effect on read sensing margin of a typical

sensing circuit is evaluated in the same section. Based on

above analyses, a novel body-biasing feedback technique is

proposed to improve the r ead sensing ma rgin in Section IV.

Experimental results are shown in Section V. Finally, Section

VI c oncludes the paper.

II. PRELIMINARIES AND RELATED WORK

MTJ is the core of STT-RAM cell. It mainly consists of

an oxide insulating layer (e.g., MgO) sandwiched by two

978-1-4799-8391-9/15/$31.00 ©2015 IEEE 1530