7

CDCE913

,

CDCEL913

www.ti.com

SCAS849G –JUNE 2007–REVISED OCTOBER 2016

Product Folder Links: CDCE913 CDCEL913

Submit Documentation FeedbackCopyright © 2007–2016, Texas Instruments Incorporated

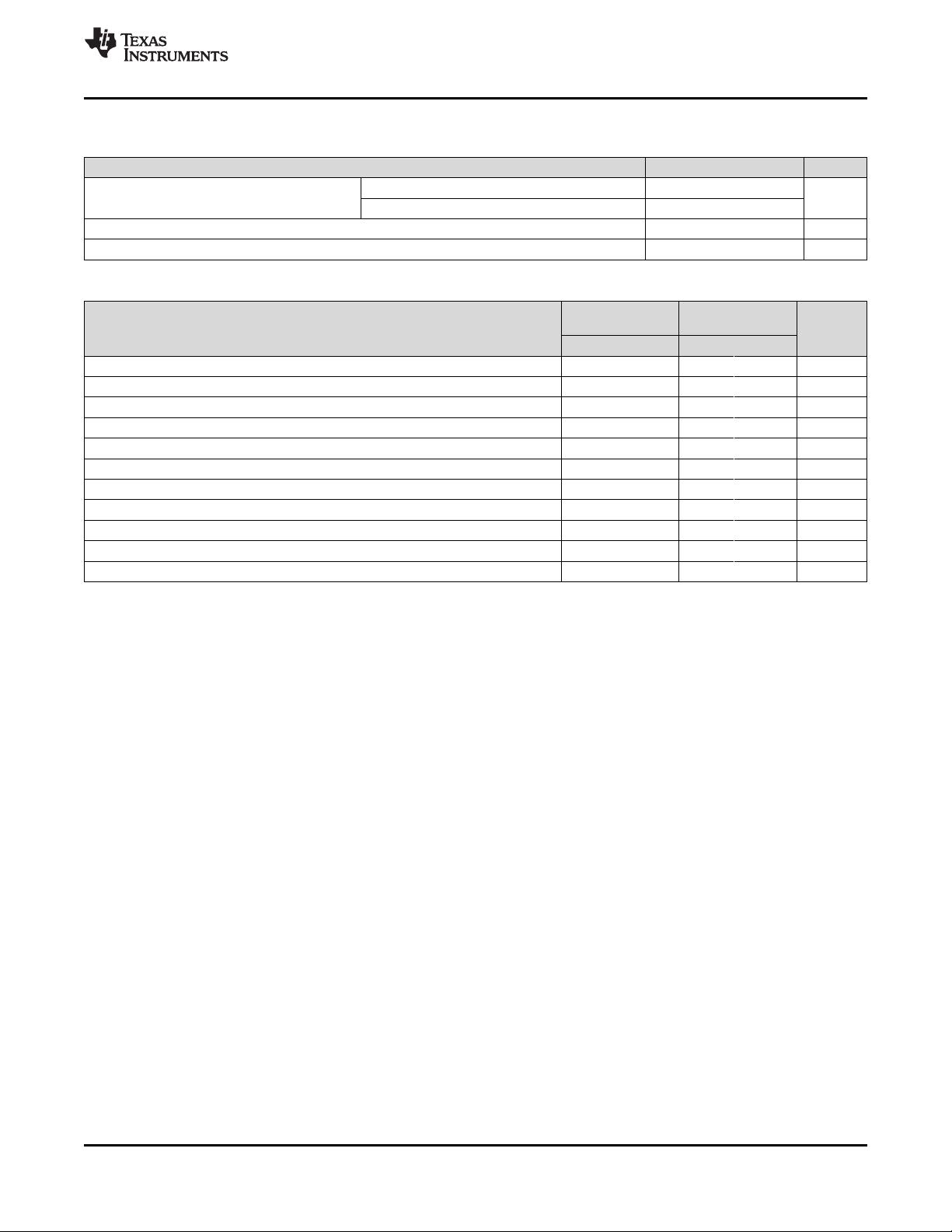

6.7 Timing Requirements: CLK_IN

over recommended ranges of supply voltage, load, and operating free-air temperature

MIN NOM MAX UNIT

f

CLK

LVCMOS clock input frequency

PLL bypass mode 0 160

MHz

PLL mode 8 160

t

r

/ t

f

Rise and fall time CLK signal (20% to 80%) 3 ns

Duty cycle CLK at V

DD

/2 40% 60%

(1) See Figure 13

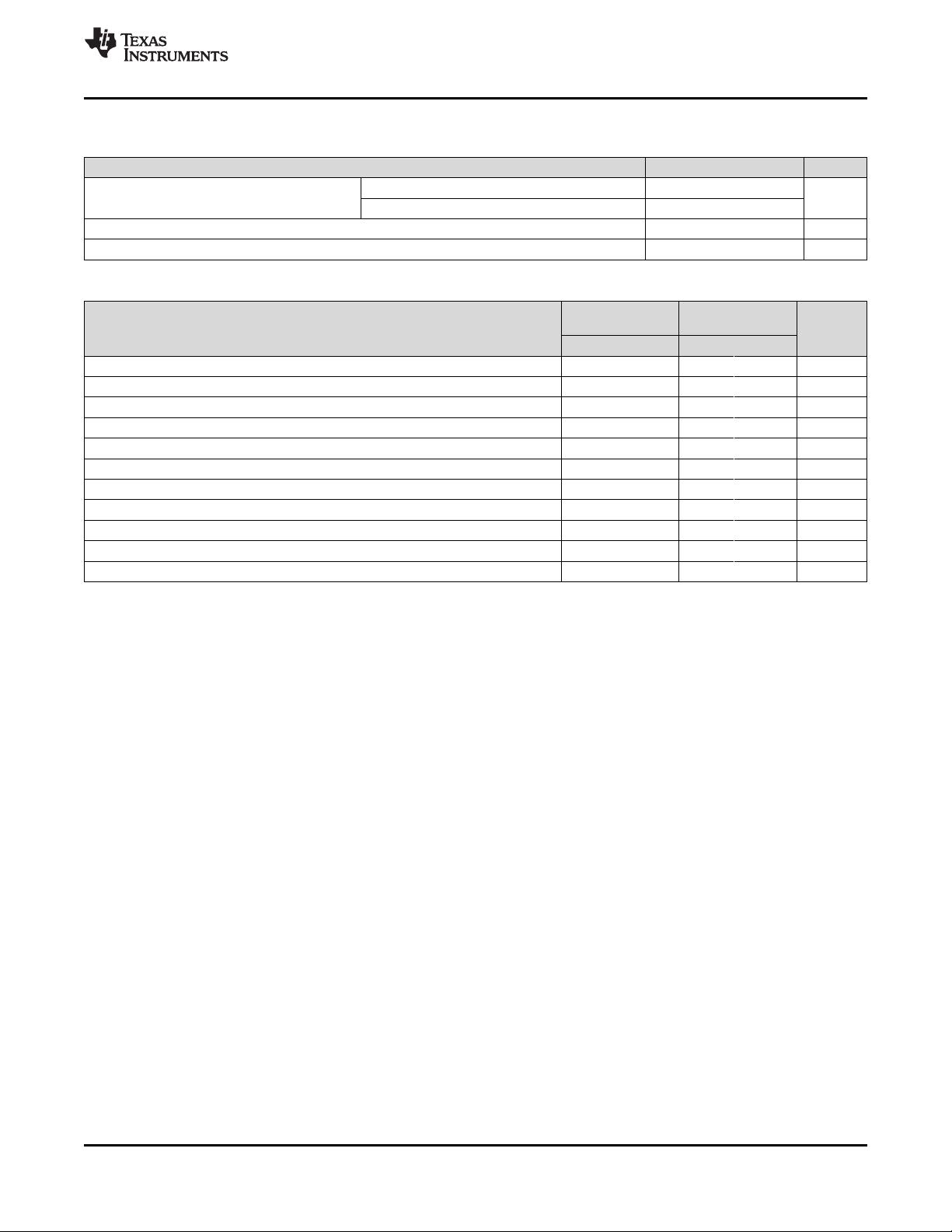

6.8 Timing Requirements: SDA/SCL

(1)

STANDARD

MODE

FAST MODE

UNIT

MIN MAX MIN MAX

f

SCL

SCL clock frequency 0 100 0 400 kHz

t

su(START)

START setup time (SCL high before SDA low) 4.7 0.6 μs

t

h(START)

START hold time (SCL low after SDA low) 4 0.6 μs

t

w(SCLL)

SCL low-pulse duration 4.7 1.3 μs

t

w(SCLH)

SCL high-pulse duration 4 0.6 μs

t

h(SDA)

SDA hold time (SDA valid after SCL low) 0 3.45 0 0.9 μs

t

su(SDA)

SDA setup time 250 100 ns

t

r

SCL/SDA input rise time 1000 300 ns

t

f

SCL/SDA input fall time 300 300 ns

t

su(STOP)

STOP setup time 4 0.6 μs

t

BUS

Bus free time between a STOP and START condition 4.7 1.3 μs