CMOS反相器设计:Cadence工具实战与工艺详解

需积分: 9 146 浏览量

更新于2024-07-27

收藏 261KB PDF 举报

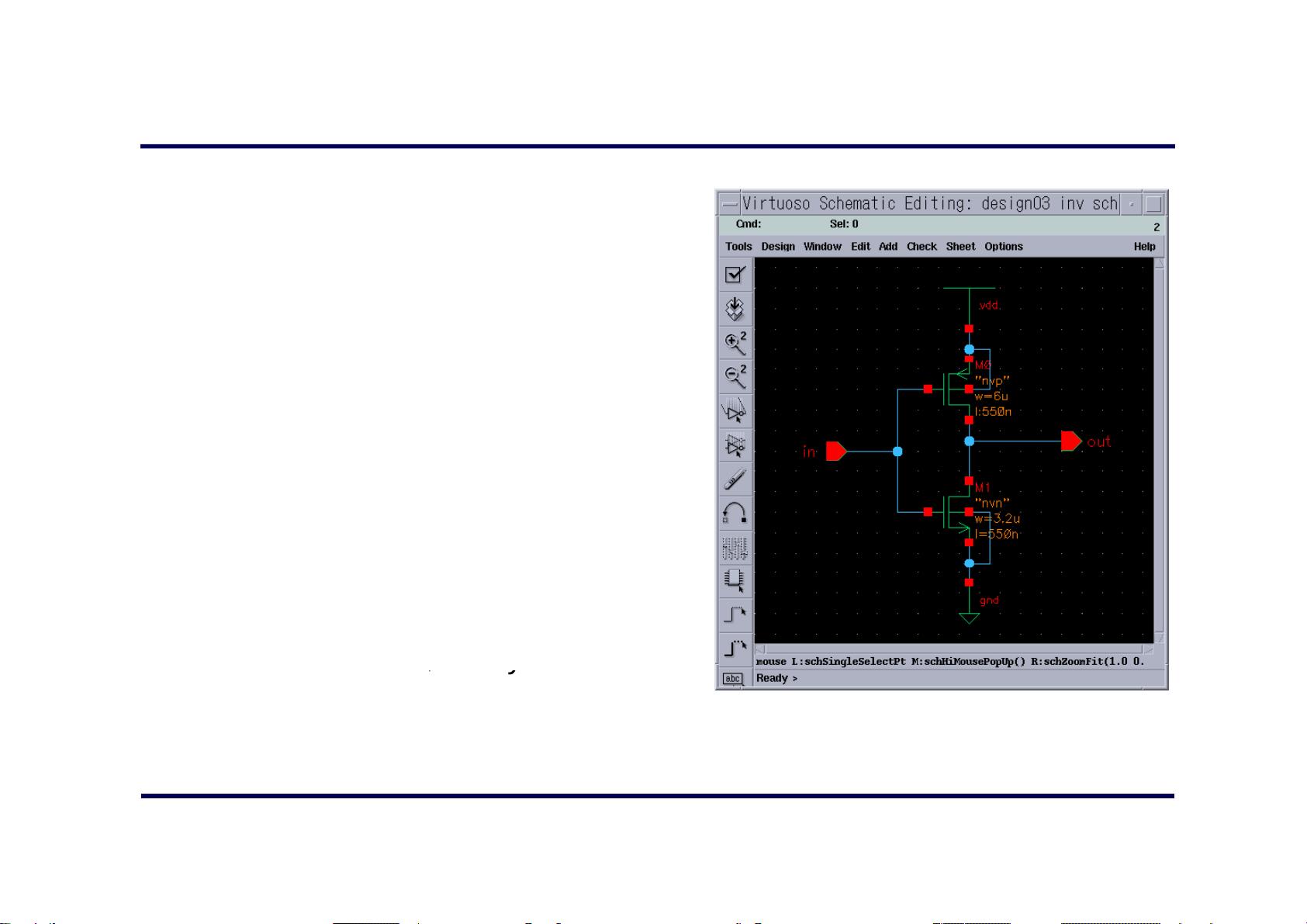

本文档主要介绍了在集成电路设计实习中关于CMOS Inverter的基本门电路设计实验,这是单元实验一的第二次课内容。CMOS Inverter是逻辑电路中最基础的组件之一,它是一种电压控制的双极性开关,利用互补的NMOS和PMOS管实现低功耗和高速度的逻辑功能。在这个实验中,参与者将学习并实践以下关键知识点:

1. 实验目的:通过本实验,学生需掌握基本门电路的版图设计技巧,熟悉Cadence等专业设计软件如Virtuoso XL的使用,包括版图设计、电路原理图输入、电路仿真以及版图验证等步骤。这有助于他们了解实际集成电路制造过程中的技术细节。

2. 版图设计:实验中使用CSMC双硅三铝混合信号工艺,涉及的主要设计层包括:TB(tub和n阱)、TO(有源区,分为主栅极和源漏区)、GT(多晶硅栅极)、SP和SN(P+和N+注入区)、金属层(A1、A2、W1-W3)以及多晶硅电阻阻挡层(IM)、电容相关结构(PC和PT)。学生需要根据电路原理图,精确地在这些层上绘制和布局电路元件。

3. 初始版图生成:使用Virtuoso XL,一个定制版图设计工具,从电路图开始,学生需依次进行schematic view的打开、电路图编辑和版图导出的流程。这个过程涉及到电路设计原则和规则的应用,以及如何确保电路性能和物理实现的兼容性。

4. 实践环节:实验的核心部分是设计一个2与非门,这需要学生将理论知识转化为实际操作,通过模拟和仿真来验证设计的正确性和有效性。这个阶段旨在提升学生的实践技能和问题解决能力。

总结来说,CMOS Inverter的单元实验一是一个系统学习集成电路设计的基础环节,涵盖了电路设计、软件工具运用和版图实现等多个层面,对于理解数字电路工作原理和半导体制造工艺至关重要。通过这个实习项目,学生能够加深对电子电路设计流程的认识,并为后续更复杂的集成电路设计打下坚实的基础。

169 浏览量

2025-01-06 上传

2025-01-06 上传

2025-01-06 上传

2025-01-06 上传

2025-01-06 上传