FPGA后仿真:ISE与Modelsim的直接与间接方法

"这篇文档介绍了如何使用ISE与Modelsim进行FPGA后仿真,特别是时序仿真的两种方法。作者毕成炜在文中详细讲解了直接和间接两种仿真方法的步骤,涉及的工具版本为ISE_12.2和ModeSim_6.5e。"

在FPGA设计流程中,后仿真是一种重要的验证手段,它可以检验设计在实际工作速度下的行为,确保设计满足时序要求。以下是对两种仿真方法的详细解释:

(一)直接方法:

1. 首先,创建一个专门的文件夹(例如D:\timing_sim),存放源代码和测试平台文件。

2. 在ISE中关闭当前项目,新建一个项目,选择合适的FPGA器件和仿真器(此处为Modelsim)。

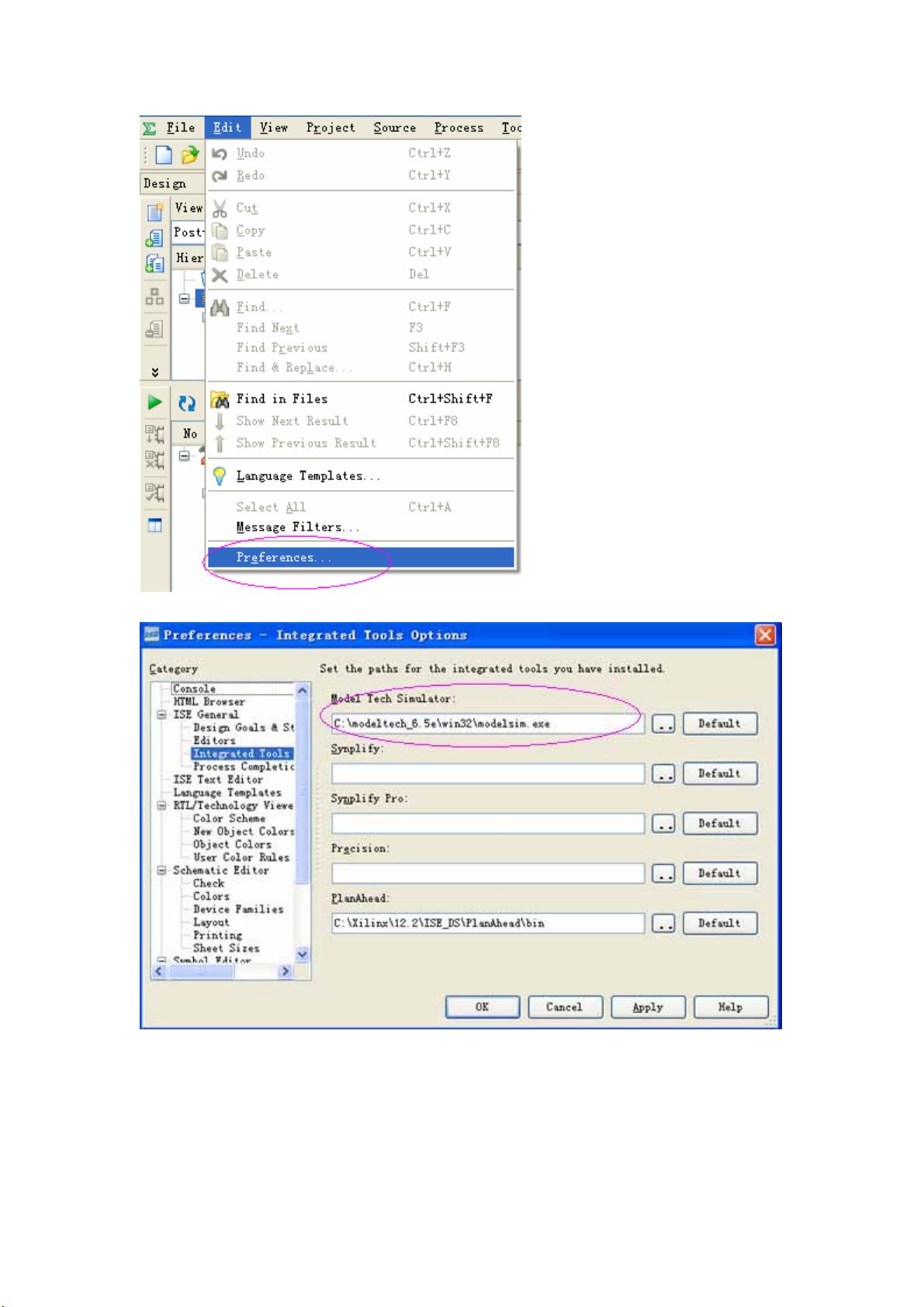

3. 在器件配置中确保选择了正确的仿真器,并在主菜单中设置Modelsim的执行文件路径。

4. 编译仿真库,这一步通常在ISE的相应目录下进行,确保使用与ISE兼容的Modelsim版本。

5. 生成的仿真库映射关系会写入ISE的modelsim.ini文件,但需手动将这些信息复制到Modelsim自身的modelsim.ini文件中,以确保两者同步。

(二)间接方法:

1. 单独启动Modelsim,然后使用ISE生成的用于后仿的文件夹netgen。

2. 在Modelsim中加载ISE生成的网表、库文件和测试平台,执行仿真。

这两种方法的核心都是确保Modelsim能正确识别和使用由ISE生成的仿真模型和配置信息。在进行仿真时,开发者需要编写测试平台,模拟输入信号,观察输出结果,以及分析波形图,以确认设计功能的正确性和时序的合理性。

在使用Modelsim进行仿真时,还需注意以下几点:

- 检查和更新modelsim.ini文件以确保库路径的正确性。

- 确保所有必要的库文件、IP核模型和用户自定义模块都已编译并链接到仿真环境中。

- 在仿真过程中,利用Modelsim的调试工具,如查看变量值、设置断点等,以便深入理解设计行为。

通过这两种方法,工程师可以在设计完成后对FPGA逻辑进行全面的功能和时序验证,确保在硬件实现前设计的正确性,从而减少后期可能出现的问题,提高设计的可靠性。

2012-08-18 上传

2019-03-29 上传

2018-06-21 上传

2017-04-26 上传

2020-08-09 上传

学习不止

- 粉丝: 17

- 资源: 4

最新资源

- DIY0920101213.rar_手机短信编程_Visual_C++_

- phoneformat:这是一个Swift 4+库,旨在简化iOS项目的电话号码格式

- Stringz是一款轻巧而功能强大的编辑器,可轻松快速地翻译您的iOS应用。-Swift开发

- Tabs URLs in current window (Wayl Assured)-crx插件

- 像素编辑器

- PyPI 官网下载 | simple-pid-1.0.1.tar.gz

- python官方3.9.0b5-amd64版本exe安装包

- node-feed-thumbnailer:一个基本的应用程序,用于从YAML文件中获取图像网址列表,并将其压缩并用作静态文件

- Whatfix for Creditkarma-crx插件

- flexible_pipeline

- scalene:Scalene:用于Python的高性能,高精度CPU和内存分析器

- pychetlabeller:一个基于python的图像标注标签工具箱。 该程序允许用户注释图像中的单个对象

- dagitty:结构因果模型的图形分析图形因果模型

- Kjunzhi.rar_数学计算_matlab_

- javascript-challenge

- nasa-image-search:使用Nasa Image数据库的简单搜索应用程序