FPGA实现按键防抖:原理与Verilog设计

下载需积分: 50 | PDF格式 | 458KB |

更新于2024-09-18

| 141 浏览量 | 举报

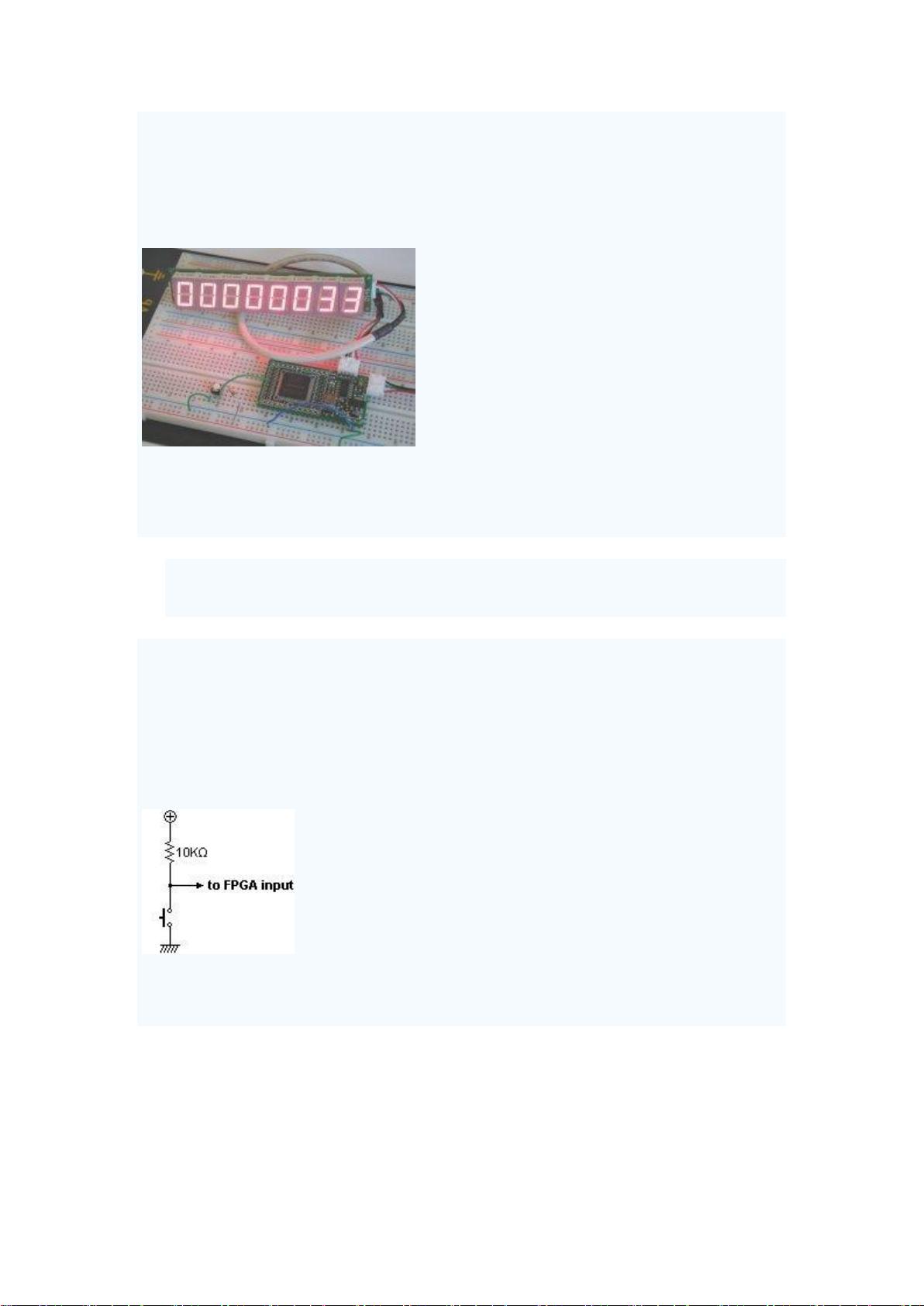

FPGA按键防抖是一个关键的电子设计技术,特别是在处理机械键盘等输入设备与FPGA之间的连接时。机械键盘由于其物理特性,按键信号可能存在抖动,导致FPGA无法准确识别按键状态。为了解决这个问题,通常采取的方法是消除这种抖动。

在FPGA按键防抖的项目中,主要分为两个部分:问题描述和解决办法。

1. **问题描述**

当将机械键盘与FPGA连接时,由于按键按下和松开过程中可能存在短暂的机械运动导致信号不稳定。理想情况下,按键信号应该是稳定的上升沿和下降沿,但实际测量中可能会出现以下不理想的波形:快速的上升和下降,或者多个毛刺。如果直接使用FPGA内部的计数器来检测按键状态,由于这些毛刺,计数器的计数可能无法正确反映按键的真实状态,从而影响系统的稳定性和准确性。

2. **解决办法**

- **硬件滤波**:一种传统方法是采用R/C滤波器结合施密特触发器来平滑按键信号,但这通常需要额外的硬件资源。然而,在FPGA内部实现更加灵活且简洁。

- **FPGA内部计数器**:利用FPGA的强大数字逻辑能力,可以设计一个自同步的解决方案。首先,使用触发器同步原始的异步按键信号PB,使其与系统时钟(例如20MHz)保持一致。然后,创建一个16位的计数器PB_cnt,每当PB信号从低变为高(表示按键按下)或从高变为低(表示按键松开)时,计数器递增。当计数器溢出(通常是2^16次),说明按键状态已经改变,此时输出PB_state、PB_down和PB_up信号,分别表示按键被按下、按下瞬间的高电平脉冲以及松开瞬间的高电平脉冲。

这个模块的Verilog代码定义了四个输出:clk用于同步,PB是原始按键信号,PB_state表示按键状态,PB_down和PB_up则是状态变化的同步信号。通过这种方法,FPGA能够有效地过滤掉按键抖动,提高系统的可靠性和响应精度。

总结来说,FPGA按键防抖的关键在于利用FPGA的逻辑处理能力和时钟同步机制,通过对按键信号的精确计数和处理,去除机械抖动,确保系统能准确地识别和响应按键操作。这是一种基础但重要的设计技术,对于许多实时或对输入稳定性有高要求的应用至关重要。

相关推荐

yuliguo123

- 粉丝: 1

最新资源

- Openaea:Unity下开源fanmad-aea游戏开发

- Eclipse中实用的Maven3插件指南

- 批量查询软件发布:轻松掌握搜索引擎下拉关键词

- 《C#技术内幕》源代码解析与学习指南

- Carmon广义切比雪夫滤波器综合与耦合矩阵分析

- C++在MFC框架下实时采集Kinect深度及彩色图像

- 代码研究员的Markdown阅读笔记解析

- 基于TCP/UDP的数据采集与端口监听系统

- 探索CDirDialog:高效的文件路径选择对话框

- PIC24单片机开发全攻略:原理与编程指南

- 实现文字焦点切换特效与滤镜滚动效果的JavaScript代码

- Flask API入门教程:快速设置与运行

- Matlab实现的说话人识别和确认系统

- 全面操作OpenFlight格式的API安装指南

- 基于C++的书店管理系统课程设计与源码解析

- Apache Tomcat 7.0.42版本压缩包发布