Verilog HDL深度探索:时序篇——步骤与时钟解析

"深入探讨Verilog HDL中的时序概念,包括步骤、时钟、综合与仿真"

在Verilog HDL的时序篇中,我们主要关注的是如何利用这种硬件描述语言来描述和理解数字系统的动态行为。时序设计是Verilog HDL的核心,因为它涉及到系统在时间上的操作和交互。

首先,我们要理解"步骤"和"时钟"的概念。步骤,从宏观上看,可以被视为模块执行的节奏或节拍,它定义了设计中各个操作的顺序。在微观层面上,步骤代表了模块内部的操作过程或状态转换。通过将传统的状态机替换为步骤,我们可以实现更灵活的设计,比如模拟顺序操作,这有助于避免因状态机复杂度过高导致的模块臃肿和表达能力下降问题。

时钟在数字系统中扮演着至关重要的角色,它是模块的心跳,标志着时间的流逝和数据处理的同步点。时钟周期是模块处理信息的最小时间单位。时钟的正确管理和使用对于确保模块间正确通信至关重要。如果模块间的通信出现问题,很可能是由于时钟同步问题,即某个模块的时钟比其他模块快或慢一个时钟周期。

在建模过程中,步骤和时钟的清晰表示对于模块的细化和优化非常关键。它们提供了模块操作的可视化表示,使得设计者能够更好地理解和改进模块的行为。

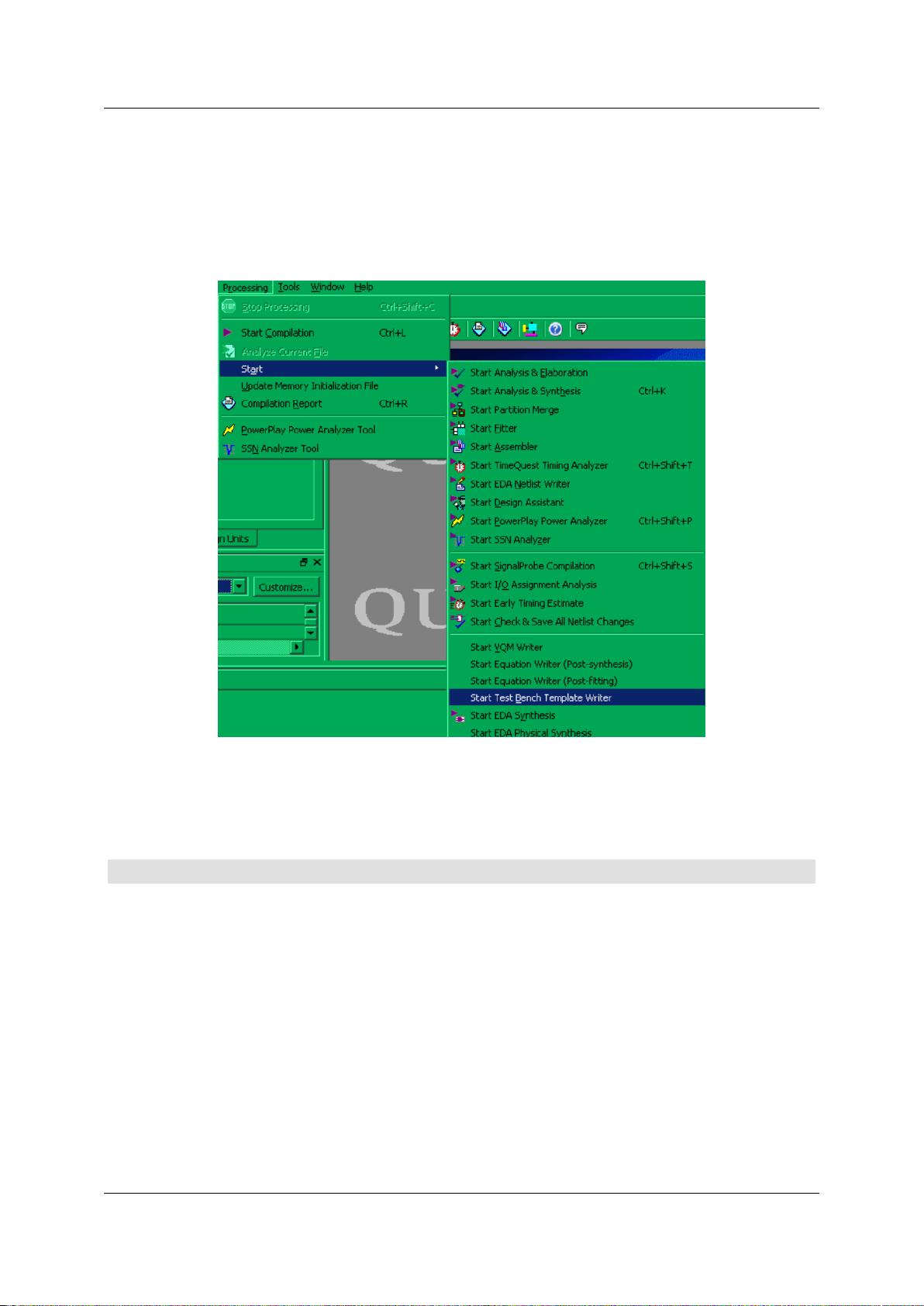

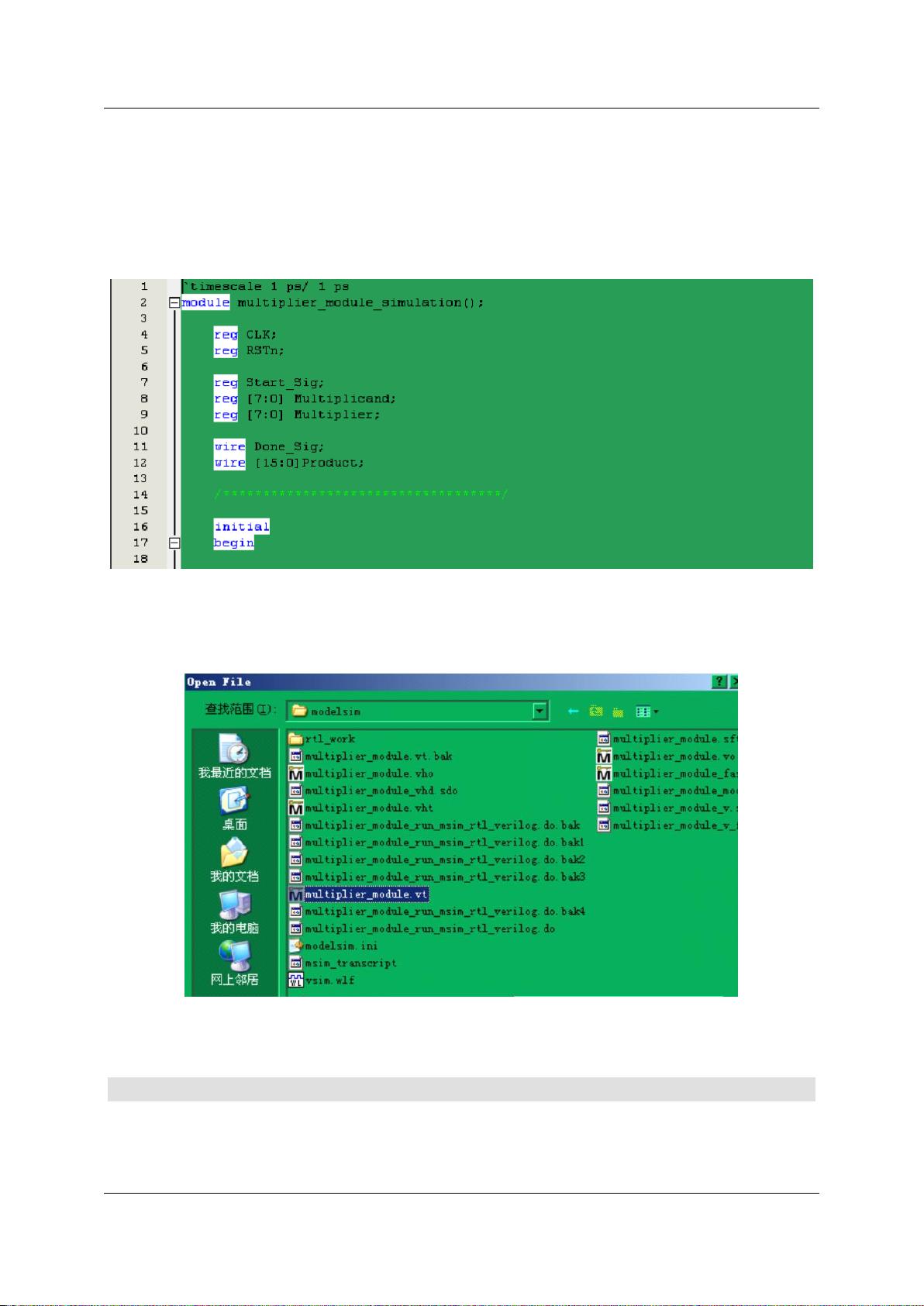

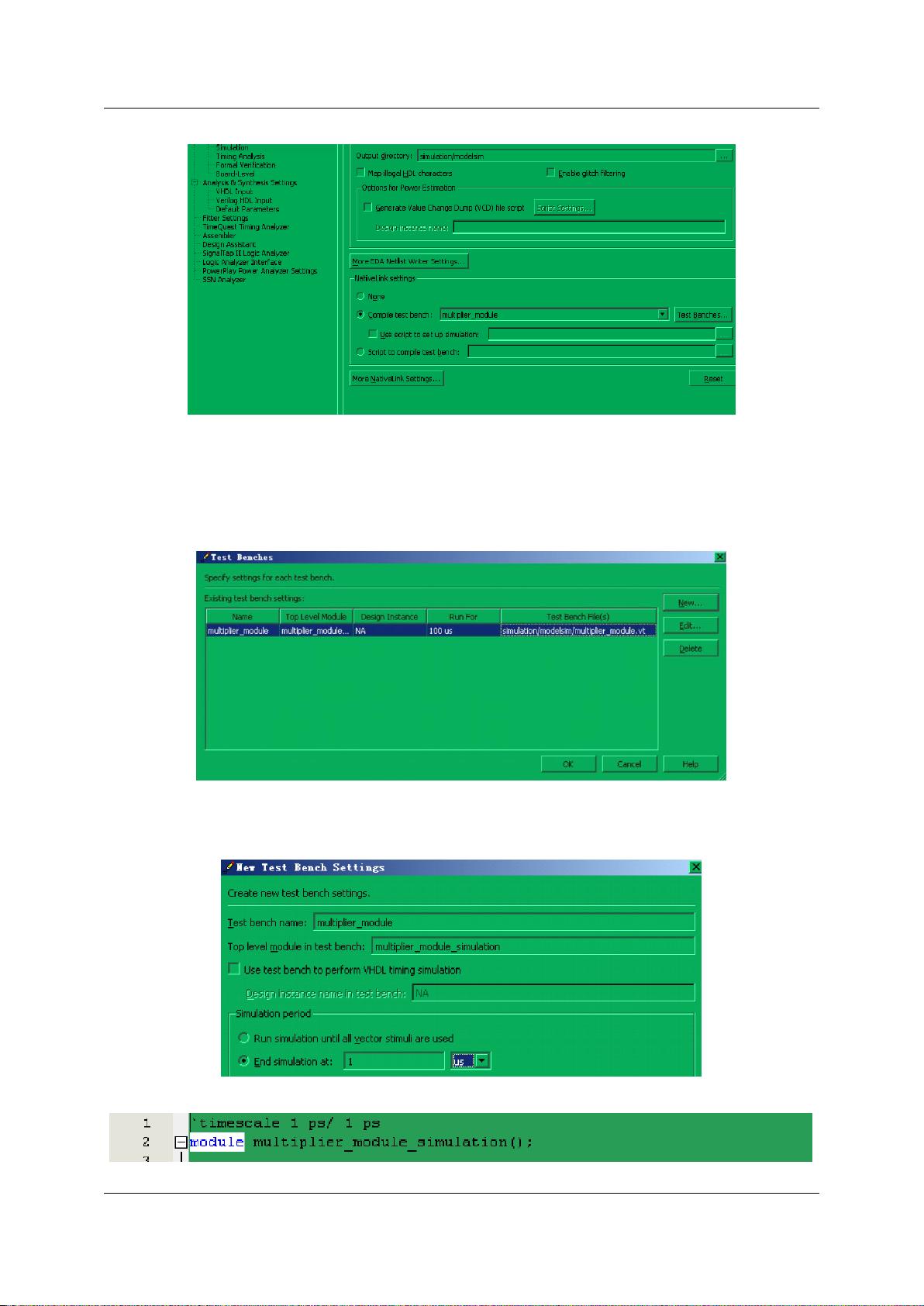

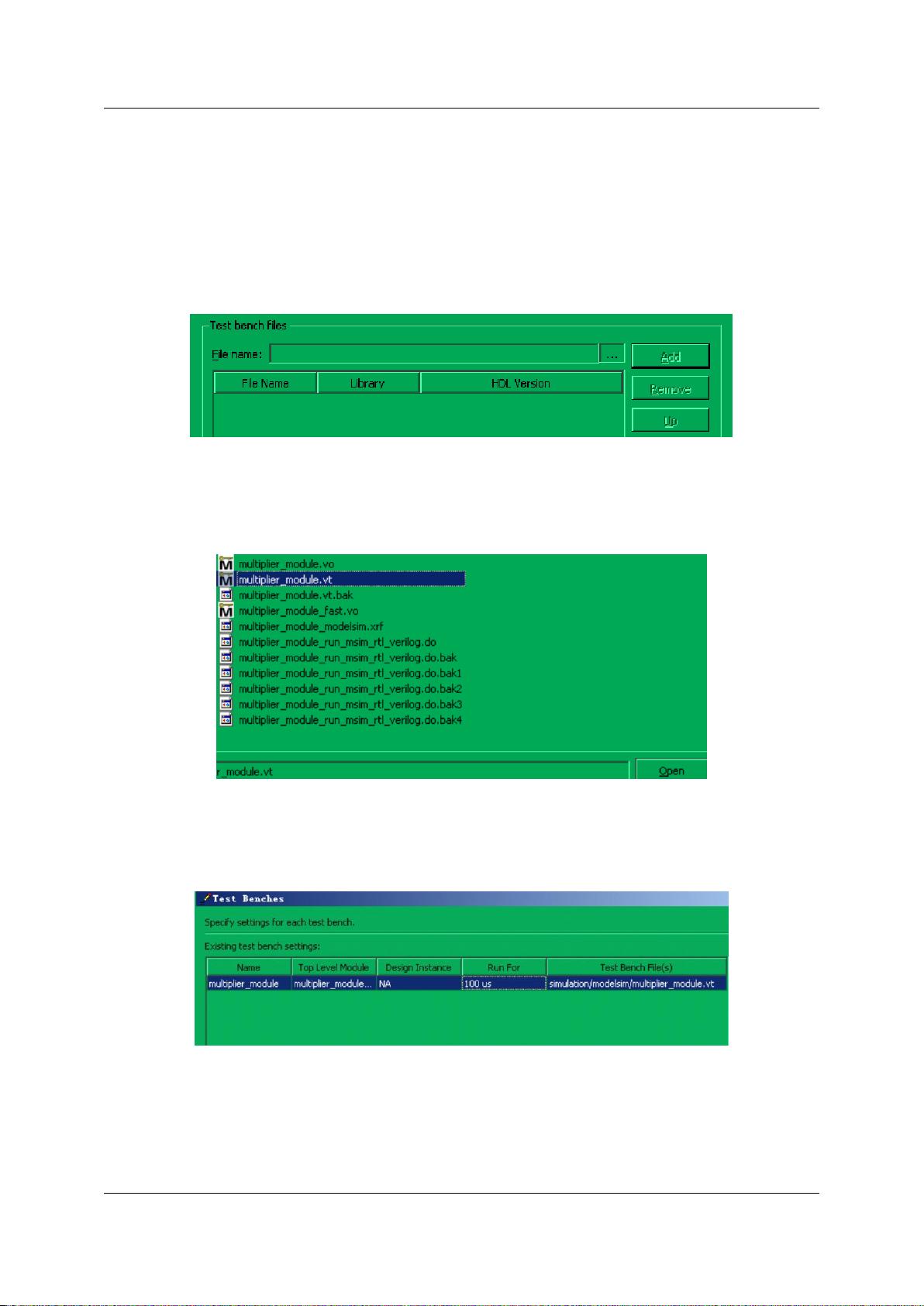

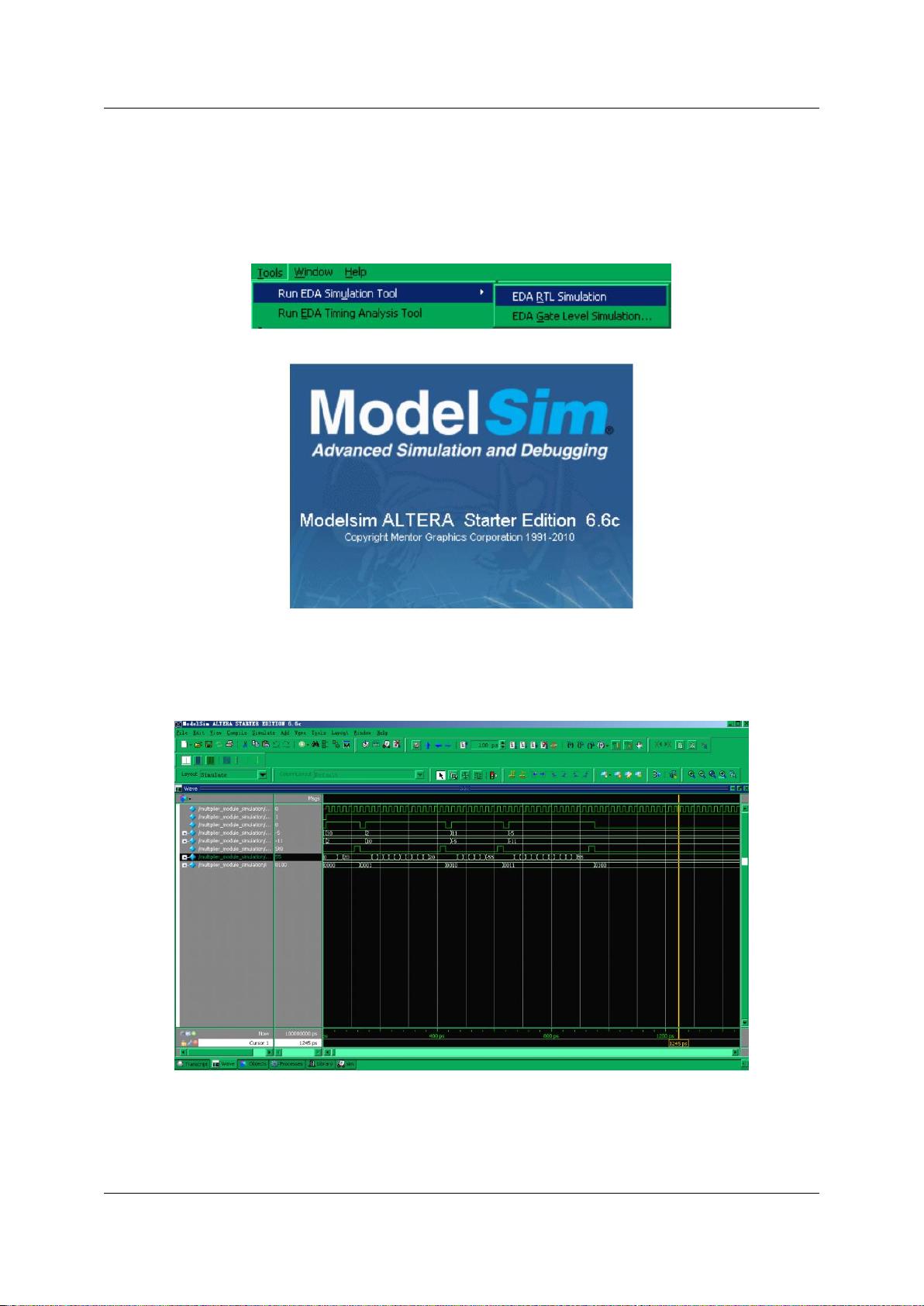

接下来,我们转向"综合"和"仿真"。综合是将Verilog HDL代码转换为实际可实现的电路的过程,它涉及到逻辑优化、资源分配等步骤。而仿真则是验证设计功能是否符合预期的过程,它允许我们在实际硬件制造前对设计进行测试。将这两者结合学习,可以帮助我们更好地理解设计流程,从抽象的描述到实际的硬件实现。

在多模块设计中,理解时钟同步和通信至关重要,因为任何通信失误都可能导致整个系统性能下降甚至失效。通过深入理解时序概念,设计师可以有效地定位和解决这些问题,从而提高设计的可靠性和效率。

Verilog HDL的时序篇提供了关于如何构建、分析和优化数字系统的关键知识,涵盖了从基本的时序概念到复杂的综合和仿真流程。这对于我们理解和设计复杂的数字系统来说,是必不可少的基础。

2021-10-03 上传

2019-07-11 上传

2018-01-09 上传

2023-06-14 上传

2023-06-10 上传

2023-06-10 上传

2023-05-16 上传

2023-05-24 上传

2023-06-04 上传

陳强-AI中医

- 粉丝: 0

- 资源: 5

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用