异步时序逻辑电路分析:脉冲异步电路的原理与约束

需积分: 49 71 浏览量

更新于2024-07-23

收藏 1.51MB PPT 举报

"异步时序逻辑电路的分析与理解"

异步时序逻辑电路是数字逻辑设计中的一个重要组成部分,尤其在复杂系统中,它能够处理不同速度和时序的信号,提供灵活的设计方案。与同步时序逻辑电路相比,异步时序逻辑电路不依赖于统一的时钟信号,而是通过外部信号的变化直接驱动电路状态的更新。

异步时序逻辑电路的特点在于电路中不存在全局的时钟信号,各个存储元件(如触发器)的状态变化和维持时间可以不同,甚至可能出现非稳定状态。这种灵活性也带来了一定的挑战,因为信号的变化过程可能会受到不可预知的时间延迟影响,从而可能导致错误的状态转移。

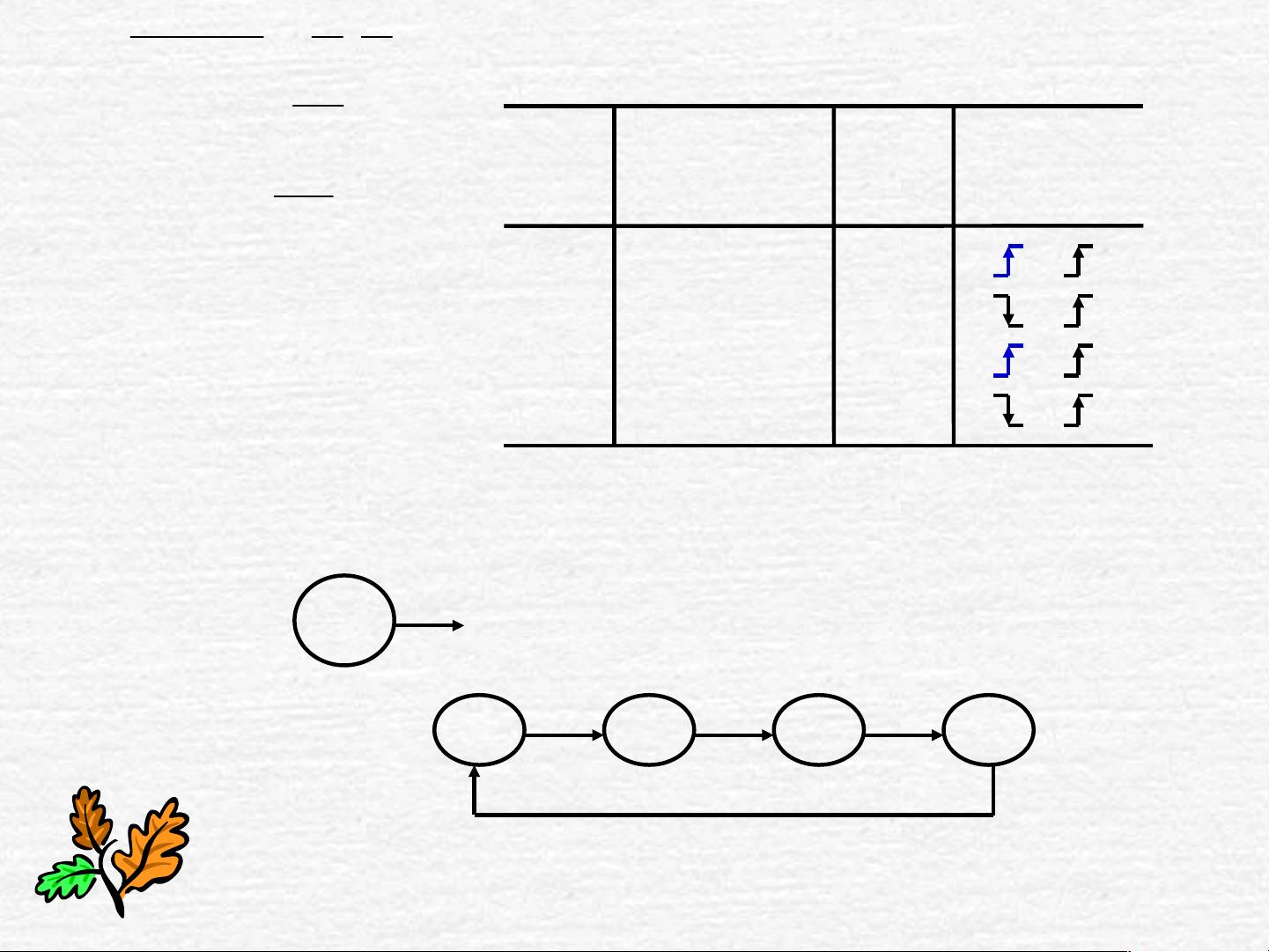

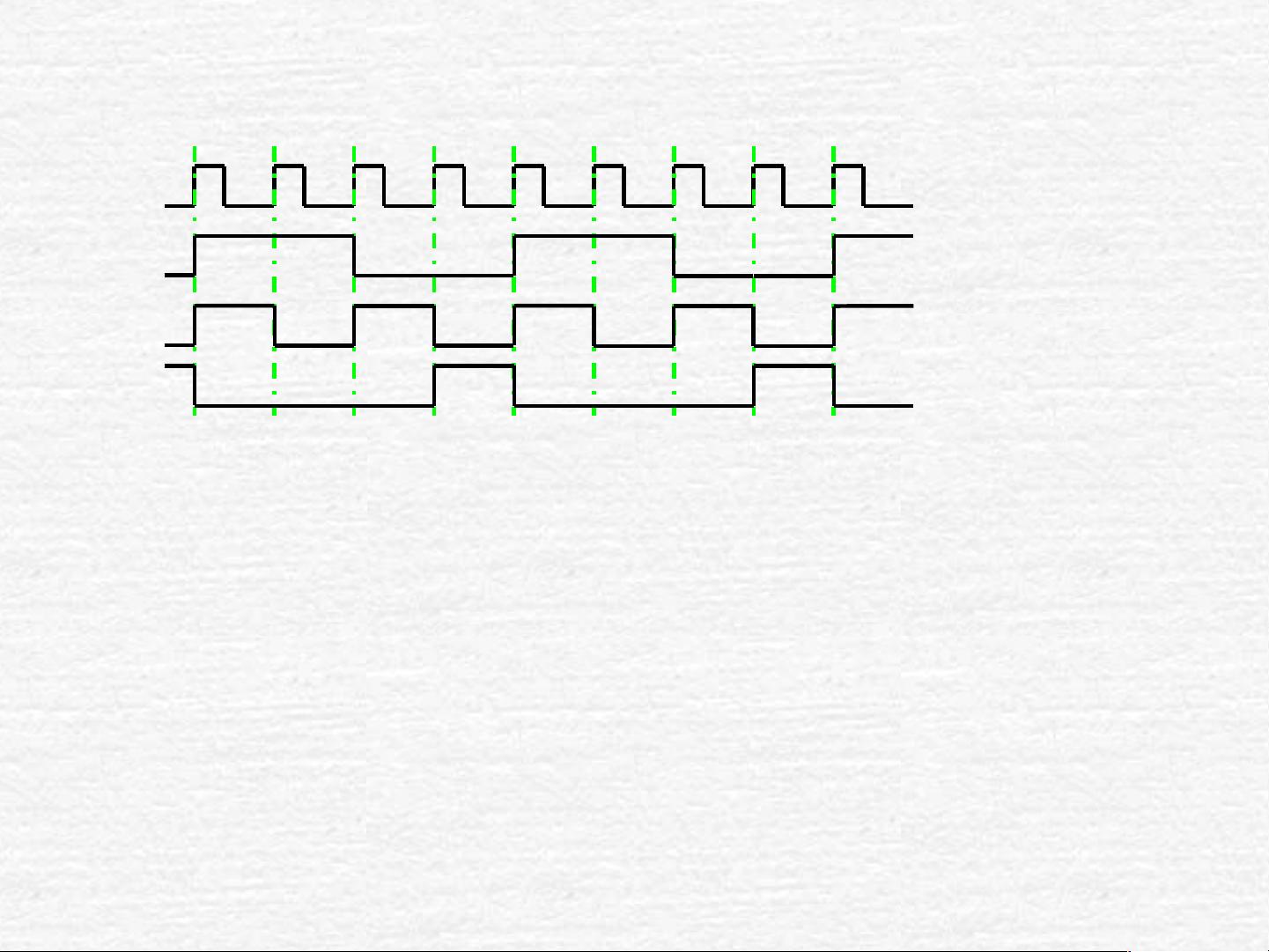

在脉冲异步时序逻辑电路中,存储元件通常由触发器构成,这些触发器可以是钟控的,也可以是非钟控的。对于钟控触发器,时钟脉冲的宽度和间隔必须满足一定的条件,以确保触发器能可靠地翻转,并且在一个脉冲的响应完全结束之后,下一个脉冲才能到来。而对于非钟控触发器,我们必须关注输入端的脉冲信号,因为它会直接影响到触发器的状态变化。

分析脉冲异步时序逻辑电路的过程与同步电路类似,但有一些关键的区别。首先,如果存储元件是钟控触发器,我们需要考虑时钟信号对激励函数的影响,只有当时钟端有脉冲时,触发器的状态才会根据输入发生改变。而如果是非钟控触发器,我们则需要关注输入端的脉冲。在分析状态转移时,由于仅允许一个输入端有脉冲,所以只需要考虑每一种单独脉冲的情况,而不是所有可能的组合,这大大简化了分析的复杂性。

以一个具有三个输入端的示例电路为例,如果“1”表示有脉冲,那么有四种可能的输入取值:000, 001, 010, 100。在分析时,我们只需考虑后三种情况,因为输入全为0时,电路状态不会改变。电路的分析包括写出时钟方程、输出方程和触发器的驱动方程,然后求解触发器的次态方程,以确定电路在给定输入下的行为。

在实际应用中,设计异步时序逻辑电路需要深入理解其工作原理和约束条件,以确保电路的正确性和可靠性。这类电路广泛应用于通信系统、嵌入式系统以及计算机硬件设计中,因为它们能够适应各种不同的时序环境,提高系统的效率和鲁棒性。

异步时序逻辑电路是一种复杂但强大的工具,它能够处理复杂的时序问题,但同时也需要更精细的设计和分析。通过理解和掌握异步时序逻辑的基本概念和分析方法,工程师们能够创建出更加灵活和适应性强的数字系统。

1197 浏览量

363 浏览量

281 浏览量

160 浏览量

169 浏览量

2024-11-01 上传

153 浏览量

252 浏览量

许巧人

- 粉丝: 0

最新资源

- 子空间聚类与字典学习结合的图像信号处理方法

- Axure组件库:iPhone6定制版资源

- 实现个性化树形菜单的JS代码包下载

- 深入掌握CodeIgniter框架技术精粹

- 一键刷入boot文件简易操作指南

- 天人文章屏蔽右键及复制插件安装与使用教程

- 网络路径重写实例教程分享

- 深入解析cglib动态代理所需的两个关键JAR包

- GitHub Classroom创建的有序双向链表实现分析

- 智能充电设备的应用程序启动技术探究

- 构建基础动态网站:用户注册与登录系统

- C语言实现多目标寻优的黄金分割法与区间搜索

- Eclipse下的LeakCanary与Demo集成快速指南

- STM32F407 GPIO控制LED闪烁程序实例

- Java网吧计费系统源码分享与学习指南

- Regoch-Websocket-Nodejs:NodeJS平台上的高效Websocket客户端实现