FPGA亚稳态问题详解与解决策略

需积分: 42 153 浏览量

更新于2024-09-09

2

收藏 442KB PDF 举报

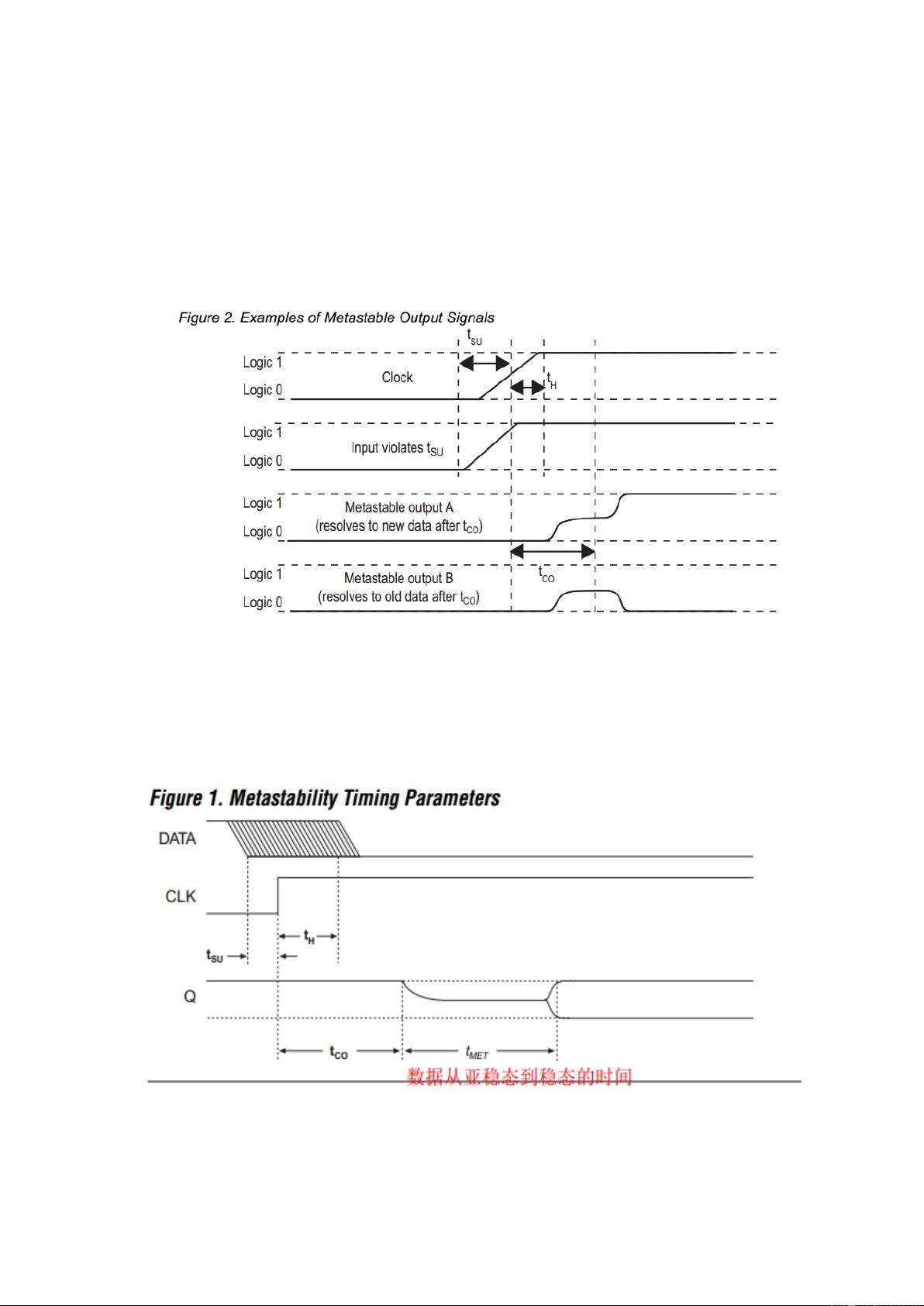

"本文主要探讨了FPGA中的亚稳态问题,包括其发生原因、解决方法和相关评价指标。亚稳态通常出现在非同步系统中,由于异步输入数据未满足触发器的时序要求,导致输出不稳定。解决亚稳态问题的方法包括增加tMET、使用更快的器件以及采用多级同步器。同步系统的定义和如何避免亚稳态也进行了阐述,并提供了相关参考文献。"

在数字系统设计中,FPGA(Field-Programmable Gate Array)因其灵活性和高性能而广泛使用。然而,亚稳态是FPGA设计中常见的问题,特别是在处理异步数据时。亚稳态是指数据在触发器的输出阶段不稳定,既不是明确的0也不是明确的1,而是在两者之间徘徊,这种状态可能导致系统功能的不确定性。

亚稳态的发生条件通常是在非同步系统中,当异步输入数据未能在触发器的建立时间(Tsu)和保持时间(Th)内稳定下来,导致触发器无法正确捕获数据。同步系统由于所有寄存器共享同一个时钟或时钟间有相位关系,可以避免亚稳态问题。

亚稳态的评价指标之一是MTBF(Mean Time Between Failures),即两次错误之间的时间间隔。MTBF越大,表示系统发生亚稳态的概率越小。通过增加数据稳定的延迟时间tMET,可以显著提高MTBF。

为了解决亚稳态,设计者可以采取以下策略:

1. 增加tMET:延长数据稳定时间,使得触发器有足够的窗口期来正确捕获数据。

2. 使用更快的器件:更快的器件可以提供更短的时钟传播时间(tCO)和建立时间(tSU),减少亚稳态出现的可能性。

3. 多级同步器:通过多级DFF来提高数据的稳定性,即使第一级产生亚稳态,后续级可能有机会将其稳定。但这会导致数据传输的延迟增加。

同步系统定义了所有寄存器在同一时钟域内工作,除了最后一个寄存器,每个寄存器的扇出为1,这样的设计有助于确保时序的正确性。当需要处理异步信号时,可以通过时钟倍频或同步器来解决亚稳态问题。

为了深入理解并解决FPGA中的亚稳态问题,可以参考文献《Metastability in Altera Devices》和《Understanding Metastability in FPGAs》,这两份文档提供了更多关于亚稳态的理论背景和实际应用指导。通过理解和应用这些知识,设计者能够更有效地避免和管理FPGA中的亚稳态问题,从而保证系统的可靠性和稳定性。

663 浏览量

557 浏览量

230 浏览量

200 浏览量

点击了解资源详情

134 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

半夜暴走徒

- 粉丝: 0

- 资源: 4

最新资源

- 基于Laravel 8.x的API接口签名认证系统

- PayPal-NET-SDK:用于PayPal RESTful API的.NET SDK

- aireACUMAR:阿卡马尔(ACUMAR)的拿破仑日报

- 广告说服观点

- 基于深度置信网络的多输入单输出回归预测(DBN)(Matlab完整程序和数据)

- decisionmaker:一个微型的Web应用程序,可以帮助您做出决策

- redditclone实践:遵循Spring Boot和Angular教程-通过freeCodeCampprogrammingtechie构建Reddit克隆(编码项目)

- pokemon-weakness-android:Pokemon Weakness的Android应用程序的源代码-Android application source code

- jsonlines:python库可简化jsonlines和ndjson数据的使用

- leetcode答案-EulerFS:欧拉FS

- AmazonS3Client.rar

- go-migrate:用Go编写的抽象迁移框架

- 监控视频.dav文件转码工具,支持转换为多种格式(MP4、AVI、WMV、MXF、GIF、DPG、MTV、AMV、SWF等)

- CM回购

- babel_pug_project:使用babel,pug,node,express进行Web服务器教育

- STNFCSensor_Android:ST NFC Sensor Android应用程序源代码-Android application source code