计算机组成原理之总线与存储器技术解析

需积分: 6 28 浏览量

更新于2024-07-16

收藏 7.12MB DOCX 举报

"该文档是关于计算机组成原理的复习资料,涵盖了总线的概念、分类、控制,以及同步和异步通信的区别。同时讨论了总线数据传输率、总线标准和即插即用等概念。此外,内容还涉及到存储器的层次结构、存取周期、带宽计算,以及内存寻址和编址方式。最后,提到了动态RAM的刷新机制和不同刷新方法的间隔,以及如何用不同规格的存储芯片构建存储器系统。"

详细知识点解释:

1. **总线**:总线是计算机硬件系统中连接各个组件的公共通信路径,具有共享、并行传输数据的特点。为了减轻总线负载,总线上的部件应具备独立工作和响应总线信号的能力。

2. **总线分类**:总线可以分为数据总线、地址总线和控制总线。系统总线包括CPU总线、内存总线和I/O总线,分别用于CPU与内存、CPU与外设之间的通信。它们可能是单向或双向的,并与机器字长、存储字长和存储单元大小相关。

3. **总线判优控制**:用于解决多个设备同时请求使用总线的情况,常见的控制方式有集中式和分布式。集中式包括菊花链和仲裁环,其中菊花链响应时间最快,但对电路故障敏感。

4. **同步通信与异步通信**:同步通信中,数据传输以固定的时钟速度进行,所有设备必须同步;异步通信则允许设备根据自身速度发送数据,通过起始位和停止位来调整同步。

5. **分离式通讯**:特点是数据传输独立于控制信号,常用于高速、低延迟的系统。

6. **总线标准**:定义了总线的物理特性和操作协议,如PCI、PCIe、USB、Ethernet等。设置标准是为了确保设备间的兼容性和互换性。即插即用允许设备无需预先配置即可在系统中使用,如PCI、USB等。

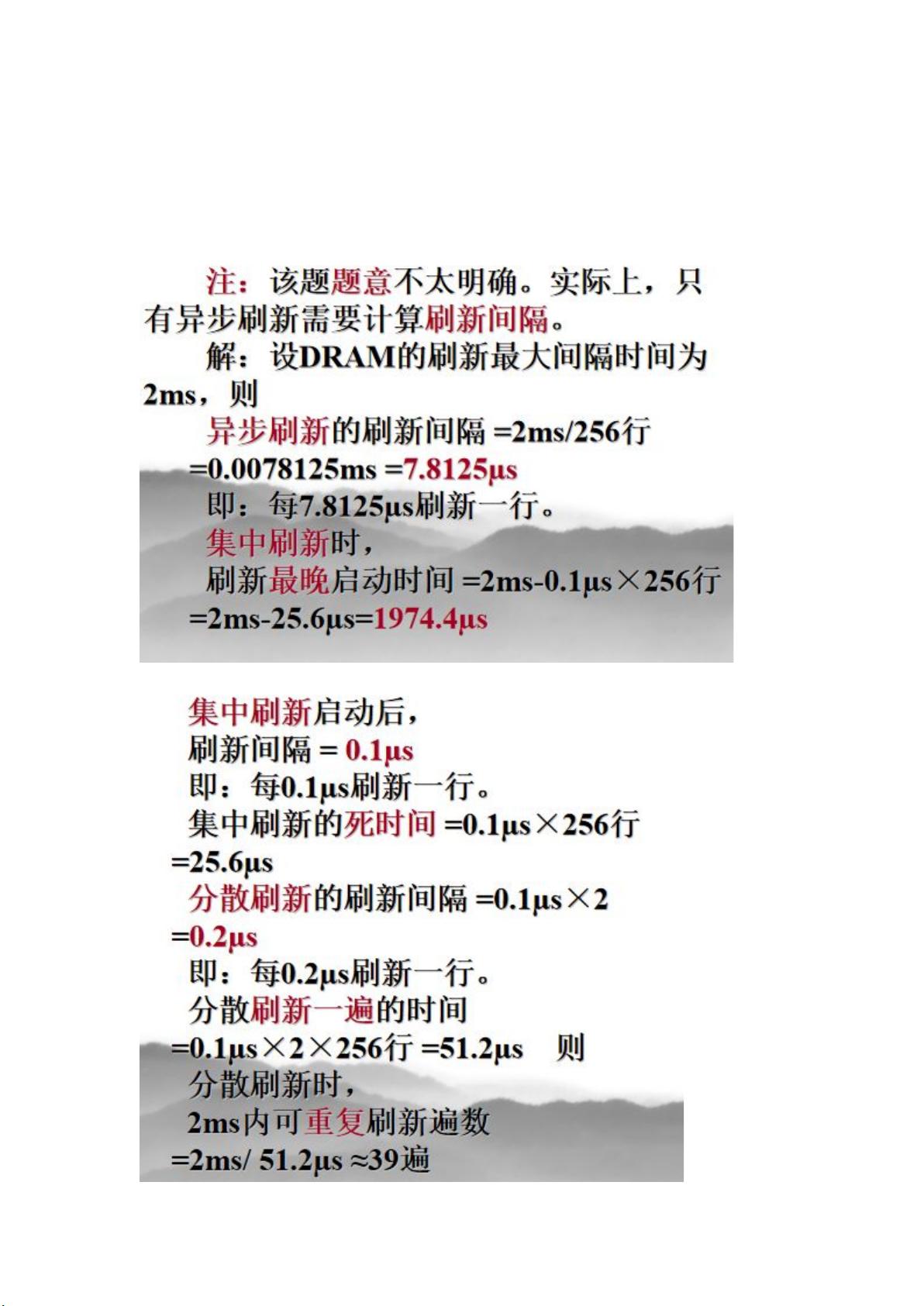

7. **总线数据传输率**:与总线宽度和频率直接相关,宽度越大,频率越高,传输速率越快。带宽计算公式为:带宽 = 总线宽度 * 频率。

8. **存储器层次结构**:体现于高速缓存、主存和辅助存储器之间,目的是通过牺牲容量换取访问速度。分层的原因是为了平衡速度、容量和成本。计算机通过地址映射和替换策略管理这些层次。

9. **存取周期与存取时间**:存取周期包含一个读周期和一个写周期,是连续两次独立访问存储器的时间;存取时间仅指完成一次读或写操作所需的时间。

10. **存储器带宽**:表示单位时间内能从存储器中读取或写入数据的速率,计算公式为:带宽 = 数据总线宽度 / 存取周期。

11. **寻址范围**:对于32位字长和64KB存储容量的系统,按字编址寻址范围是64KB / 32位/字 = 2^14 字。

12. **动态RAM刷新**:由于DRAM需要定期刷新以保持数据,否则会丢失。刷新方法有集中刷新、分散刷新和异步刷新,刷新间隔根据芯片特性而定。

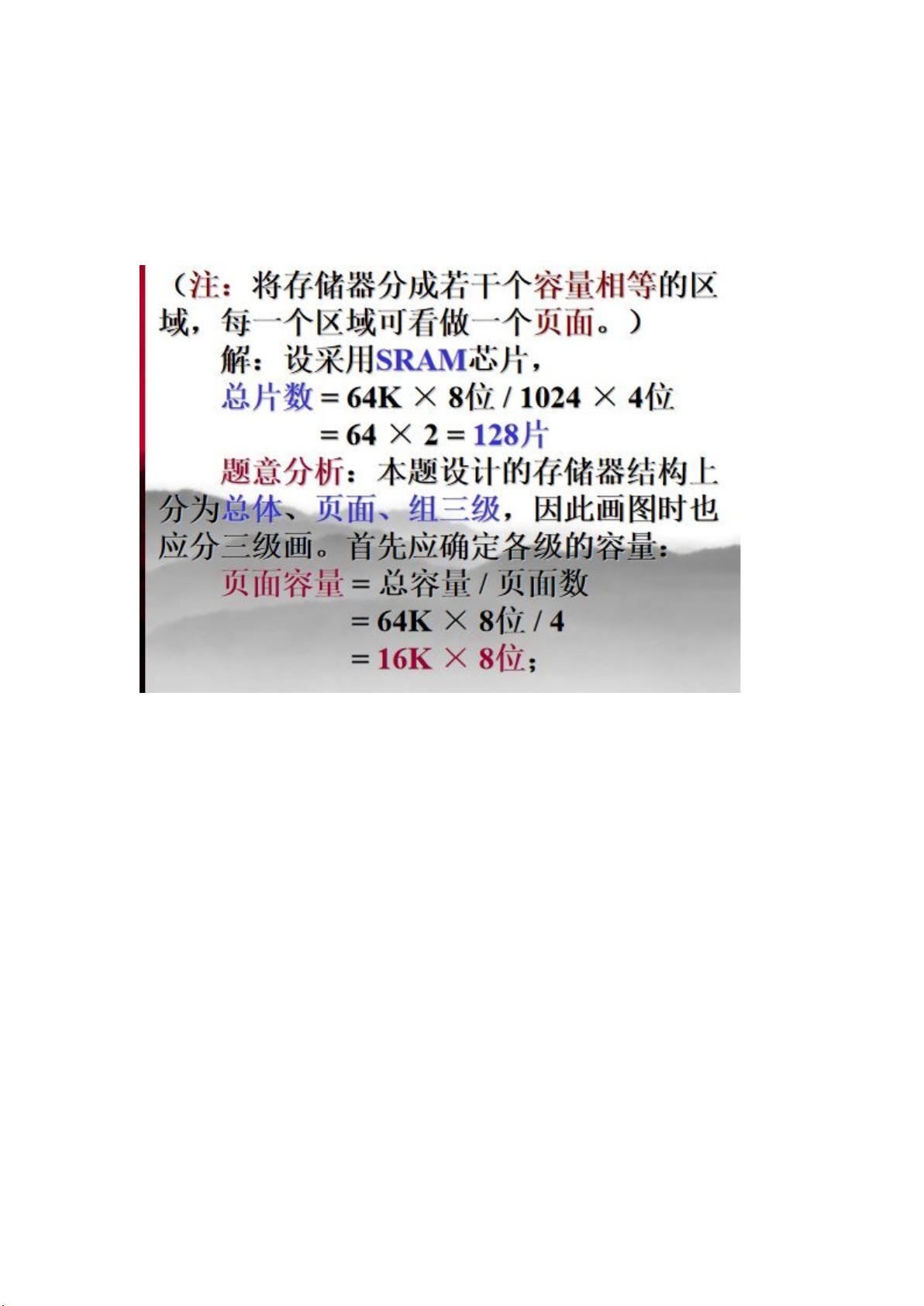

13. **存储器构建**:构建64K×8位存储器可能需要使用16K×32位或1024×4位的芯片,具体数量取决于芯片规格和存储器组织方式。

14. **存储基元**:64K×8位的RAM芯片含有64K * 8位 = 65536个存储基元。

15. **设计存储器系统**:此部分涉及如何使用1024×4位的芯片构建64K×8位的存储器,需要考虑页面和组的划分,以及所需的芯片数量。具体实现通常涉及地址译码和多片芯片的级联。

1353 浏览量

2021-09-30 上传

2021-12-06 上传

2680 浏览量

271 浏览量

2021-11-25 上传

2022-07-14 上传

Healer66

- 粉丝: 333

最新资源

- ITween插件实用教程:路径运动与应用案例

- React三纤维动态渐变背景应用程序开发指南

- 使用Office组件实现WinForm下Word文档合并功能

- RS232串口驱动:Z-TEK转接头兼容性验证

- 昆仑通态MCGS西门子CP443-1以太网驱动详解

- 同步流密码实验研究报告与实现分析

- Android高级应用开发教程与实践案例解析

- 深入解读ISO-26262汽车电子功能安全国标版

- Udemy Rails课程实践:开发财务跟踪器应用

- BIG-IP LTM配置详解及虚拟服务器管理手册

- BB FlashBack Pro 2.7.6软件深度体验分享

- Java版Google Map Api调用样例程序演示

- 探索设计工具与材料弹性特性:模量与泊松比

- JAGS-PHP:一款PHP实现的Gemini协议服务器

- 自定义线性布局WidgetDemo简易教程

- 奥迪A5双门轿跑SolidWorks模型下载