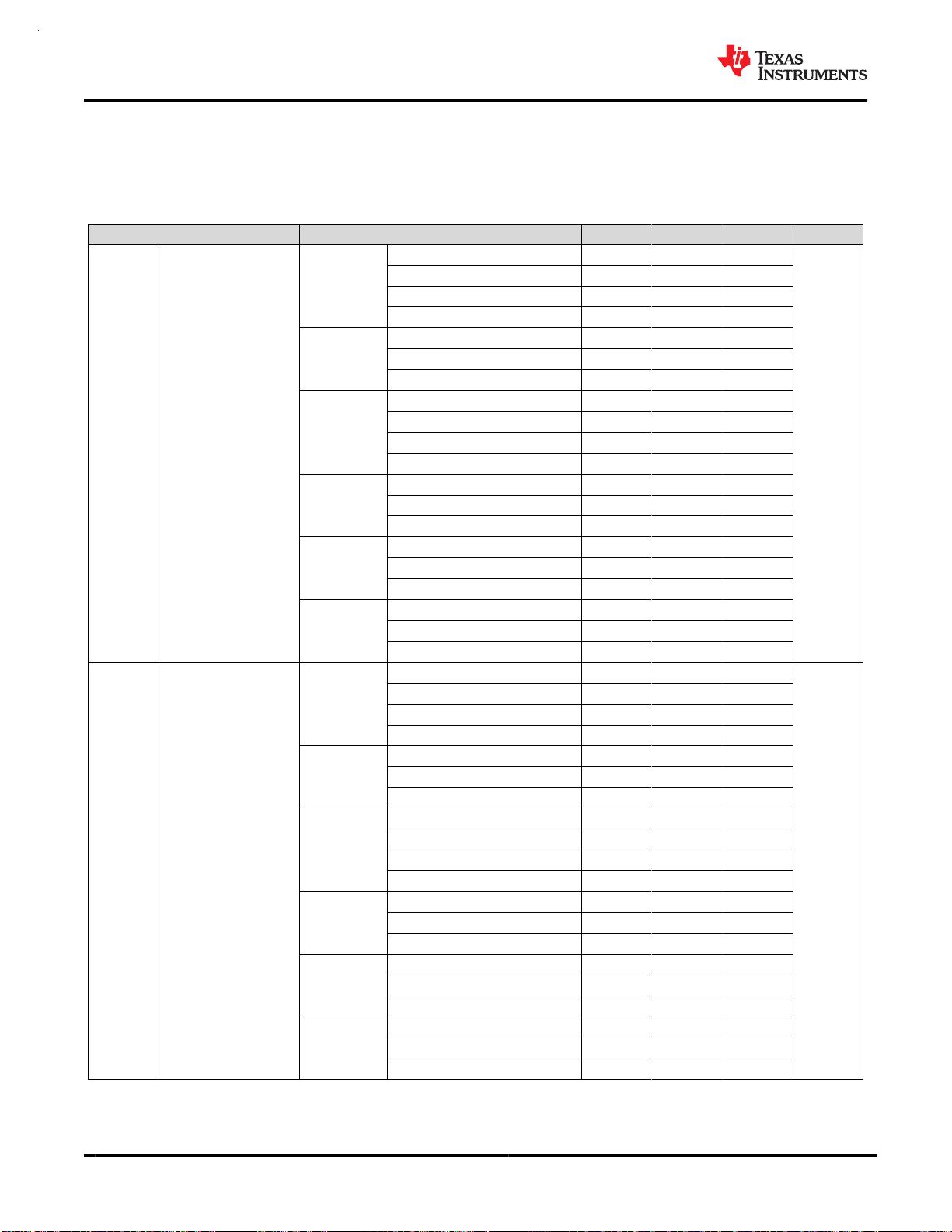

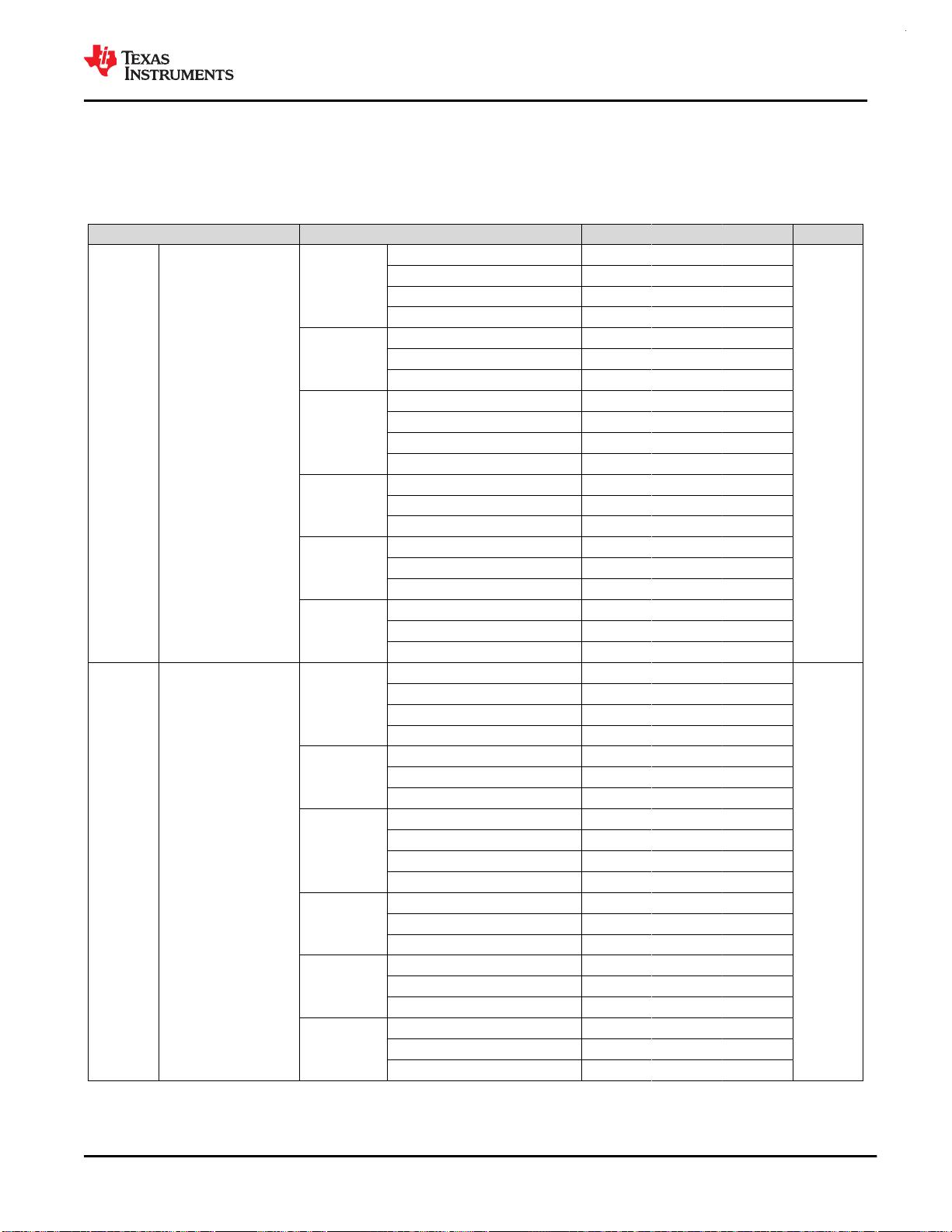

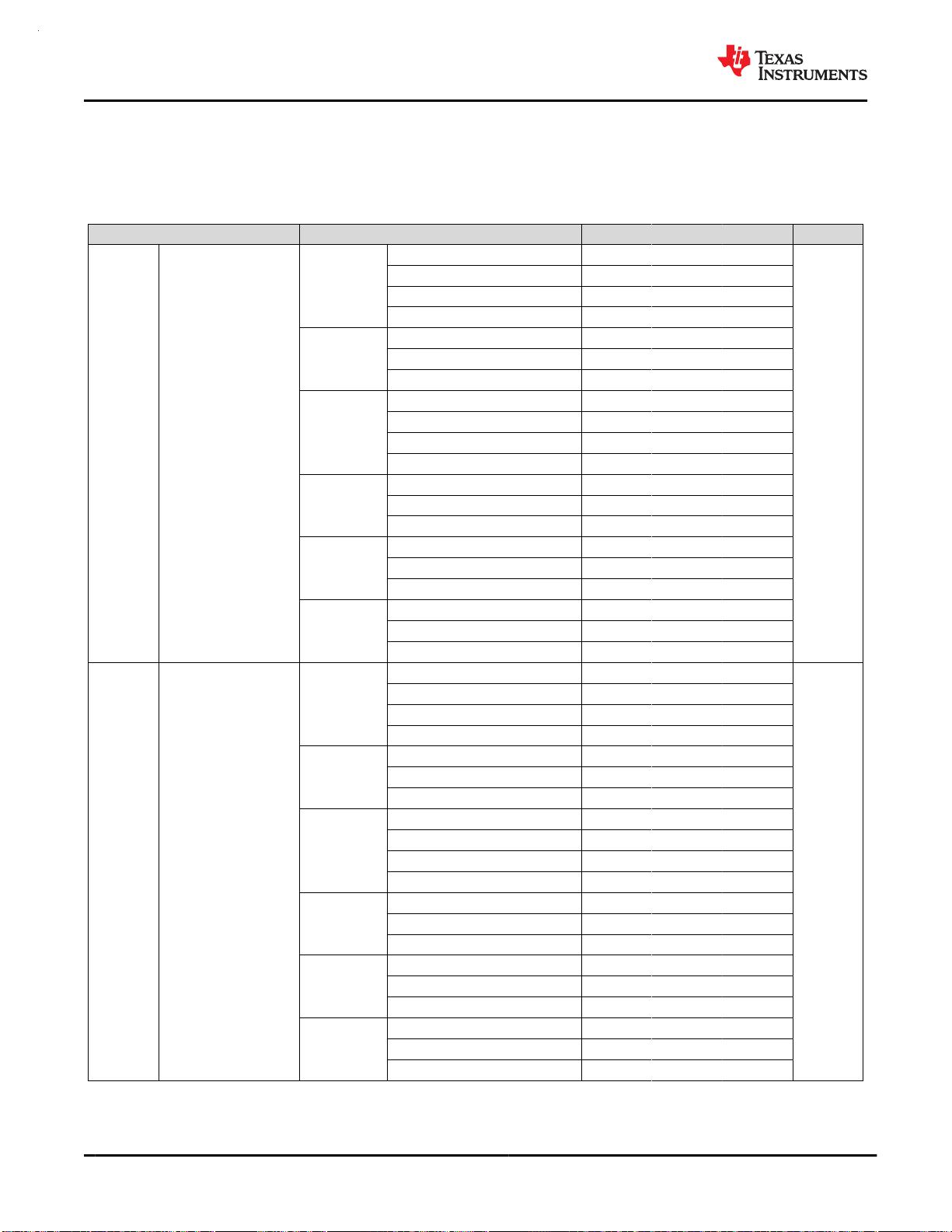

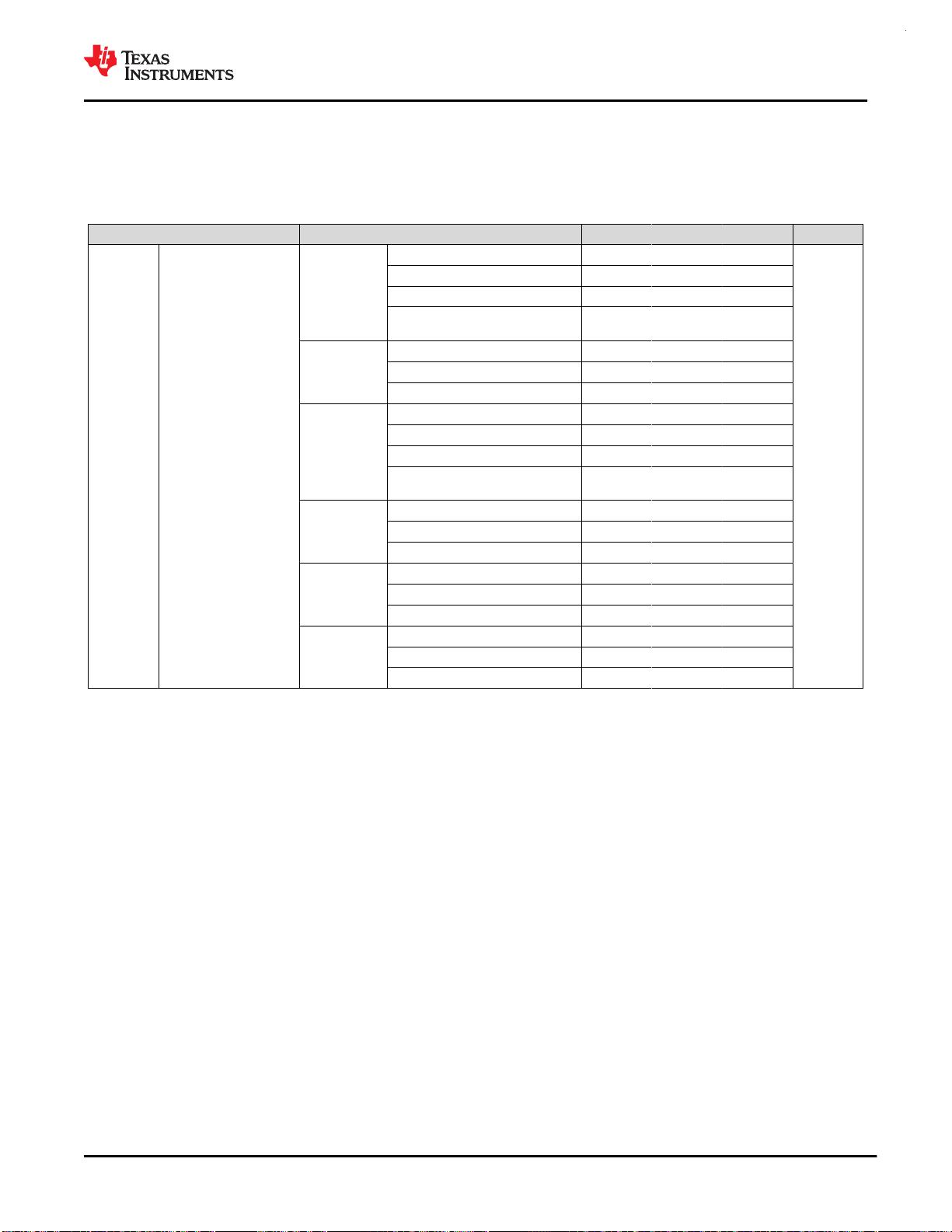

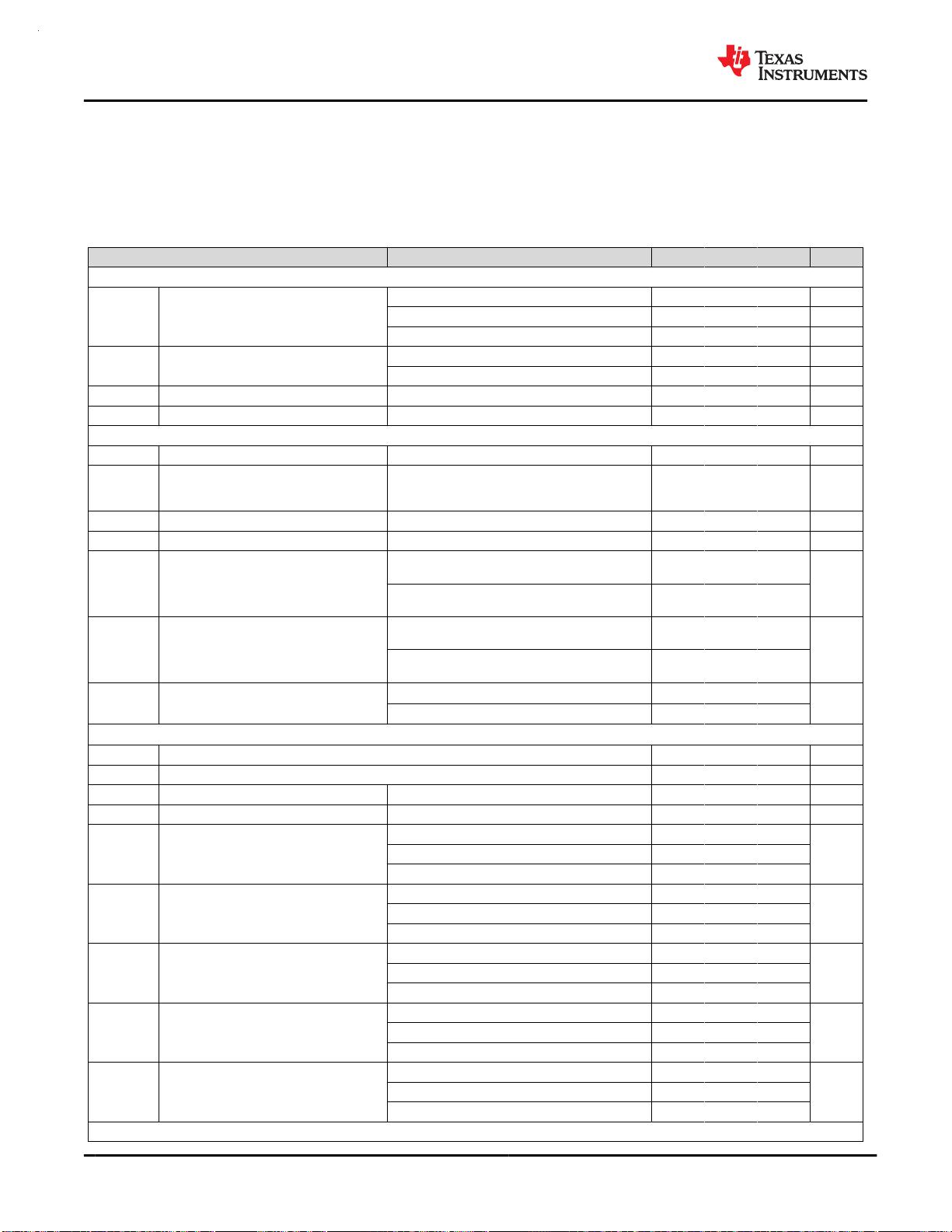

7.7 Switching Characteristics

typical values at T

J

= 25°C, VA19 = 1.9 V, VPLL19 = 1.9 V, VREFO = 1.9 V, VTRIG = 1.1V, VA11 = 1.1 V, VD11 = 1.1 V,

default full-scale voltage (V

FS

= 0.8 V

PP

), f

IN

= 97 MHz, A

IN

= –1 dBFS, f

CLK

= 1.6 GHz, filtered 1-V

PP

sine-wave clock

applied to CLK±, PLL disabled, JMODE = 0, High Performance Mode and foreground calibration, SER_PE = 4 (unless

otherwise noted); VA11Q and VCLK11 noise suppression on when CPLL on; minimum and maximum values are at nominal

supply voltages and over the operating junction temperature range provided in the Recommended Operating Conditions

table

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

ADC SAMPLING CLOCK

t

AD

Sampling (aperture) delay from the clock

falling edge to sampling instant

PLL disabled, CLK± 305 ps

PLL enabled, CLK± 314 ps

PLL enabled, SE_CLK 332 ps

t

AJ

Aperture jitter, rms

Dither disabled (ADC_DITH_EN = 0) 50 fs

Dither enabled (ADC_DITH_EN = 1) 60 fs

t

J(PLL)

PLL additive jitter, rms PLL enabled (PLL_EN = 1), f

PLLREF

= 50 MHz 358 fs

t

J(PLL)

PLL additive jitter, rms PLL enabled (PLL_EN = 1), f

PLLREF

= 200 MHz 340 fs

CLOCK AND TRIGGER OUTPUTS (PLLREFO±, TRIGOUT±, ORC, ORD)

f

PLLREFO

PLLREFO± frequency range PLL Enabled, PLLREFO± enabled 50 500 MHz

f

DIVREFO

ORC and ORD frequency range when

programmed to output divided PLL reference

clock

PLL Enabled, DIVREF_C_MODE > 0,

DIVREF_D_MODE > 0

12.5 100 MHz

t

PW(TRIGOUT)

Minimum TRIGOUT± pulse width TRIGOUT_SRC = 0 (TMSTP±) 1 t

CLK

f

TRIGOUT

TRIGOUT± frequency range TRIGOUT_SRC = 1 (S-PLL) 800 MHz

t

PD(REF)

Input clock to PLLREFO± propagation delay

PLLREF_SE = 0 (CLK± used), nominal supply

voltage, T

A

= 25°C

280 359 440

ps

PLLREF_SE = 1 (SE_CLK used), nominal supply

voltage, T

A

= 25°C

380 469 560

t

PD-TEMPCO

Input clock to PLLREFO± propagation delay

temperature coefficient

PLLREF_SE = 0 (CLK± used), nominal supply

voltage

250 330 420

fs/°C

PLLREF_SE = 1 (SE_CLK used), nominal supply

voltage

280 365 450

t

PD-VOLTCO

Input clock to PLLREFO± propagation delay

supply voltage coefficient

PLLREF_SE = 0 (CLK± used), T

A

= 25°C

–533 –397 –186

fs/mV

PLLREF_SE = 1 (SE_CLK used), T

A

= 25°C

–480 –372 –180

SERIAL DATA OUTPUTS (D[7:0]+, D[7:0]–)

f

SERDES

Serialized output bit rate 2.5 17.16 Gbps

UI Serialized output unit interval 58.3 400 ps

t

TLH

Low-to-high transition time (differential) 20% to 80%, 8H8L test pattern, 16.5 Gbps 28 ps

t

THL

High-to-low transition time (differential) 20% to 80%, 8H8L test pattern, 16.5 Gbps 28 ps

DDJ Data dependent jitter, peak-to-peak

PRBS-7 test pattern, JMODE = 0, 12.8 Gbps 8.56

psPRBS-9 test pattern, JMODE = 4, 16.5 Gbps 6.9

PRBS-9 test pattern, JMODE = 8, 17.16 Gbps 9.28

DCD Even-odd jitter, peak-to-peak

PRBS-7 test pattern, JMODE = 0, 12.8 Gbps 0.2

psPRBS-9 test pattern, JMODE = 4, 16.5 Gbps 0.01

PRBS-9 test pattern, JMODE = 8, 17.16 Gbps 0.05

EBUJ

Effective bounded uncorrelated jitter, peak-to-

peak

PRBS-7 test pattern, JMODE = 0, 12.8 Gbps 1.63

psPRBS-9 test pattern, JMODE = 4, 16.5 Gbps 0.85

PRBS-9 test pattern, JMODE = 8, 17.16 Gbps 3.12

RJ Unbounded random jitter, RMS

8H8L test pattern, JMODE = 0, 12.8 Gbps 0.88

ps8H8L test pattern, JMODE = 4, 16.5 Gbps 0.72

8H8L test pattern, JMODE = 8, 17.16 Gbps 1

TJ

Total jitter, peak-to-peak, with unbounded

random jitter portion defined with respect to a

BER = 1e-15 (Q = 7.94)

PRBS-7 test pattern, JMODE = 0, 12.8 Gbps 21.35

psPRBS-9 test pattern, JMODE = 4, 16.5 Gbps 18.01

PRBS-9 test pattern, JMODE = 8, 17.16 Gbps 23.78

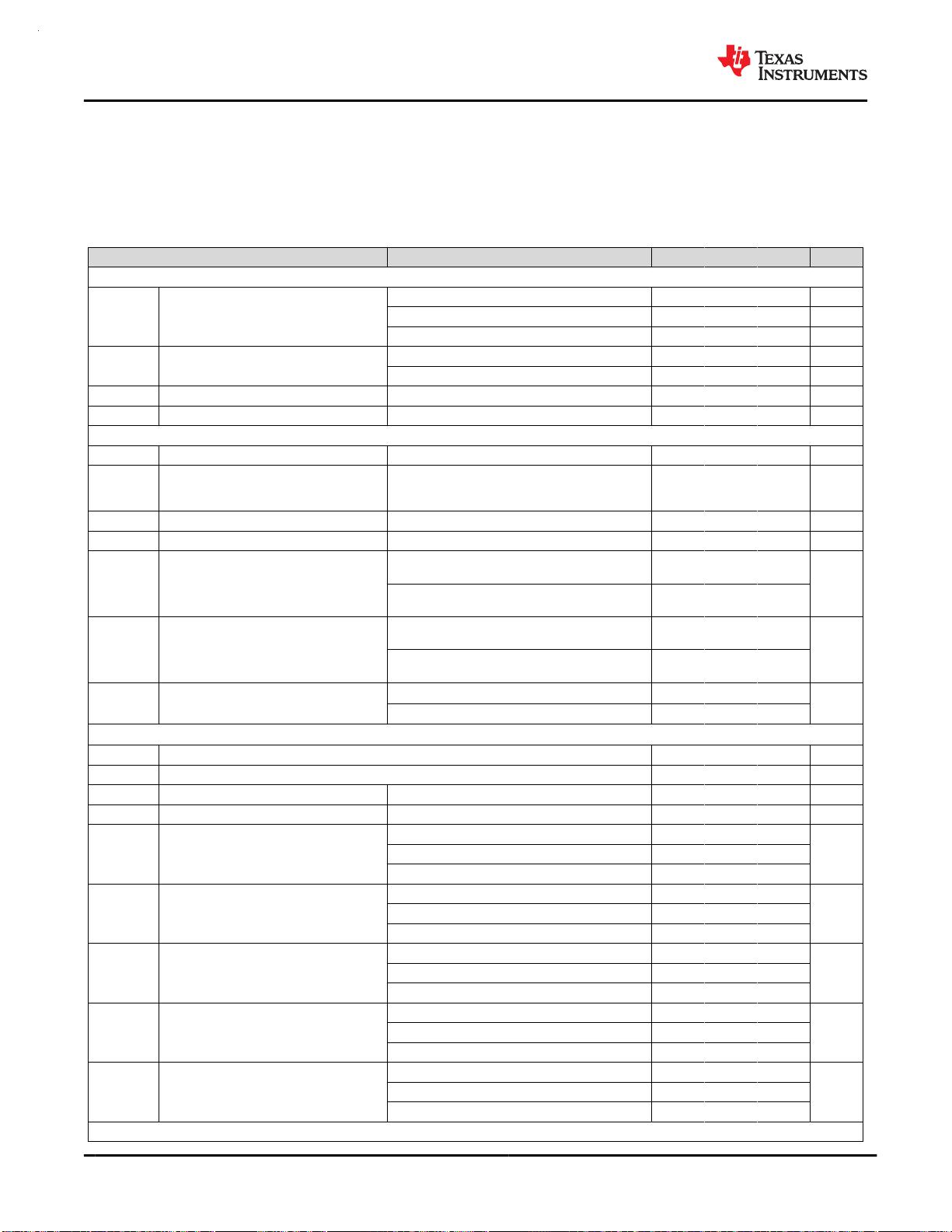

ADC CORE LATENCY

ADC12QJ1600-EP

ZHCSPX2 – JUNE 2022

www.ti.com.cn

20 Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: ADC12QJ1600-EP