FPGA时序约束解析:从问题到解决方案

173 浏览量

更新于2024-06-19

2

收藏 4MB PDF 举报

"小梅哥FPGA时序约束笔记.pdf,主要讲述FPGA开发中的时序分析和时序约束,通过实例解析时序问题对设计稳定性的影响,并探讨如何解决这些问题。"

在FPGA开发中,时序约束是至关重要的,它直接影响着设计的性能和稳定性。时序分析涉及到信号在系统内的传输时间,包括组合逻辑路径延迟和时钟周期内的延迟,确保数据能在正确的时间到达目的地,避免数据错乱和系统不稳定。

文中提到了几个实例来阐述时序问题的影响。首先,作者提到在设计一个基于CY7C68013的USB传输模块时,由于时序不匹配,导致在不同硬件平台上通信出现数据误码。这可能是由于时钟同步、信号传输延迟或者逻辑设计不当造成的。解决此类问题通常需要深入理解FPGA内部的工作机制,进行精确的时序约束,确保在所有目标平台上的一致性。

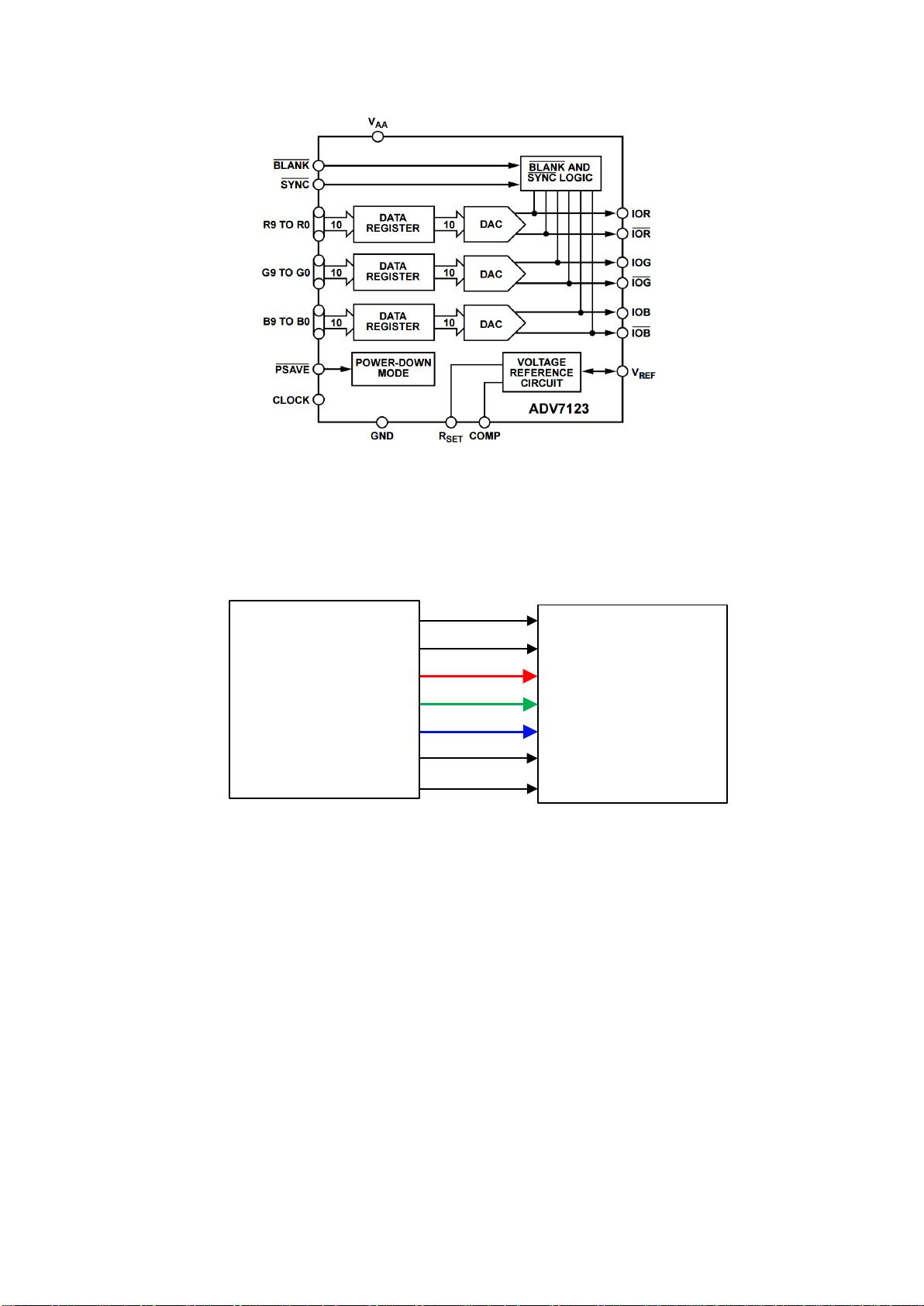

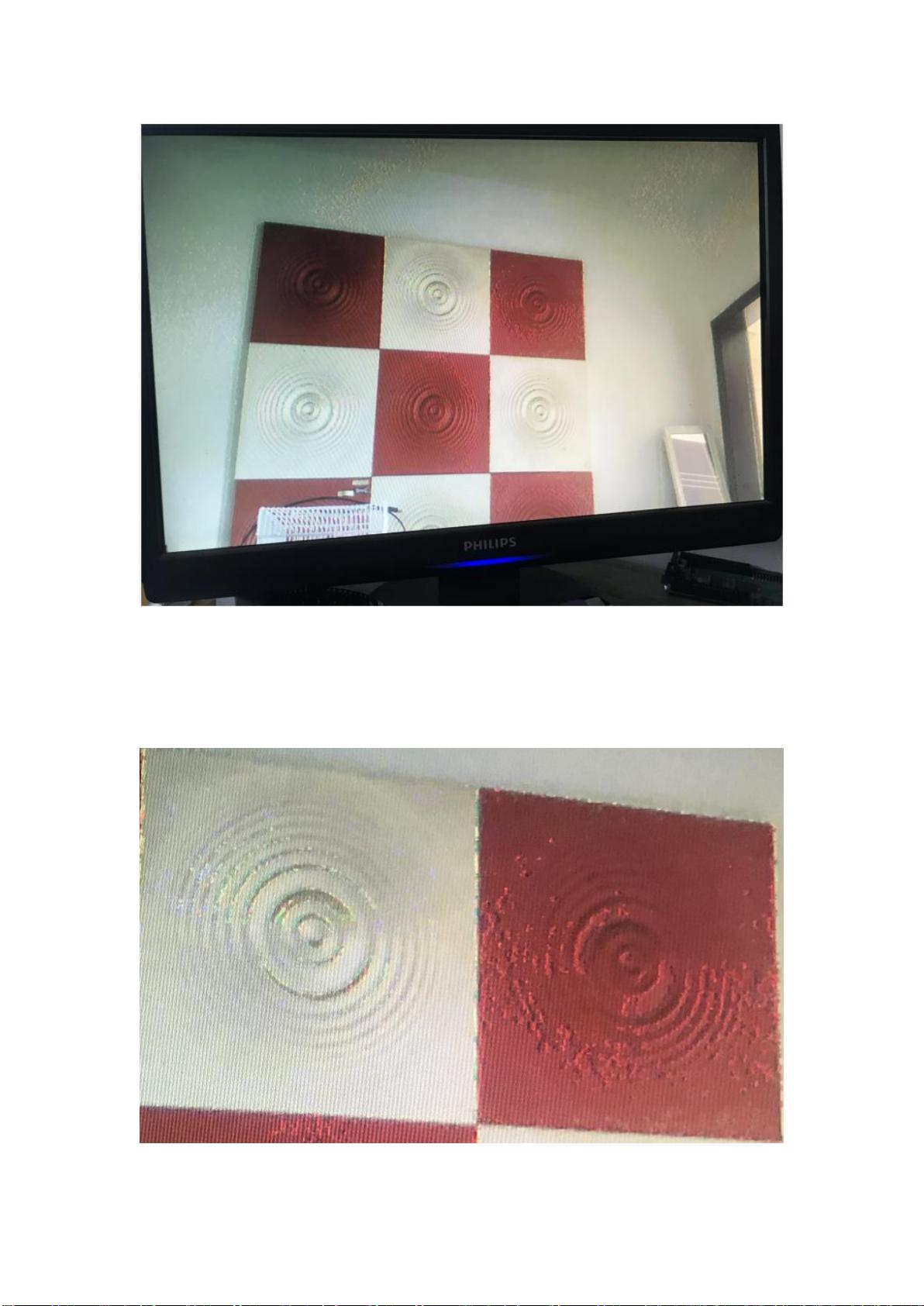

其次,作者在使用ADV7123进行数字RGB到模拟VGA转换时,发现有时需要对时钟信号取反才能正常工作。这是因为不同设备之间的时序容差,以及对时钟边沿敏感性的差异。解决此类问题需要细致地调整时序参数,甚至可能需要引入额外的逻辑处理来适应不同的硬件。

时序约束是解决这些问题的关键。它涉及到对FPGA设计中各个模块和路径设置特定的延迟限制,确保满足系统时钟周期的要求。在Xilinx的Vivado或Intel的Quartus等工具中,开发者可以使用各种时序约束语法(如UCD92XX系列的约束文件)来指定输入输出的延迟、建立时间、保持时间和时钟偏移等。

学习FPGA开发时,理解并掌握时序约束不仅能提升设计效率,还能确保设计的可靠性。初学者应该首先了解基本的时序概念,如时钟周期、最大延迟路径和最小建立时间。然后,通过实践项目,逐步熟悉如何在实际设计中应用这些概念,如设置正确的输入输出约束,优化逻辑路径,以及处理时钟域间的同步问题。

此外,时序收敛是FPGA设计流程中的一个重要环节,确保设计在满足速度要求的同时还能成功编译。这可能需要反复迭代,调整逻辑结构,优化布线,甚至使用时序预测技术来预估优化效果。

FPGA时序分析与约束是开发者必须掌握的核心技能之一。通过理论学习与实际案例相结合,可以逐步提高对时序问题的洞察力和解决能力,从而提高设计的稳定性和性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-04-09 上传

2023-12-05 上传

2023-09-09 上传

2023-10-18 上传

SKCQTGZX

- 粉丝: 128

- 资源: 4767

最新资源

- dmfont:DM-Font的PyTorch正式实施(ECCV 2020)

- 像素艺术制作者:使用JQuery创建像素艺术的网站

- Graphics:Visual Studio 2019入门项目

- map_viewing_program.rar_GIS编程_C#_

- curso_html5_css3:网站barbararia Alura,当前HTML5和CSS3的完整版本

- matlab心线代码-cpmodel-jap:心肺模型-JAP2020-Karamolegkos,Albanese,Chbat

- FCC-Responsive-Web-Design

- UrFU:实验室工作,项目和其他与研究相关的

- PRS:多程序计算机的仿真模型

- 适用于iOS的Product Hunt徽章-Swift开发

- Azure_devop_IaC-Terraform:使用Terraform创建应用IaC概念的Azure AppService

- sift.rar_matlab例程_matlab_

- Symfony_Voitures:CRUD固定装置和Faker

- Home alarm-开源

- Project_Hybrid_VotingApp

- EMS For Google Calendar-crx插件