FPGA应用开发实验指南:从基础到SOPC系统

版权申诉

200 浏览量

更新于2024-06-26

收藏 9.25MB PDF 举报

"FPGA应用开发实验指导书-学生版本new.pdf"

这是一份针对FPGA(Field-Programmable Gate Array,现场可编程门阵列)应用开发的实验指导书,适合学生学习使用。书中详细介绍了多个实验,涵盖了从基础的Quartus II软件操作到复杂的SOPC(System on a Programmable Chip,可编程片上系统)系统开发。以下是各实验的核心知识点:

**实验一:Quartus软件操作**

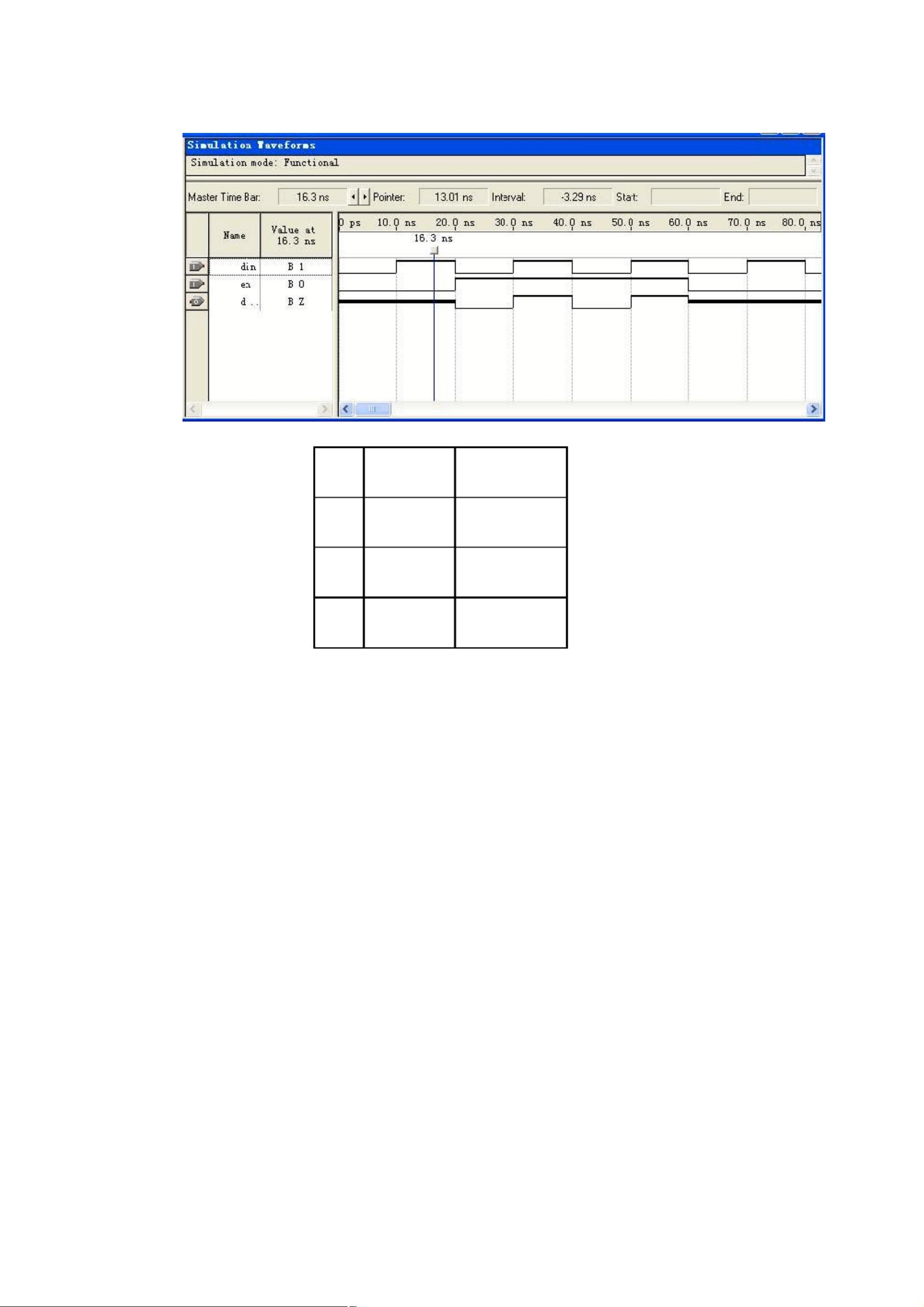

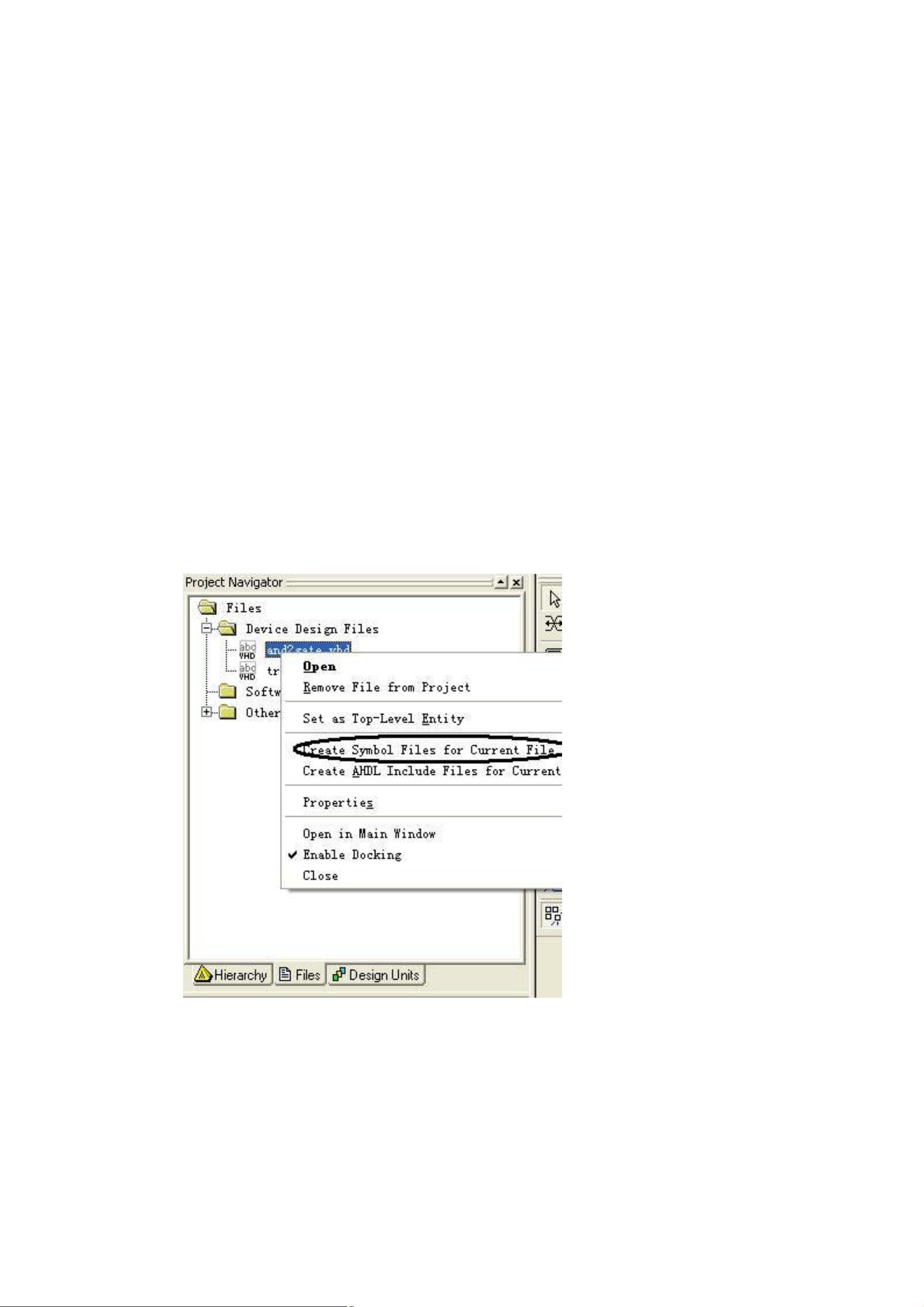

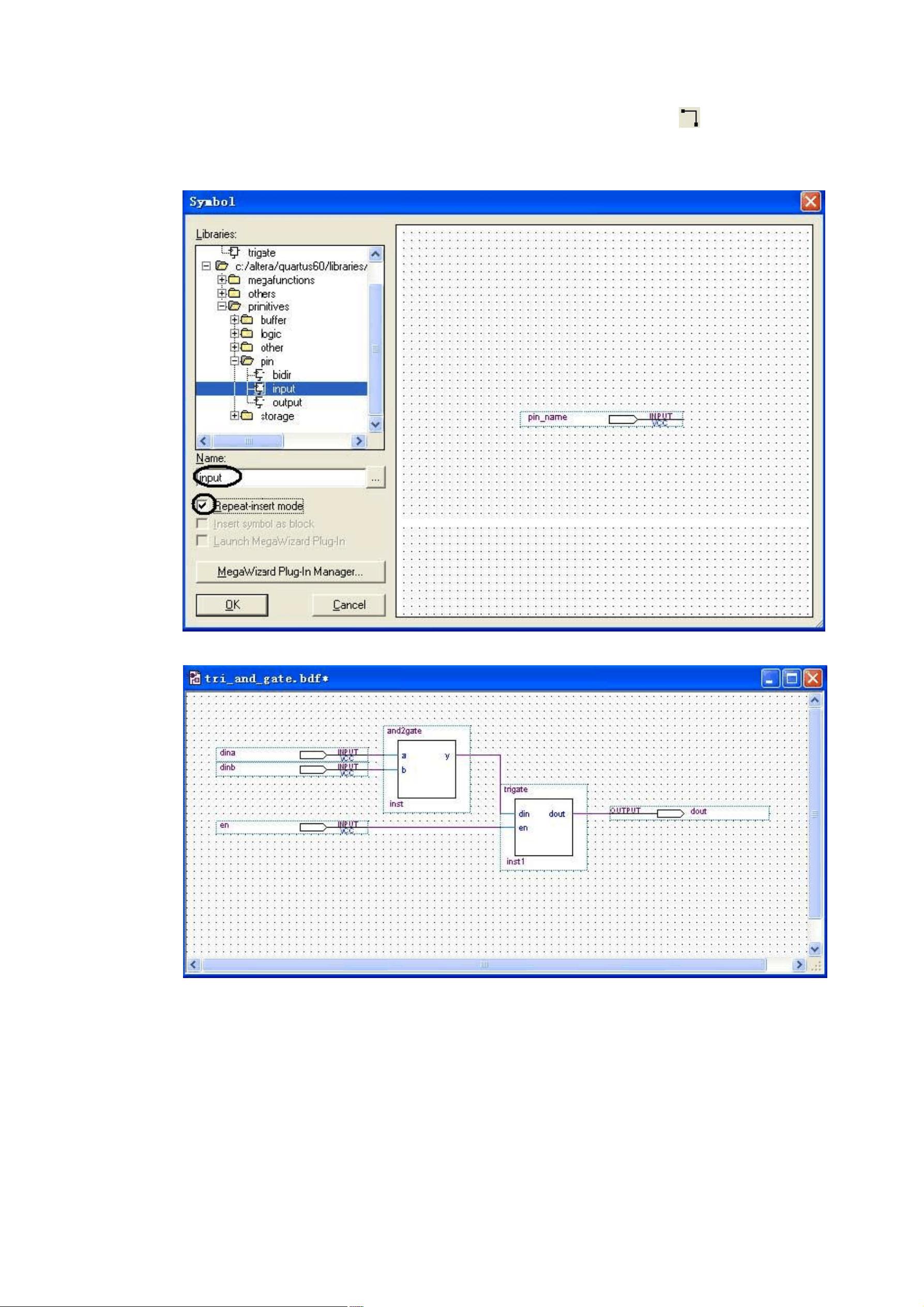

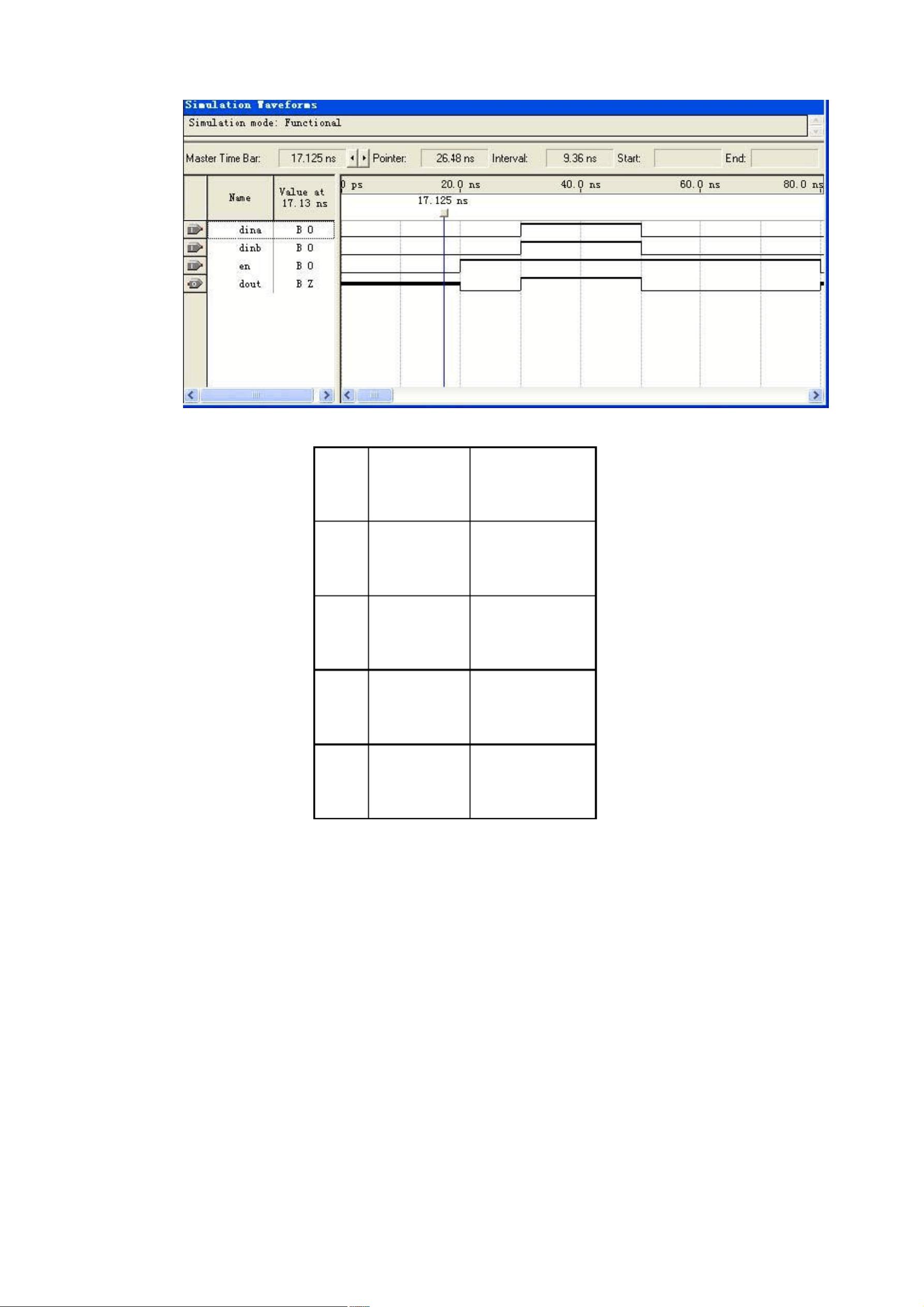

1. **QuartusII的文本编辑输入法**:学习如何使用Quartus II进行文本编辑,即基于硬件描述语言(如VHDL或Verilog)编写设计代码。

2. **QuartusII的图形编辑输入法**:介绍通过图形界面设计电路的方法,包括原理图捕获和状态机编辑。

**实验二:简单的组合逻辑电路设计**

1. **四舍五入判别电路**:设计一个电路用于处理数字的四舍五入操作。

2. **控灯电路**:控制LED灯的亮灭,理解基本的逻辑门和组合逻辑。

3. **优先权排队电路**:实现不同输入信号的优先级判断。

**实验三:显示译码电路**

1. **数字循环显示**:设计电路实现数字的循环滚动显示。

2. **字母循环显示电路**:扩展到字母的显示,涉及字符编码和译码。

**实验四:BCD码加法电路**

1. **二进制码到BCD码的转换**:学习二进制到BCD(Binary-Coded Decimal,二进制编码的十进制)的转换逻辑。

2. **1位BCD加法器**:构建一个能处理BCD码的加法运算单元。

3. **2位BCD加法器**:进一步扩展到两数的BCD加法。

**实验五:分频器**

1. **偶数倍分频**:设计分频电路,使输出频率为输入频率的偶数倍。

2. **奇数倍分频**:实现分频为输入频率的奇数倍。

3. **嵌入式锁相环宏功能模块的使用**:利用锁相环技术实现高精度分频。

**实验六:触发器与计数器**

1. **触发器功能的模拟实现**:理解和使用不同类型的触发器(如D触发器、JK触发器等)。

2. **计数器**:设计各种计数模式(如二进制、十进制、模N计数器)的电路。

3. **时钟电路**:理解时钟信号在数字系统中的重要性并设计时钟分发电路。

**实验七:存储器的设计**

1. **用LPM实现32×8RAM**:使用LPM(Logic Macro Cell,逻辑宏单元)库创建固定大小的RAM。

2. **用VHDL实现**:用硬件描述语言VHDL自定义RAM结构。

3. **用片外RAM实现**:连接外部SRAM或DRAM,扩展FPGA内部存储能力。

4. **SRAM的应用**:探讨静态RAM(SRAM)在高速缓存或其他需要快速访问的应用场景。

**实验八:波形发生器设计**

1. **加入计数器元件**:利用计数器产生不同频率的波形。

2. **建立存储器初值设定文件**:设置存储器的初始值以生成特定波形。

3. **加入只读存储器ROM元件**:使用ROM存储预定义的波形数据。

4. **编辑和编译顶层设计文件**:完成整个系统的设计和验证。

**实验九:交通灯设计**

1. **设计原理**:基于现实世界交通规则设计红绿灯控制器。

2. **部分程序**:展示部分关键代码实现。

3. **具体设计步骤**:详细说明从需求分析到实现的步骤。

**实验十:基于DE2的SOPC系统开发**

1. **建立一个新的SOPC系统**:在FPGA中构建嵌入式处理器系统。

2. **在SOPCBuilder中定义目标系统**:配置处理器、外设和总线架构。

3. **分配基地址和中断请求优先级**:管理硬件资源的地址空间和中断处理。

4. **显示外设的连接关系**:可视化系统组件间的连接。

5. **指定其他的NiosII设定**:优化Nios II嵌入式处理器的配置。

6. **生成SOPCBuilder目标系统**:完成系统集成并生成配置文件。

7. **将目标集成到Quartus项目中**:将SOPC系统整合到Quartus工程中。

8. **下载硬件设计到目标FPGA**:通过JTAG接口下载设计到DE2开发板上的FPGA。

9. **使用NiosII IDE开发软件**:编写和调试运行在Nios II处理器上的软件。

这份实验指导书全面地覆盖了FPGA开发的各个方面,从基础的逻辑电路设计到复杂的嵌入式系统构建,是学习FPGA技术的宝贵资料。通过这些实验,学生能够掌握FPGA开发的基本流程,提升硬件描述语言编程技能,并理解数字系统设计的核心概念。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-09-02 上传

2022-01-17 上传

2021-12-15 上传

2010-06-09 上传

2022-11-16 上传

2021-10-05 上传

apple_51426592

- 粉丝: 9838

- 资源: 9652

最新资源

- 非常不错的在线邮件群发系统官方版v1.1

- ng-auth:角度中的简单身份验证受限状态

- 4Coders-MeuCandidatoIdeal:黑客马拉松透明度巴西应用程序

- Memory-Game:原生Android记忆游戏应用

- 心情MTV网站系统官方版 v2.0

- 红警2mix文件加密器

- chasqientrega:https

- 广告牌彩灯闪烁控制程序+设计说明.rar

- frontend-boilerplate

- aspectjs:aspectjs切面编程

- mail-bot:基于条件的邮件机器人

- Hotel_website:CSS中的基本酒店网站

- 手机九宫格html5网站模板

- 水国类数据集(CV专用)

- 中国城市区域数据.zip

- ASOFI3D_时域各向异性地震建模_c语言_地震建模_时域_各向异性_ASOFI3D_建模_地震_3D